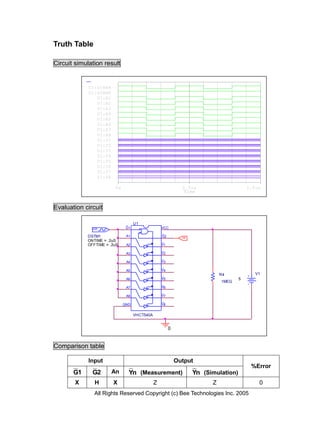

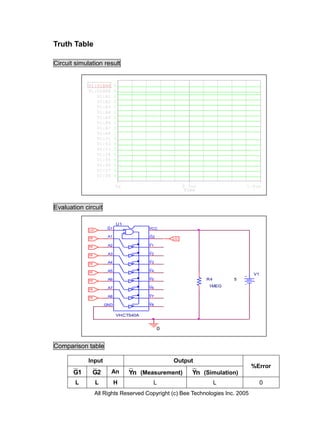

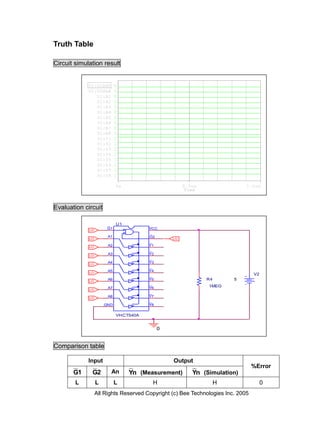

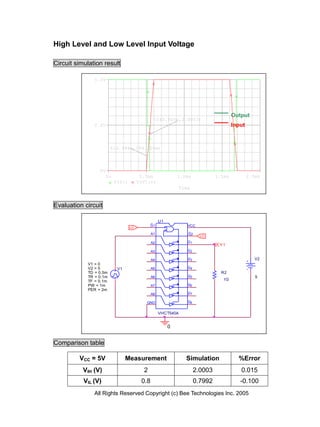

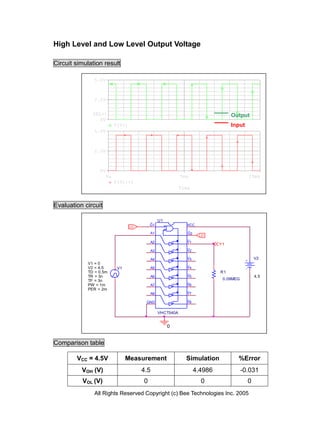

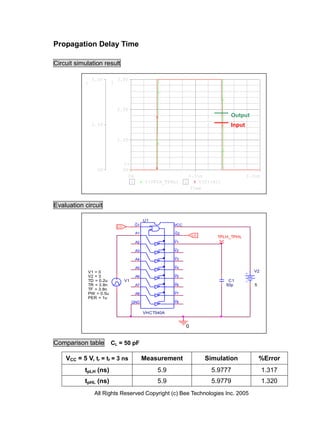

The document outlines the device modeling report for the TC74VHCT540A CMOS digital integrated circuit from Toshiba. It includes various circuit simulation results, comparisons between measurements and simulations, such as truth tables, propagation delay times, and output enable/disable times. The report highlights performance metrics such as voltage levels and errors in simulation predictions.