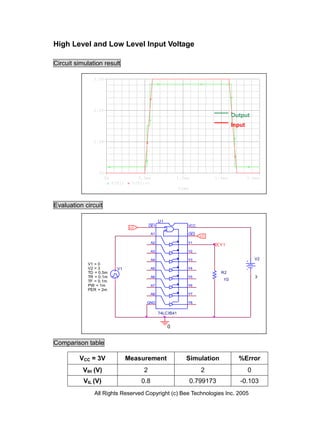

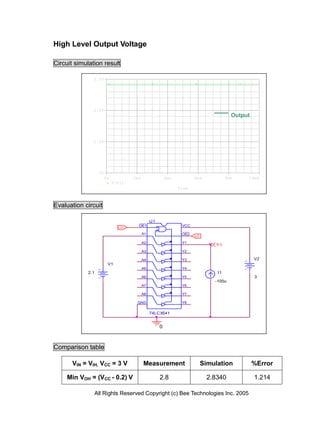

The document is a device modeling report for the CMOS digital integrated circuit TC74LCX541FW, manufactured by Toshiba Bee Technologies Inc. It includes truth tables, circuit simulation results, and performance comparisons related to input/output characteristics, propagation delay, and output enable/disable times. The report provides detailed measurements and simulations, highlighting errors in output and timing under various conditions.