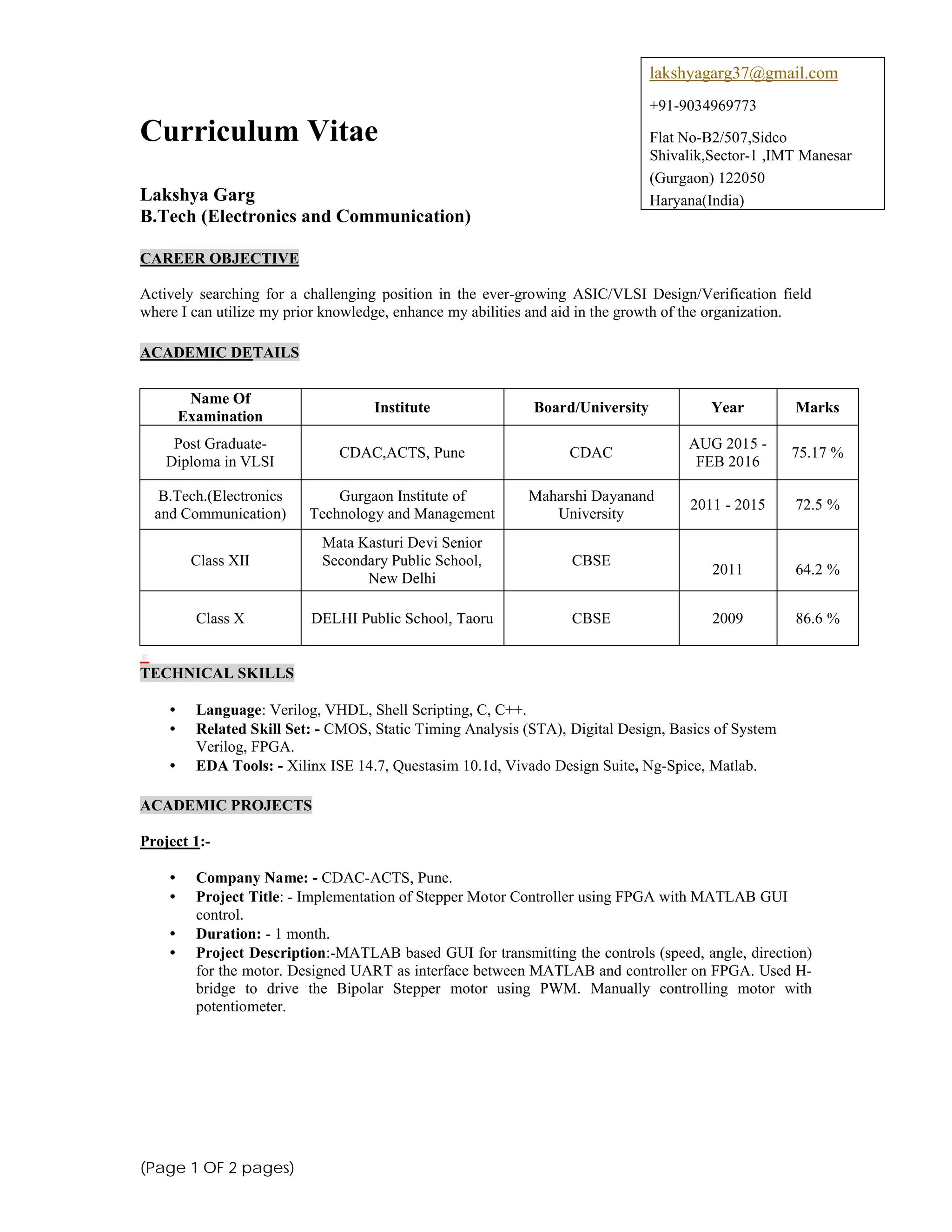

Lakshya Garg's curriculum vitae summarizes his educational and professional background. He holds a B.Tech in Electronics and Communication and a post-graduate diploma in VLSI. His technical skills include Verilog, VHDL, C, C++, and EDA tools like Xilinx ISE and Vivado. He has worked on academic projects implementing a stepper motor controller with FPGA and MATLAB GUI, a basic UART design, and a traffic light controller. He was involved in leadership roles in student organizations and technical events and participated in robotics competitions during his time as a student.