resume

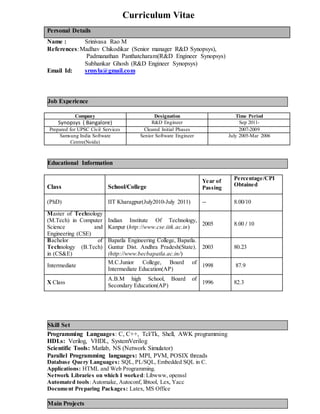

- 1. Curriculum Vitae Personal Details Name : Srinivasa Rao M References:Madhav Chikodikar (Senior manager R&D Synopsys), Padmanathan Panthatcharam(R&D Engineer Synopsys) Subhankar Ghosh (R&D Engineer Synopsys) Email Id: srmyla@gmail.com Company Designation Time Period Synopsys ( Bangalore) R&D Engineer Sep 2011- Prepared for UPSC Civil Services Cleared Initial Phases 2007-2009 Samsung India Software Centre(Noida) Senior Software Engineer July 2005-Mar 2006 Class School/College Year of Passing Percentage/CPI Obtained (PhD) IIT Kharagpur(July2010-July 2011) -- 8.00/10 Master of Technology (M.Tech) in Computer Science and Engineering (CSE) Indian Institute Of Technology, Kanpur (http://www.cse.iitk.ac.in) 2005 8.00 / 10 Bachelor of Technology (B.Tech) in (CS&E) Bapatla Engineering College, Bapatla. Guntur Dist. Andhra Pradesh(State). (http://www.becbapatla.ac.in/) 2003 80.23 Intermediate M.C.Junior College, Board of Intermediate Education(AP) 1998 87.9 X Class A.B.M high School, Board of Secondary Education(AP) 1996 82.3 Programming Languages: C, C++, Tcl/Tk, Shell, AWK programming HDLs: Verilog, VHDL, SystemVerilog Scientific Tools: Matlab, NS (Network Simulator) Parallel Programming languages: MPI, PVM, POSIX threads Database Query Languages: SQL, PL/SQL, Embedded SQL in C. Applications: HTML and Web Programming. Network Libraries on which I worked: Libwww, openssl Automated tools: Automake, Autoconf, libtool, Lex, Yacc Document Preparing Packages: Latex, MS Office Job Experience Educational Information Skill Set Main Projects

- 2. Distributed SLP writer: o Programming Language: C o Duration, Company: 6 months, Syopsys o Role: Main developer This is currently ongoing project. Currently for writing the slp writer we are loading the whole netlist of the design. This is consuming lot of memory and makes run time very slow. In this project we load netlist only partially and load modules on demand using skeleton netlist. Adding initial value support for registers and memories in slp writer, vm writer o Programming Language: C o Duration, Company:1 month, Synopsys o Role: Main Developer In 1403 release slp writer is not forward annotating initial values for registers and memories. Without it may cause simulation failures and logic bugs. In this project we tried to handle that. Making slp writer output System Verilog compatible and implemented rotl,rotr rtl models o Programming Language:C o Duration, Company:3 months, Synopsys o Role: Main Developer In this project we made the slp writer output system Verilog compliant. That means the Verilog code written by slp writer is a valid system Verilog code as well. Like there will be no system Verilog keywords in any module ports and the Verilog written is a legal system Verilog as well. In this project we implemented rtl models for rotate left and rotate right operators. Using System Verilog constructs force/bind to reduce number of modified modules o Programming Language:C,Verilog o Duration, Company:3 months, Synopsys o Role: Main Developer When a module has to be machine generated due to various reasons like partition, complex ports then we have to machine generate all the modules above that module in the hierarchy. This increases number of modified modules. If we use force/bind constructs of system Verilog then we can prevent machine generation of whole hierarchy. In this project we have implemented it which is yet to be productized. Automatic VCS Script generation for post partition netlist simulation for Certify/Protocompiler o Programming Language:C,Verilog o Duration, Company:3 months, Synopsys o Role:Main Developer After partition all most all designs are simulated to verify their functional correctness. The most popular tool for simulation is VCS. As part of slp generation stage itself, we will create a vcs script sothat user has no need to write a vcs script can make changes to the Automatic generated vcs script. Writing One module per file for SLP writer for Certify/Protocompiler o Programming Language:C,Verilog o Duration, Company:3 months, synopsys o Role: Main Developer Till 2014.03 release all machine generated modules are being written in a single file. This has some disadvantages/limitations like if the machine generated modules has more than one encryption then we cannot open the file in more than one encrypted form. And if the user wanted to ignore some modified modules, he has to explicitly delete them. On the other hand, if the module is generated per file we can open the file in the specific encryption form of the module and if the user does not want some modules then he can simply do not add the corresponding files in the fpga mixed project.

- 3. Supporting System Verilog multidimensional ports(2d ports) in SLP Writer for Certify/Protocompiler o Programming Language: C,System Verilog o Duration, Company:3 months, Synopsys. o Role: Main Developer Certify and Protocompiler are prototyping multi fpga tools. After the design has been partitioned, some modules get modified due to partition, failed to uniquify or modules having ports with keyword names and some other reasons. Till 1403, If the module is system Verilog and it has complex ports like two dimensional ports, we are machine generating that module. If a module has been machine generated then modules in the upper level hierarchy are also machine generated. This increases number of modified modules. The less the number of modified modules, the better it can be easily simulated. As part of reducing total modified modules, we are reusing original module with complex ports instead of machine generating it. As part of this the generated file is system Verilog and no longer a Verilog one. Rtl-ilm model creation for Automatic Compile Point flow and running top module as a separate Compile Point for Synplify: o Programming Language: C, Posix Threads, Verilog/VHDL o Platform: Linux o Duration, Company: 6 months, Synopsys o Role: Main Developer Compile Point flow is used to synthesize designs in parallel. Automatic compile point flow is used to automatically select module with enough logic and to run them in parallel. There was dependency between the compile points (Only after all child compile points are mapped we should map its parent using mapped timing models of child CPs). This project is aimed at removing dependency using rtl level timing model. In addition to this we have successfully mapped top module as a separate compile point. This will allow compile points can be run even across machines. Currently this flow is being applied to Xilinx, Altera, Microsemi mappers. Read/Write Check Collision Logic for Write first RAM for Synplify: o Programming Language: C, Xml, Verilog/VHDL o Platform: Windows o Duration, Company : 3 months (Synopsys), Main Developer o This is project is to develop UI switch so that if the user is sure that in his design there will be no read/write collision, he can set the switch off. If there is a collision he can set the switch on so that bypass logic will be built around the inferred RAM. This is implemented for all FPGA technologies (Xilinx, Altera,..). Handling Initial values for RAM when it decomposed into registers for Synplify: o Programming Language: C, Verilog/VHDL o Platform: Windows o Duration, Company : 3 months (Synopsys), Main Developer o When the RAM module is being decomposed into registers either explicitly set by user or if the RAM cannot be inferred due to some other reason then the initial values set on the RAM should be propagated to the corresponding fragmented registers. Honoring initial values is very important for high reliability designs. This project is aimed at honoring initial values for RAM when decomposed into registers. Issues on Automatic Compile Point Flow for Synplify: o Programming Language: C with posix threads, Verilog/VHDL o Tools : gdb,vs2010 o Platform: Windows/ Linux

- 4. o Duration, Company : 3 months (Synopsys), Co-Developer (team of 3) o In this ongoing project, I have handled some issues like pushing tristate to top, Honoring syn_probe attribute, resolving multiple CPs with same Name etc. IHD Browser for HDDVD Player: o Programming Language: C with POSIX threads ,C++ o Libraries: libwww, openssl o Tools: Automake, Autoconf, libtool o Document Preparing Package: Latex o Duration, Company : 6 months (Samsung), owner of network module o Platform: Linux o This project is to develop a high definition browser for HD DVD Player. I handled Network Module. The function of Network layer is to take request from FCM(File Cache Manager) for downloading and connects to the network to download and Present the data to FCM. It also gets request from Programming Engine (Script Module) through APIs. Important sub modules implemented in this project are Disc Authentication Connecting using SSL when the protocol is https Server Authentication Cookies and CA certificate Management Data Streaming and Compete Downloading Developing APIs to be used by script module Used libwww as a main library and the openssl for the support of https and Server Authentication Demultiplexing Transport stream for HDTV for simultaneous display of channels on different windows o Programming Language: C and OpenGL o Codecs: MPEG4,MP3,WAV o Platform: Linux o Document Preparing Package: Latex o Duration, Company : 6 months (Samsung), co-developer (team of 5) o This project is to demultiplex transport stream of TV cable network in real time and displaying various channels simultaneously on different windows using open GL. HDTV shows the user selected channel. MTech Thesis: BioBIRCH: An Incremental Algorithm for Clustering of ESTs Tools: BLAST, CAP3, Phrap, Phred, TIGR Assembler, Celera Platform: Linux Document Preparing Package: Latex Expressed genes of an organism are not sequenced in single pass due to experimental limitations. Expressed Sequence Tags(ESTs) are subsequences of expressed genes, sequenced in single pass. ESTs are clustered to obtain their parent genes. Whenever ESTs of an expressed gene of an organism are sequenced they are added to the current database of ESTs of that organism. Due to advancements in sequencing machines, databases of ESTs become huge with no upper bound on their size. Clustering of ESTs has become a challenging task because of these huge datasets. Though number of ESTs of an organism does not have an upper bound, total number of genes of an organism is constant. Exploiting this property, we designed and implemented a new incremental algorithm BioBIRCH for clustering of ESTs. To our knowledge this is first such algorithm to cluster ESTs. The novel features of this algorithm are 1) whenever a new dataset is added to the database, instead of clustering updated database from beginning, we emph {merge} new data set with the clusters of old database and cluster this resultant dataset to form new clusters. 2) time and space

- 5. required for clustering become negligible, when compared with traditional techniques. 3) since the number of clusters(genes) is constant for an organism, whatever may be size of the database, this algorithm does not go out of memory which is the biggest problem in clustering. 4) this algorithm avoids all versus all pair wise alignment of ESTs, making it time efficient. Using sequential version of this algorithm, we clustered 31,000 Arabidopsis ESTs in 6 days on Pentium IV 3.6 GHz machine. Dataset of 55,000 ESTs of Arabidopsis thaliana is clustered in 4 days on a parallel machine of 11 Pentium III nodes, with parallel version of this algorithm. The quality of these clusters are good when compared with clusters formed using PaCE. The current state-of-the-art parallel softwares like PaCE and TGICL are not able to run on this data set on the same parallel machine. B.Tech Project: Design and Implementation of subset of ANSI C Compiler Languages: C, Shell, AWK Tools: Lex, Yacc Document Preparing Package: MS Office Platform: Unix In this Project we have taken a subset of C Language and Implemented a Compiler. This compiler takes a program written in C and converts it into an Intermediate language. We used Lex as Lexical analyzer and Yacc as syntax analyzer COURSES TAKEN IN GRADUATION (Core): 1st Year: Numerical Computational Methods, Differential Calculus, Integral Calculus, Probability and Statistics, C Programming. 2nd Year: Digital Logic Design, Discrete Mathematics, Data Structures, Computer Graphics, Electronic Devices & Linear IC’s. 3rd Year: Systems Software, Computer Organization, Automata Theory and Formal Languages, Object Oriented Programming & Systems, Principles of Programming Languages, Microprocessors & Interfacing, System Analysis and Design, Operations Research, Operating Systems. 4th Year: Compiler Design, Database Management Systems, Design & Analysis of Algorithms, Computer Networks, Software Engineering, Distributed Database Systems, Image Processing. COURSES TAKEN IN POST-GRADUATION: 1st Semester: Advanced Computer Networks, Machine Learning and Knowledge Discovery, Mobile Computing, Design and Analysis of Algorithms. 2nd Semester: Computational Complexity, Data Mining, Logic in Computer Science. Cleared PhD comprehensive exam with highest marks at IIT KGP in first semester itself Best Team Player Award 2005-06 presented by Samsung India Software Centre, New Delhi Recipient of Gold Medal for getting first position in GATE-2003( National level Entrance Exam for doing PG in IITs and NITs ) (percentile 99.74, AllIndiaRank-97) among all the B.Tech students in the college in the final year of B.Tech. Recipient of Gold Medal for getting first position in GATE-2002 percentile 99.56, AllIndiaR- ank-83 among all B.Tech students in the college in third year of B.Tech. Courses Scholastic Achievements

- 6. Got 475 rank in EAMCET-98(Region Level Entrance Exam for doing Bachelor Degree in Engineering Conducted by Andhra Pradesh state Government). One in Top 10 of the class throughout my educational career The information given above is true to the best of my knowledge. Srinivasa Rao Myla