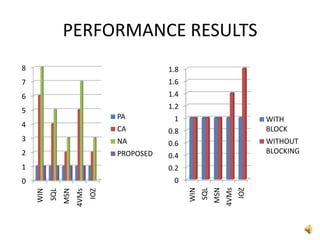

This document provides information on solid state drives (SSDs). It discusses the history and operation of flash memory, how SSDs work compared to hard disk drives, and performance optimizations like parallelism and garbage collection. SSDs have advantages over HDDs like higher data transfer rates, lower power consumption and size, but also challenges like limited write cycles and latency issues. The document evaluates different page placement policies and block repositioning methods to improve SSD response times.

![REFERENCES

• IEEETrans. Comput., vol. 60, no. 6, pp. 753–766, 2011 BY M. L.

Chiao and D.W. Chang.

• H. Shim, B. Seo, J. Kim, and S. Maeng, “An adaptive

partitioning scheme for DRAM-based cache in solid state

drives,” in Proc. IEEE IN NOV 2010

• R. McDougall and J. Mauro, FileBench [Online]. Available:

http:// www.solarisinternals.com/si/tools/filebench/

• http://www.intel.com/pressroom/.html

• http://www.physorg.com/news/.html

• http://www.storageview.com/.html](https://image.slidesharecdn.com/pptssd-130427231934-phpapp01/85/Ppt-ssd-24-320.jpg)