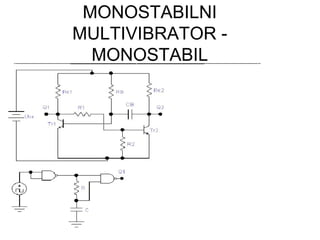

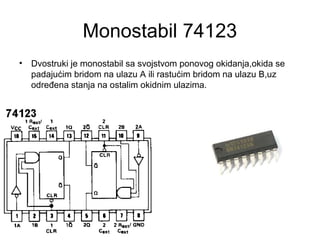

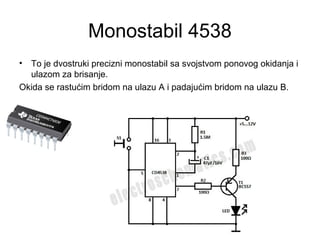

Monostabilni multivibrator je sklop s jednim stabilnim stanjem koji prelazi u kvazistabilno stanje uz promjenu ulaza. Razlikujemo monostabile s i bez svojstva ponovnog okidanja te različite vrste integriranih monostabila. Najčešće korišteni integrirani sklop za monostabil je 555, koji se može konfigurirati kao monostabilni ili astabilni multivibrator.