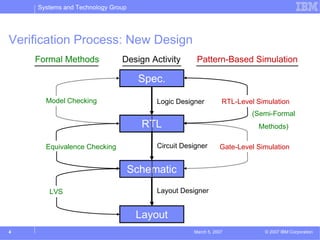

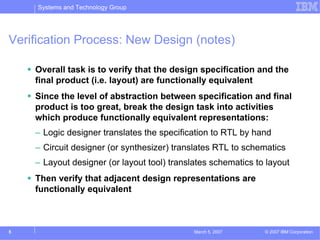

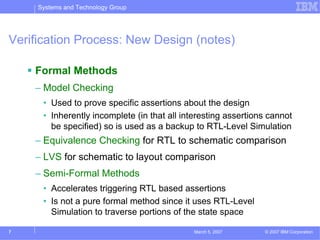

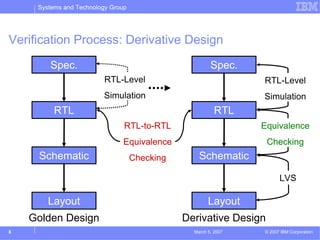

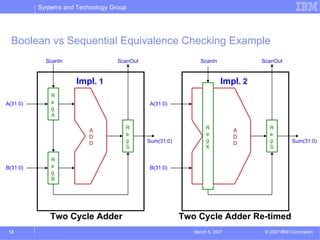

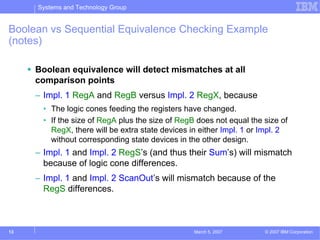

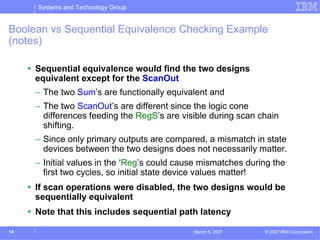

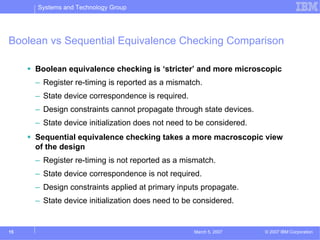

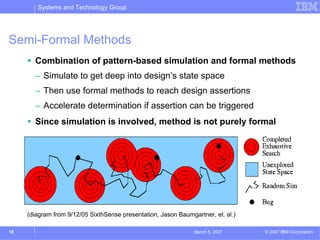

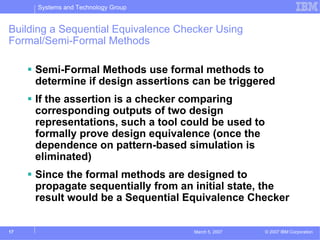

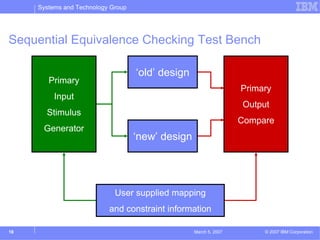

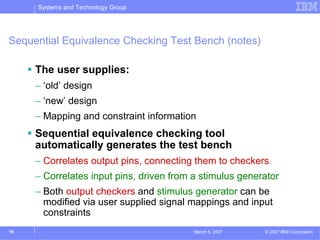

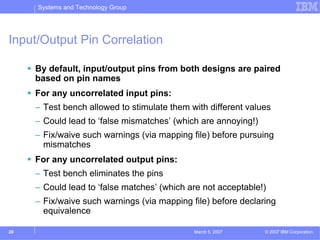

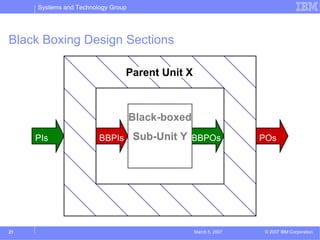

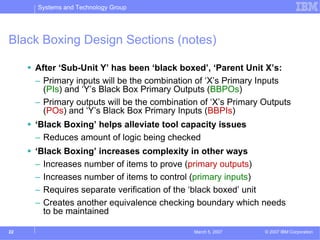

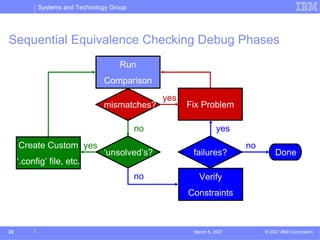

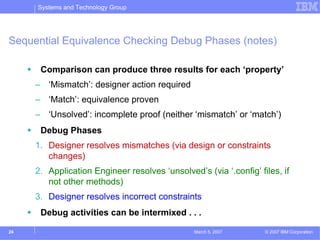

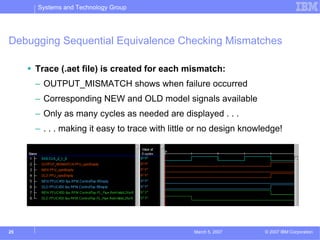

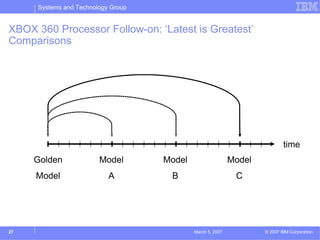

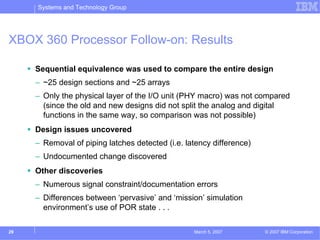

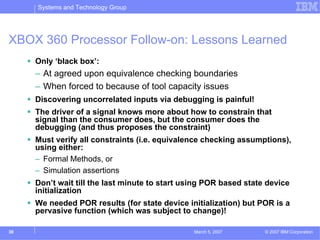

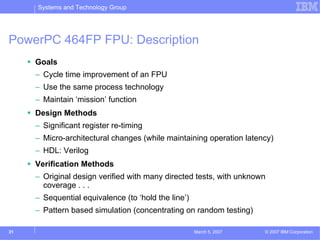

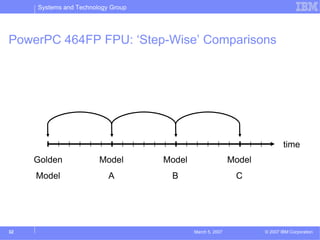

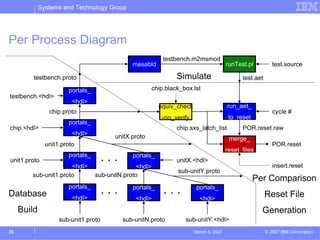

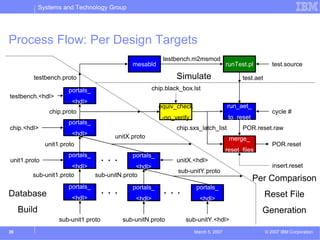

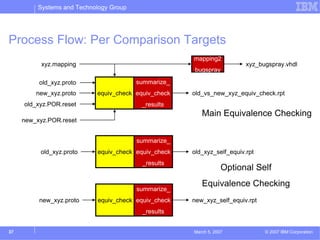

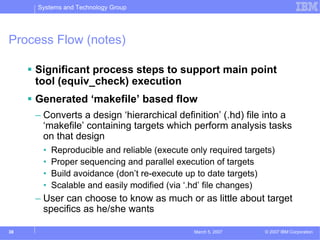

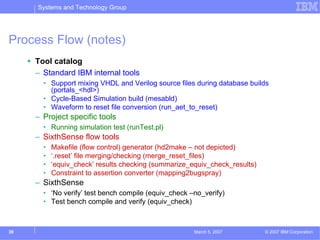

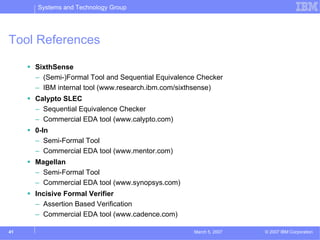

The document discusses formal verification methods like formal equivalence checking and how they can be used at different stages of the design process, including verifying that design representations are functionally equivalent from specification to layout for new designs and across derivative designs. It also explains the difference between boolean and sequential equivalence checking and provides an example comparing two implementations of a two cycle adder to illustrate the types of mismatches each approach can find.