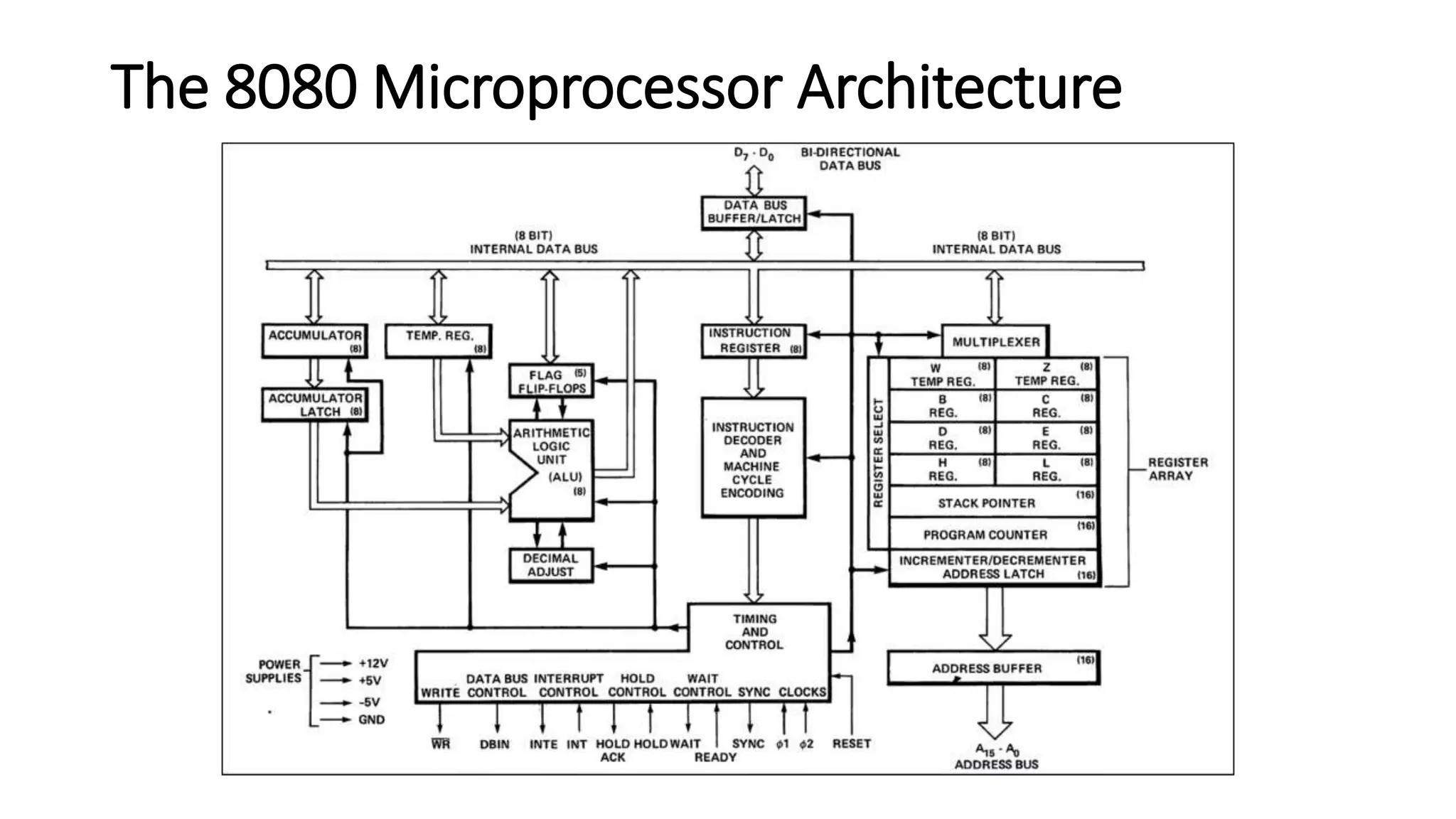

The 8080 microprocessor has the following key functional units and registers:

- Register array including program counter, stack pointer, and seven 8-bit registers

- Arithmetic logic unit (ALU)

- Instruction register and control section

- Bi-directional data bus

It uses a 16-bit address bus and 8-bit data bus. The instruction set includes instructions for data transfer, arithmetic, logical operations, branching, stack/I/O, and machine control. Fetching and executing instructions follows the basic fetch-decode-execute cycle.