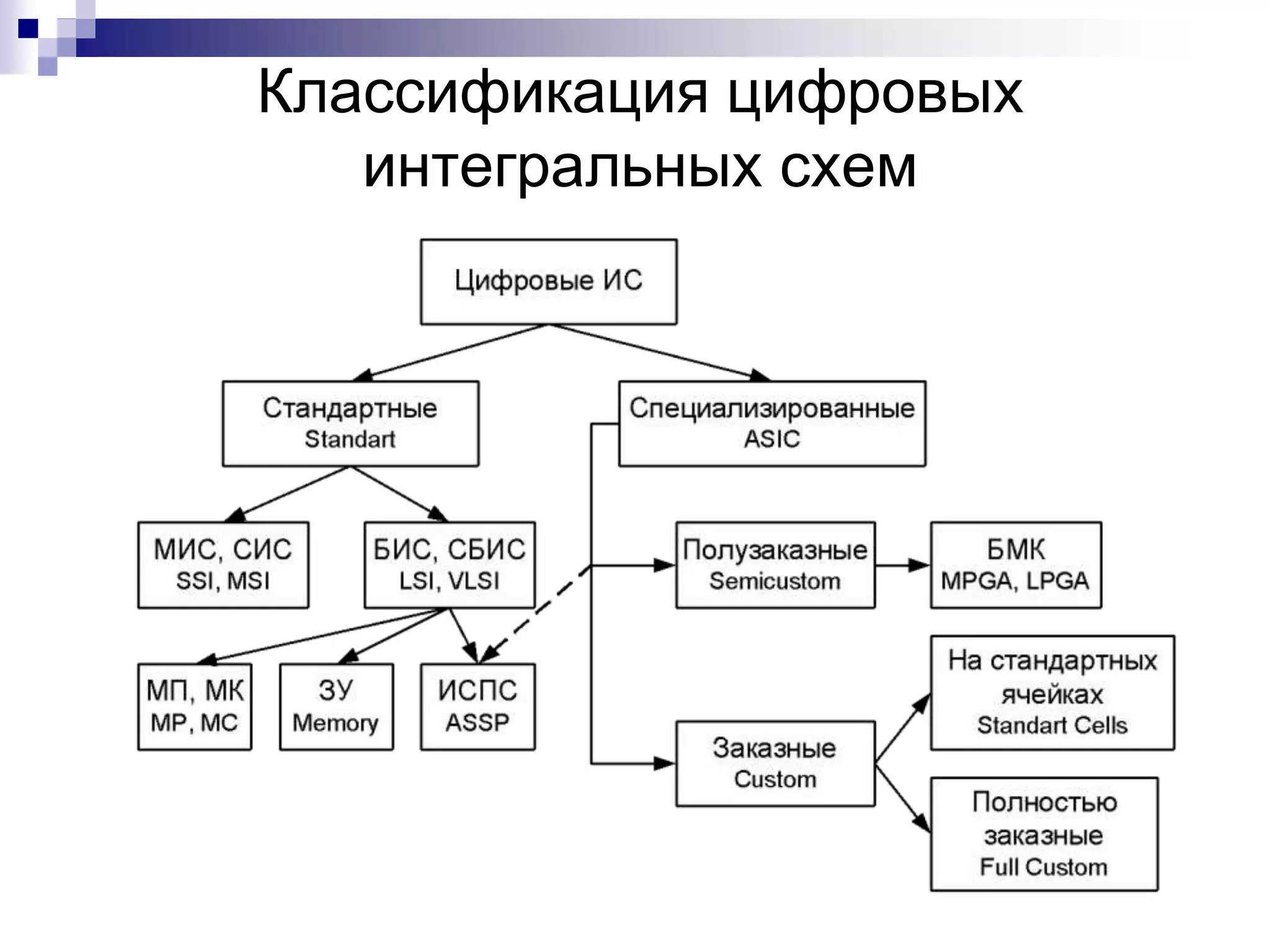

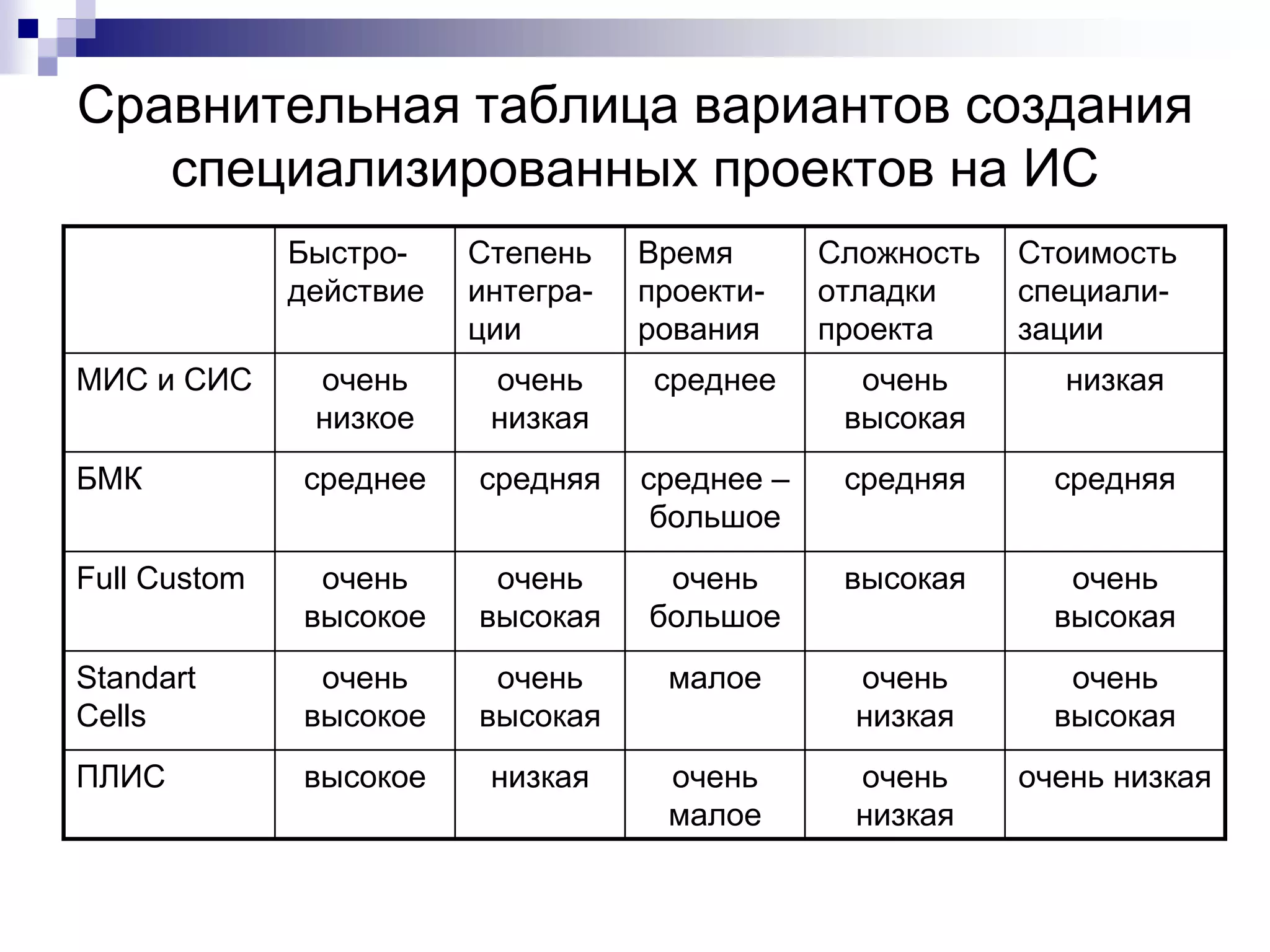

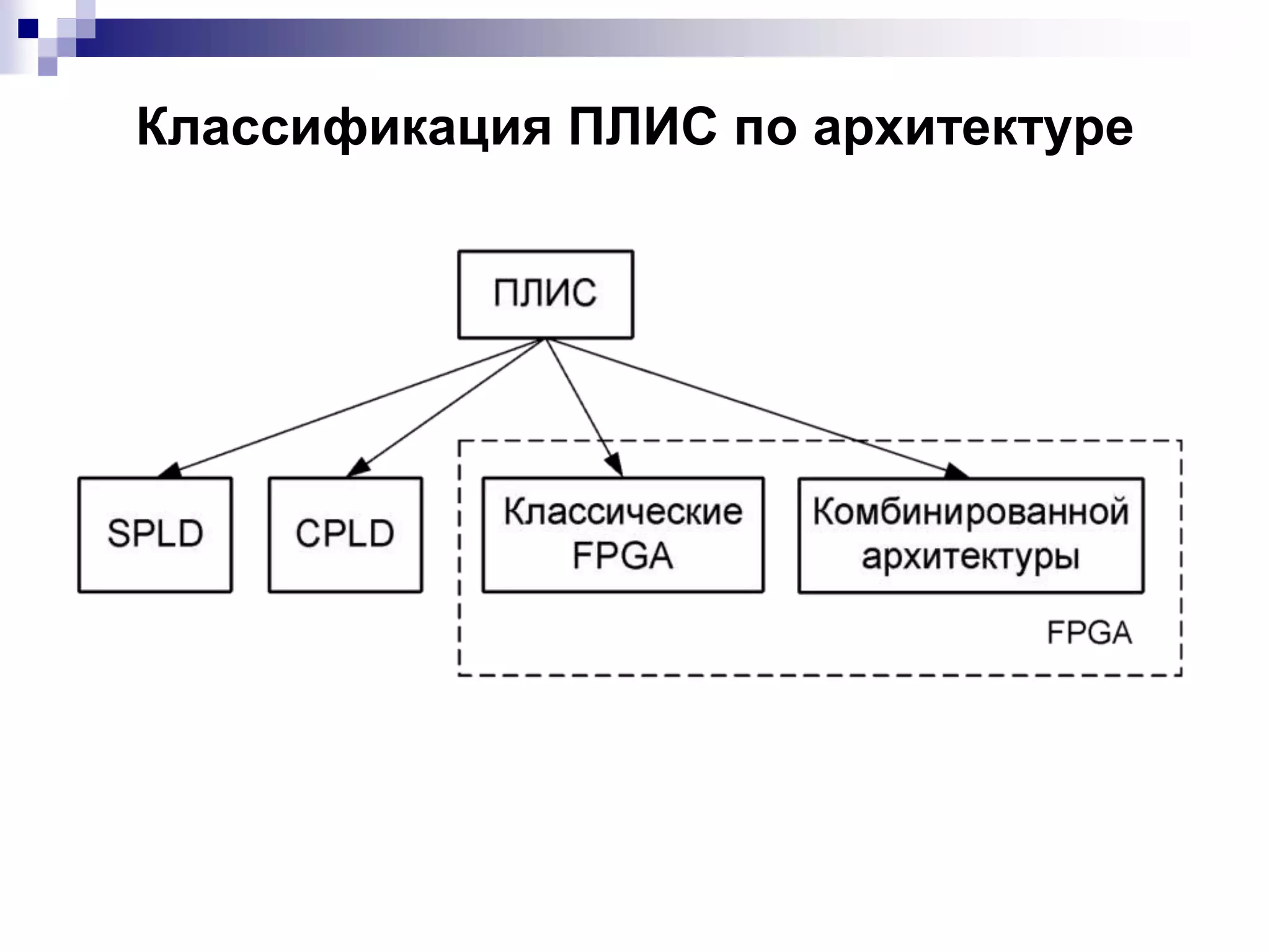

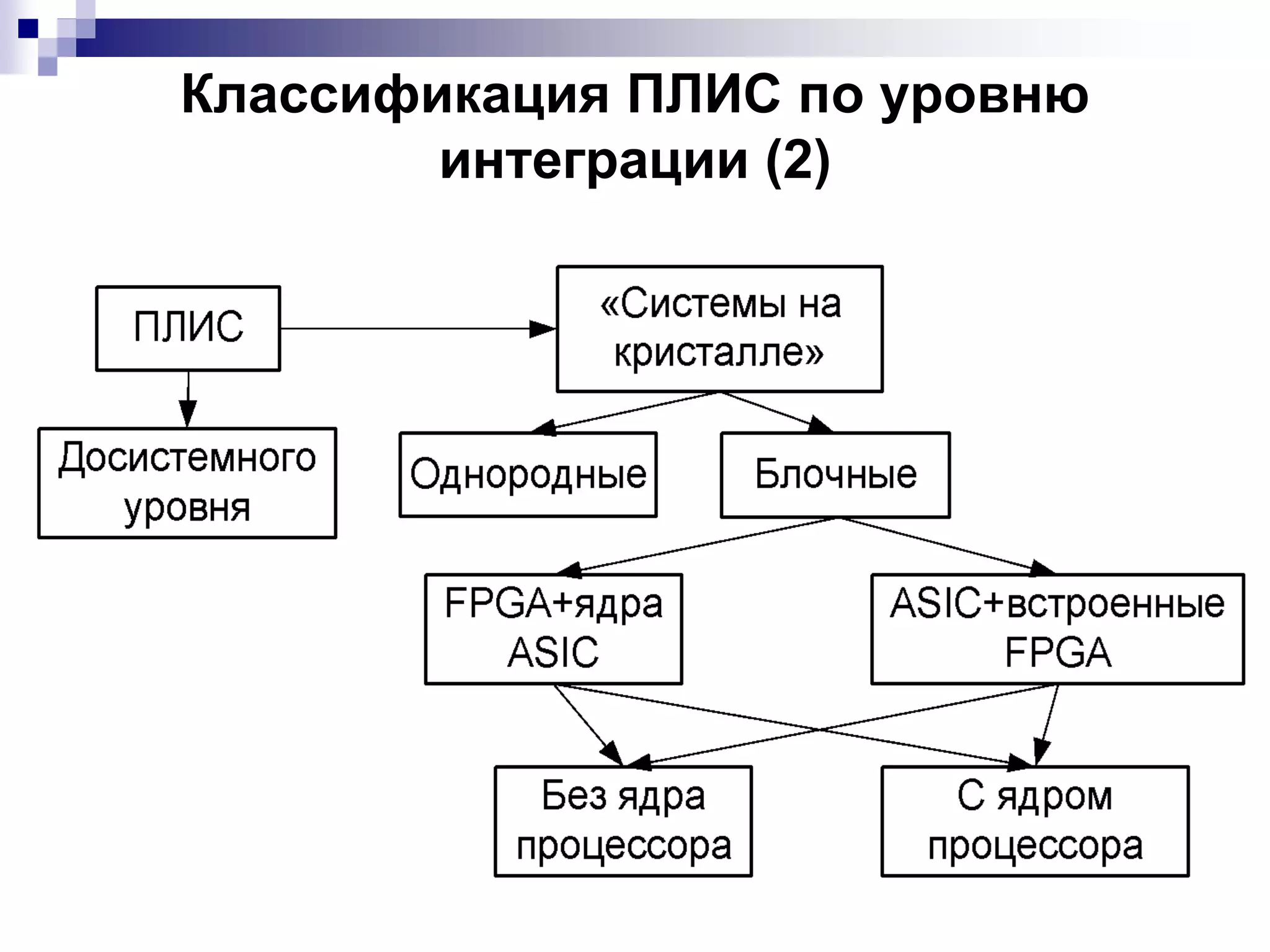

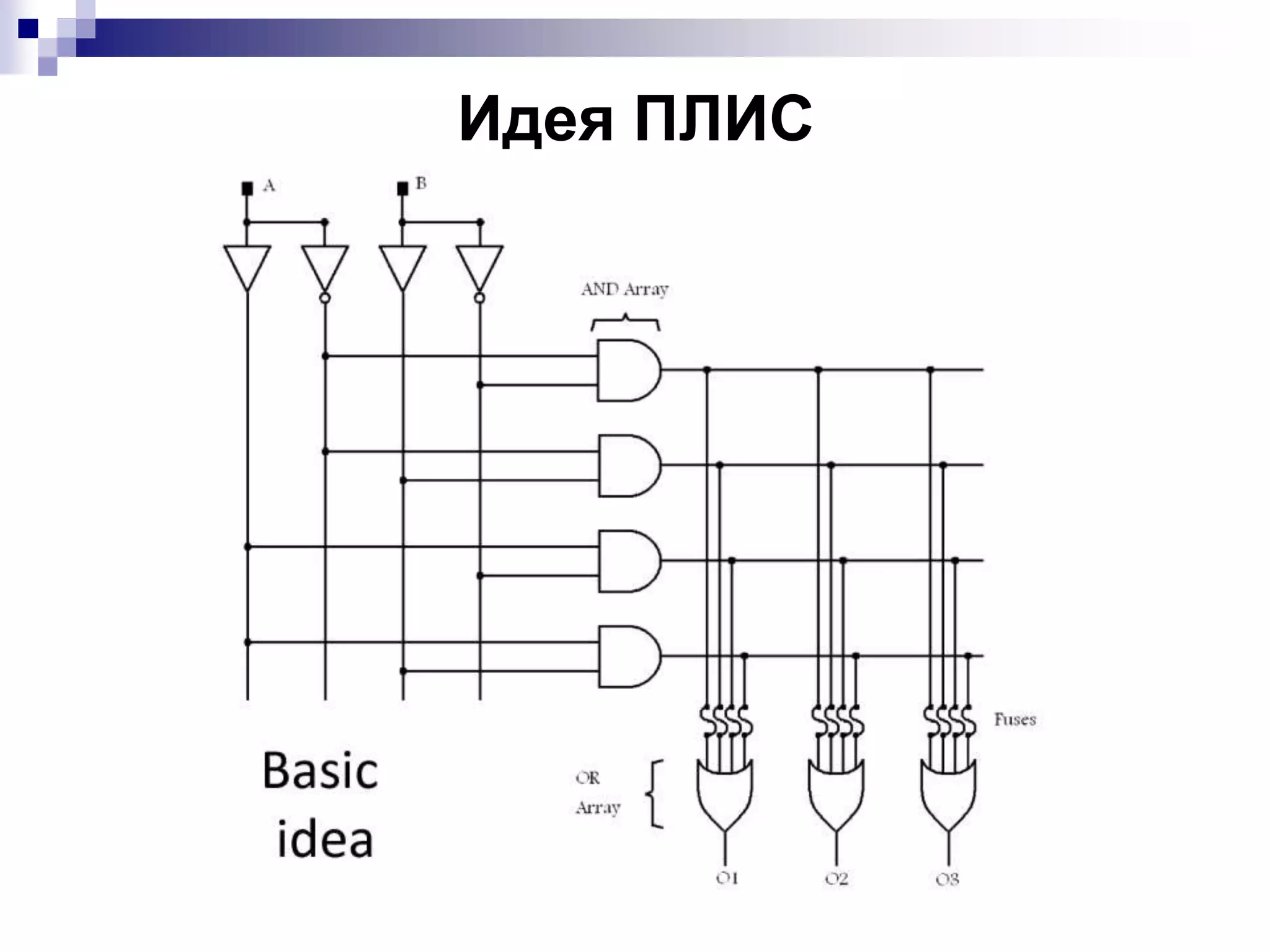

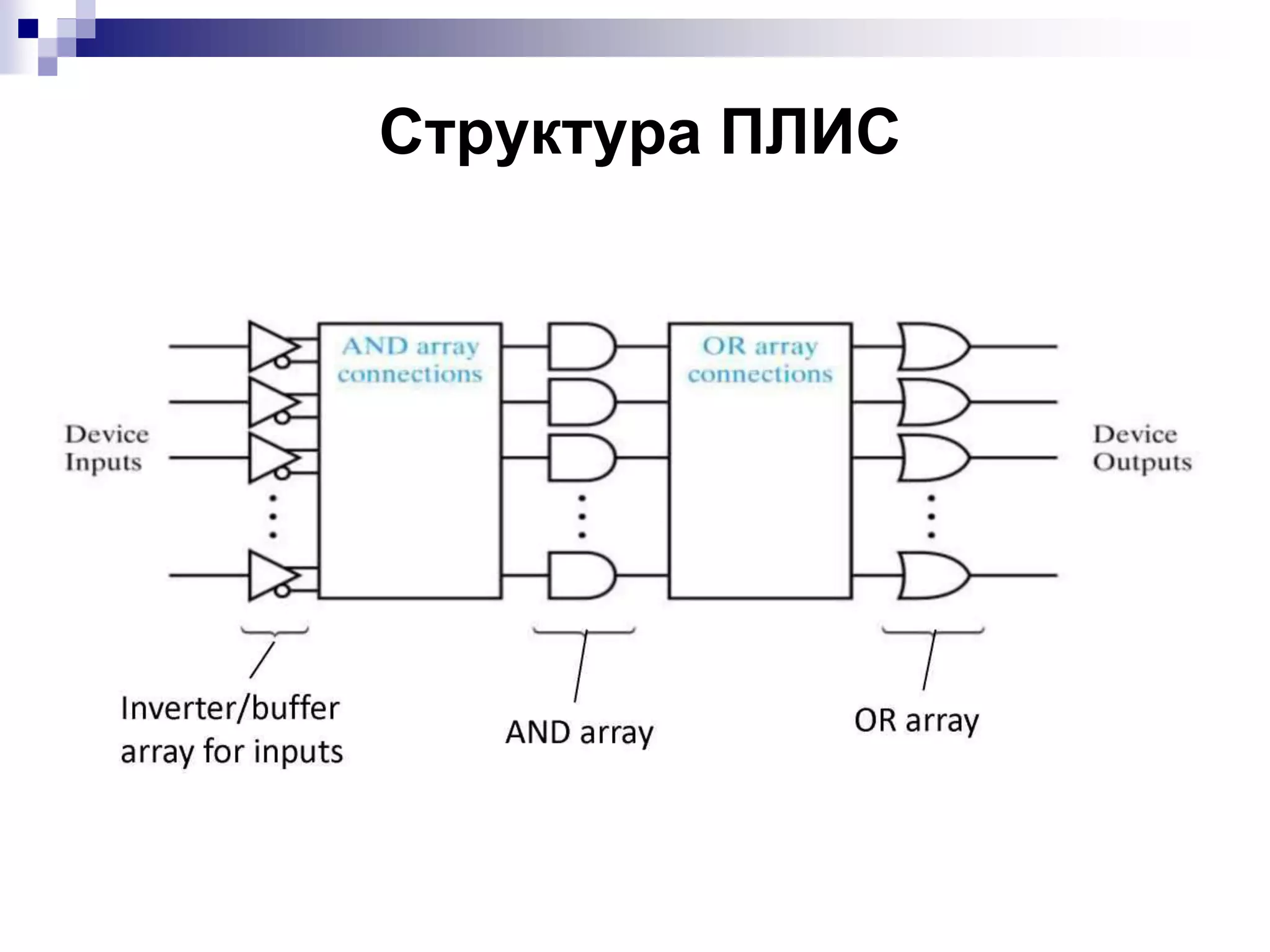

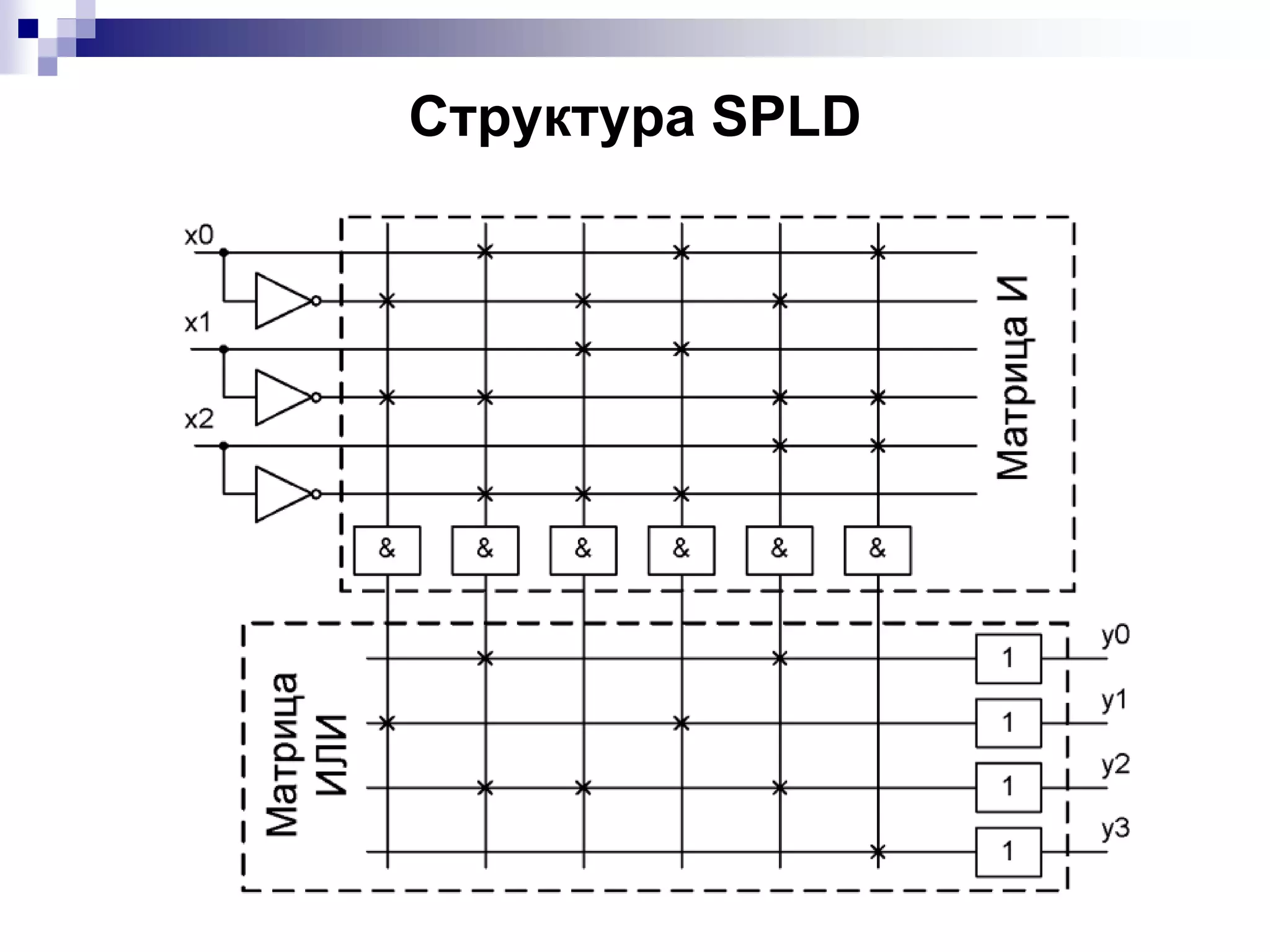

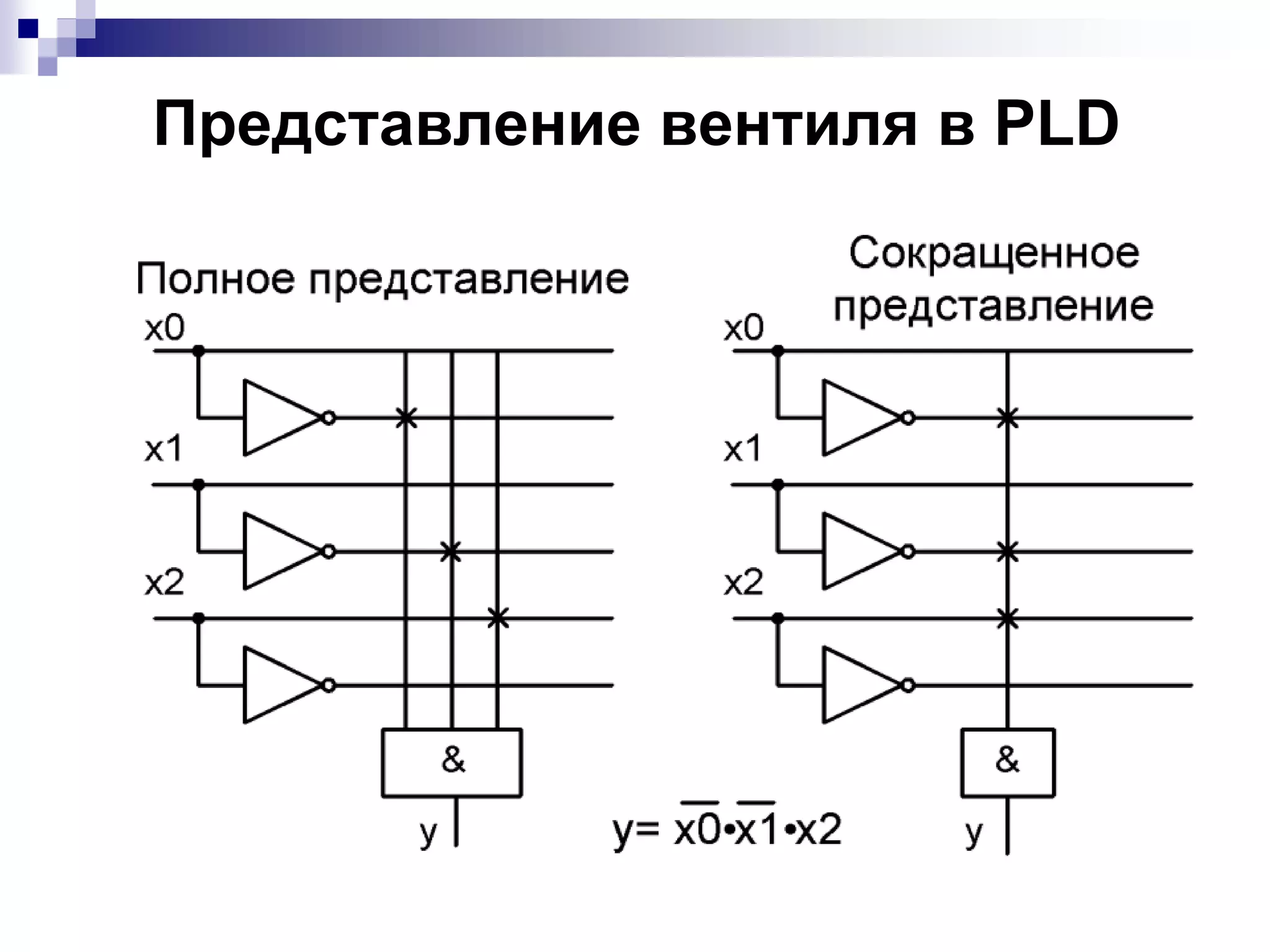

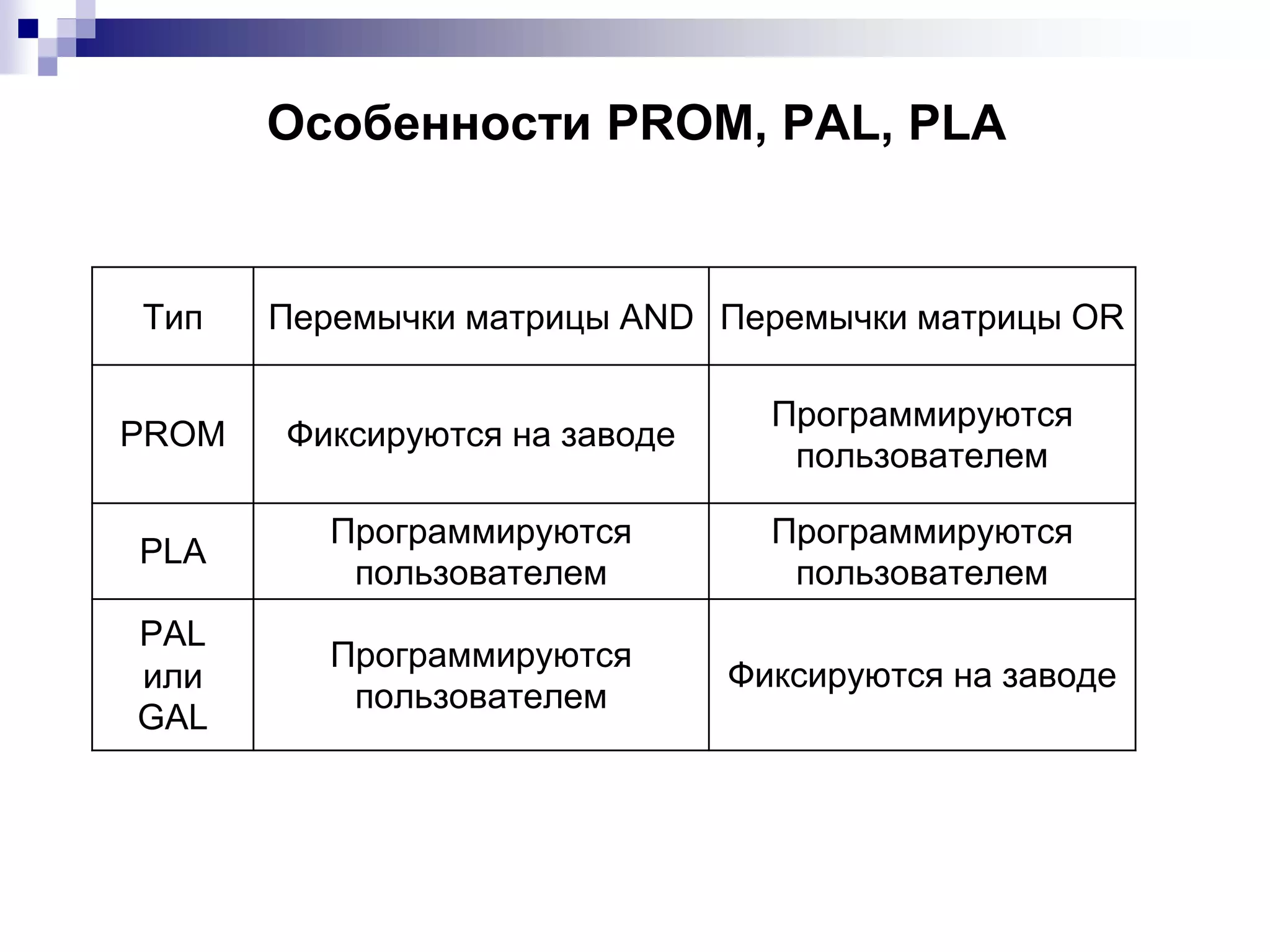

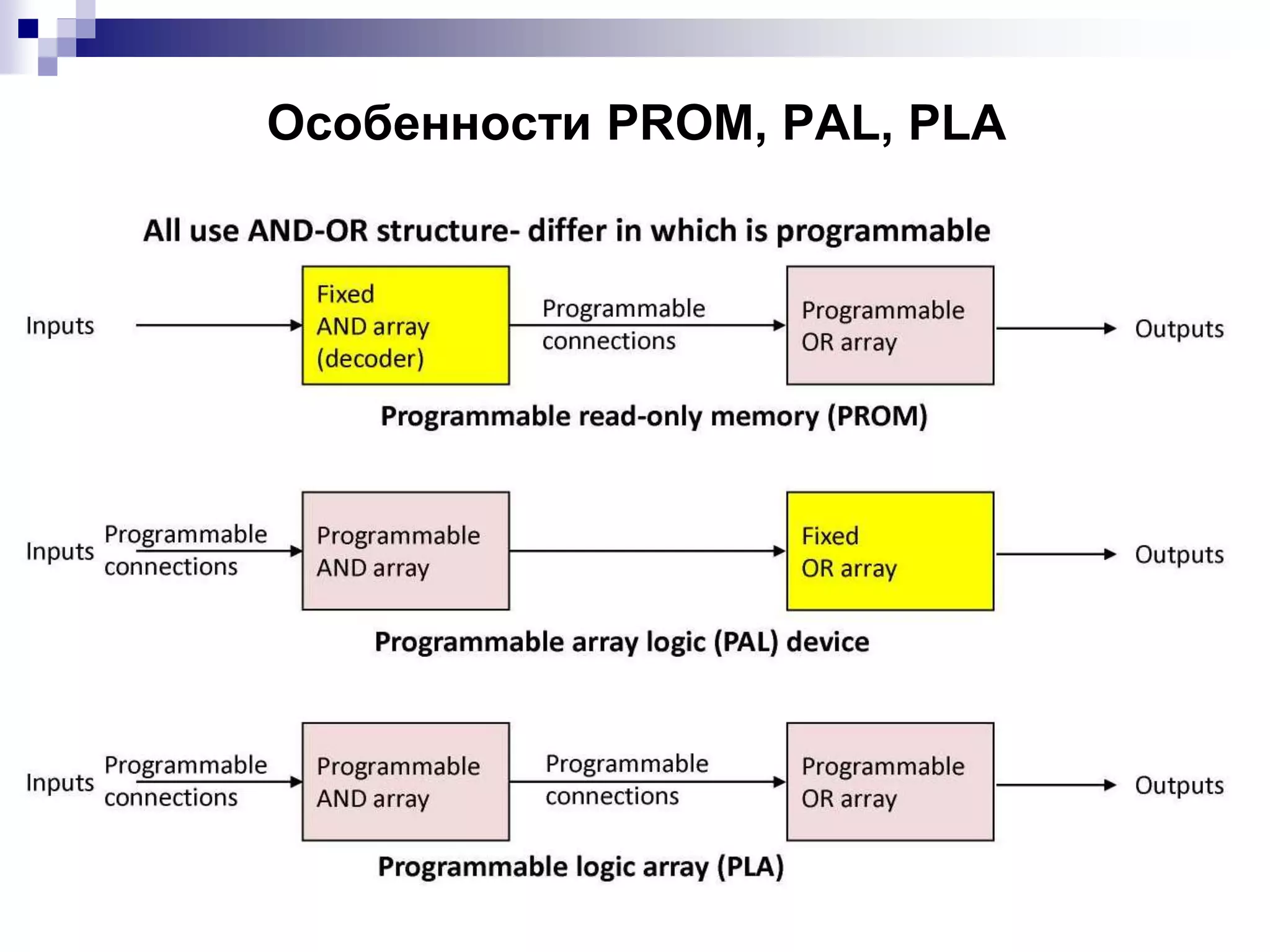

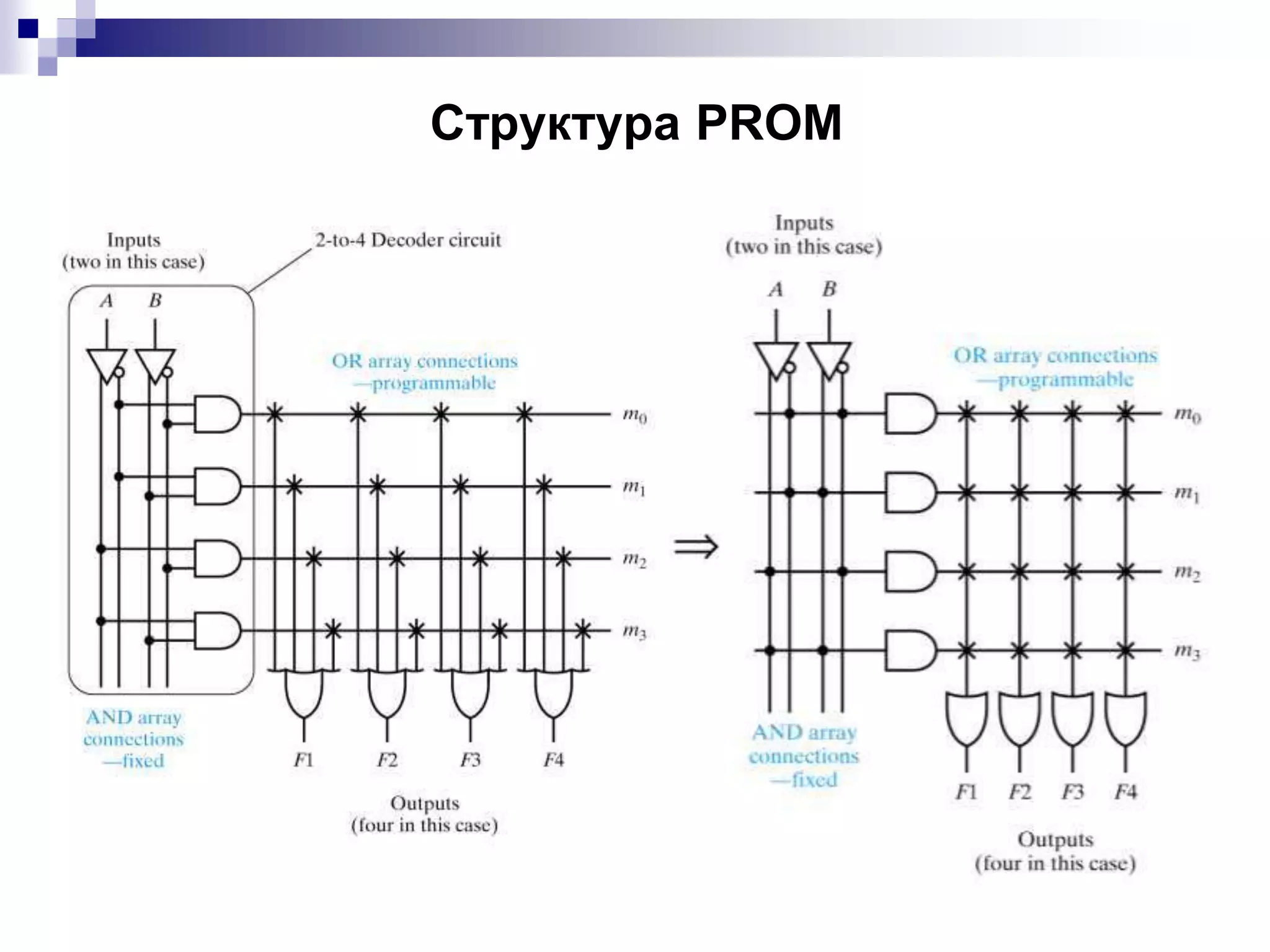

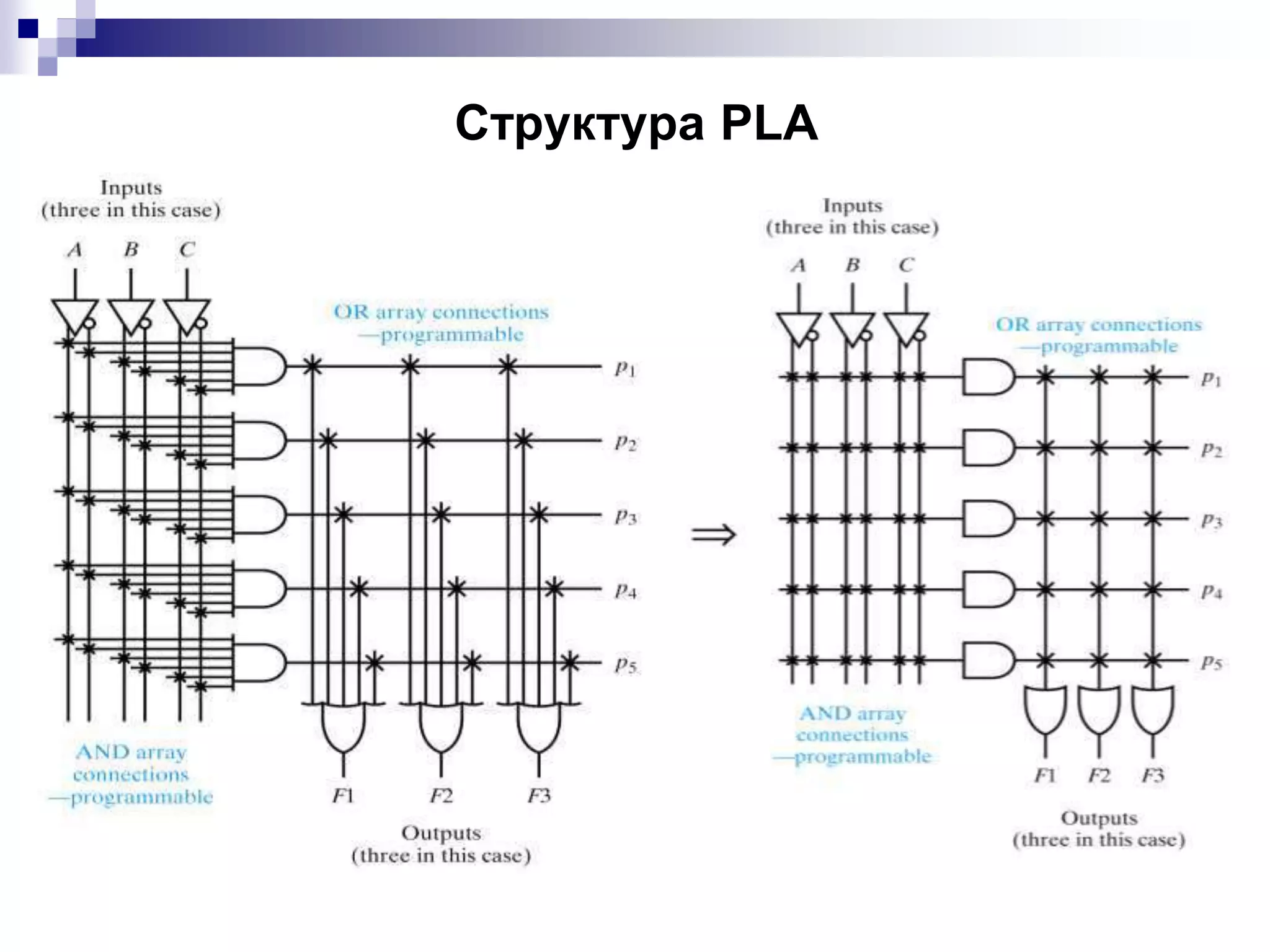

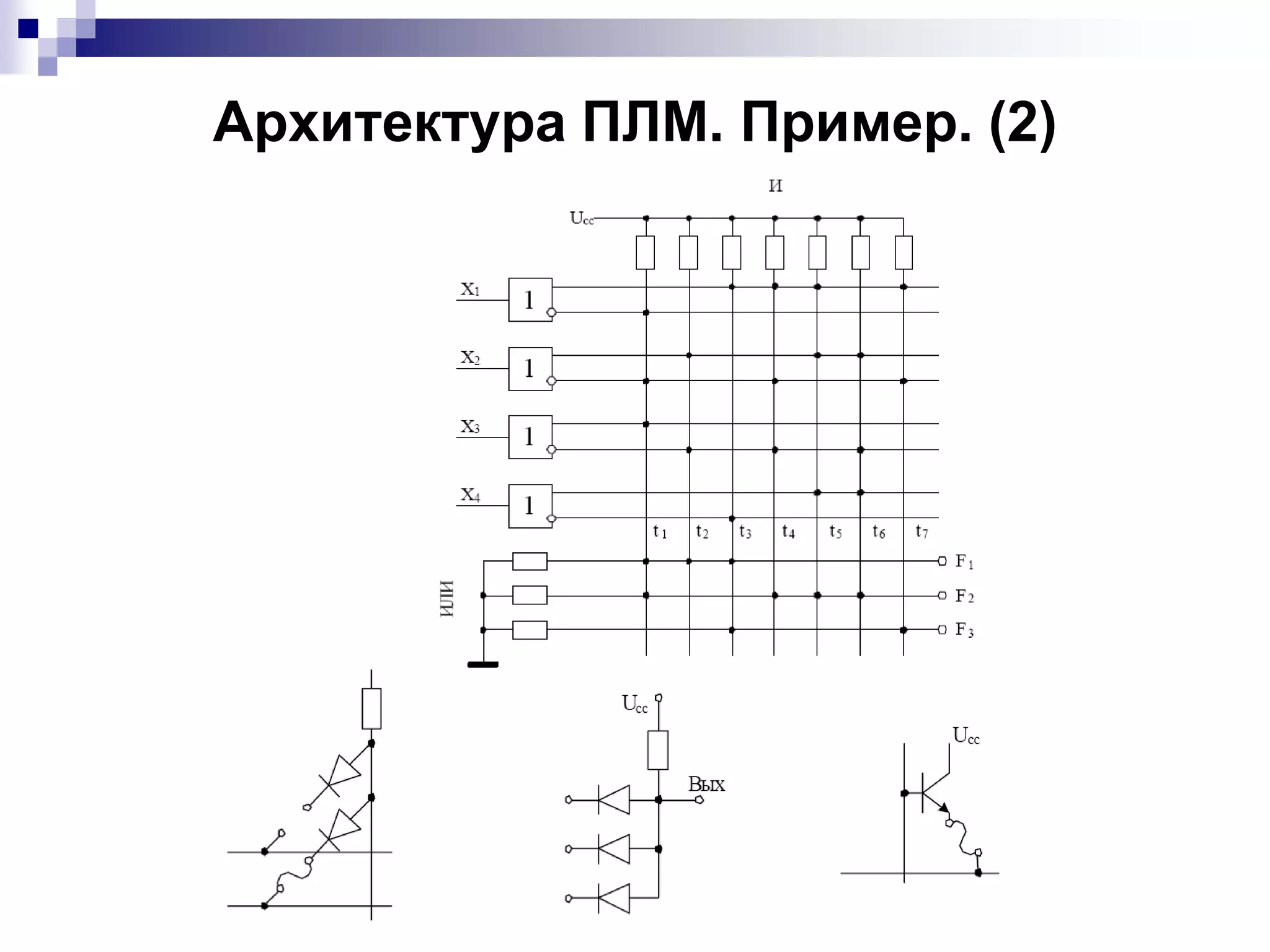

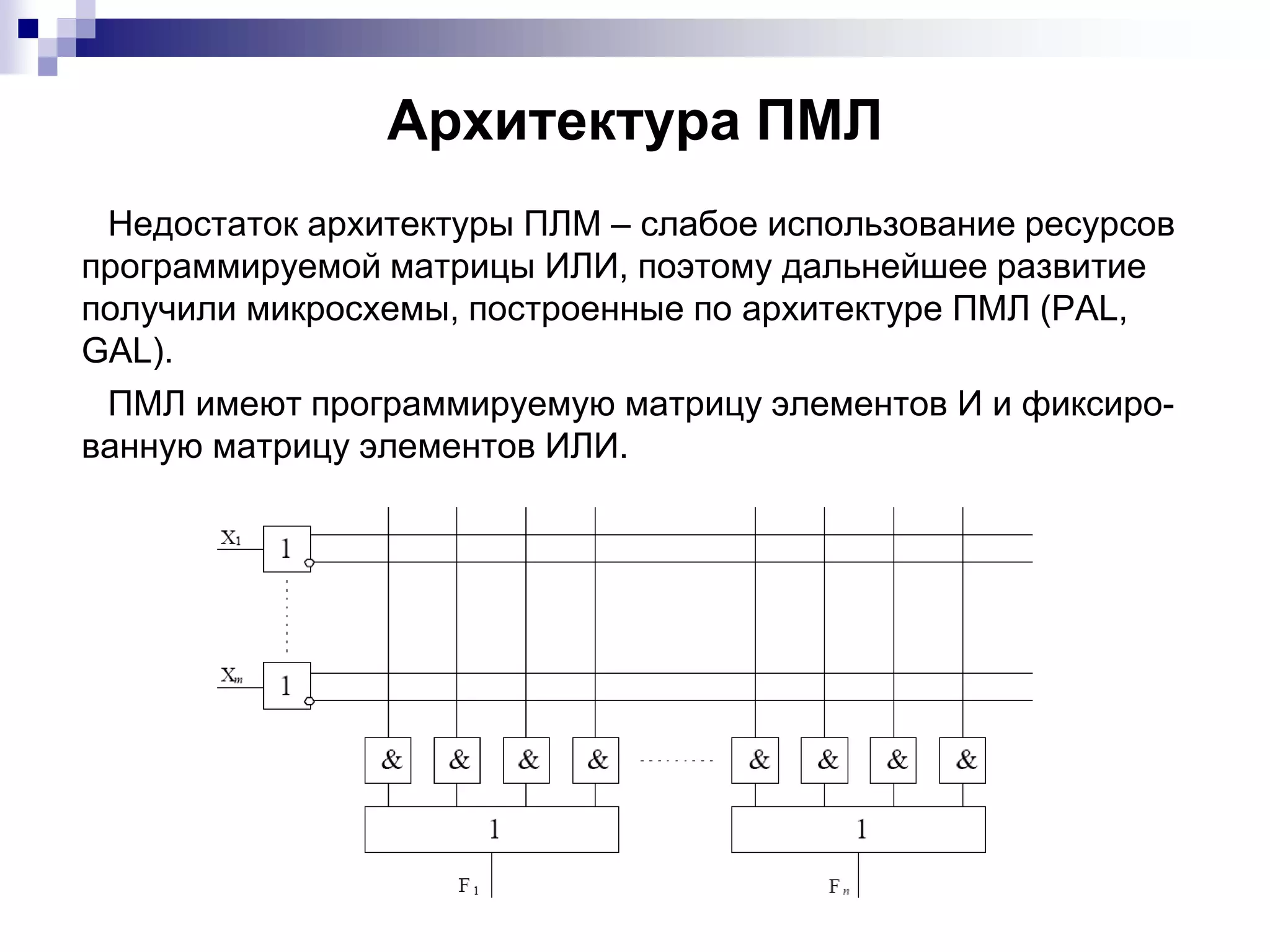

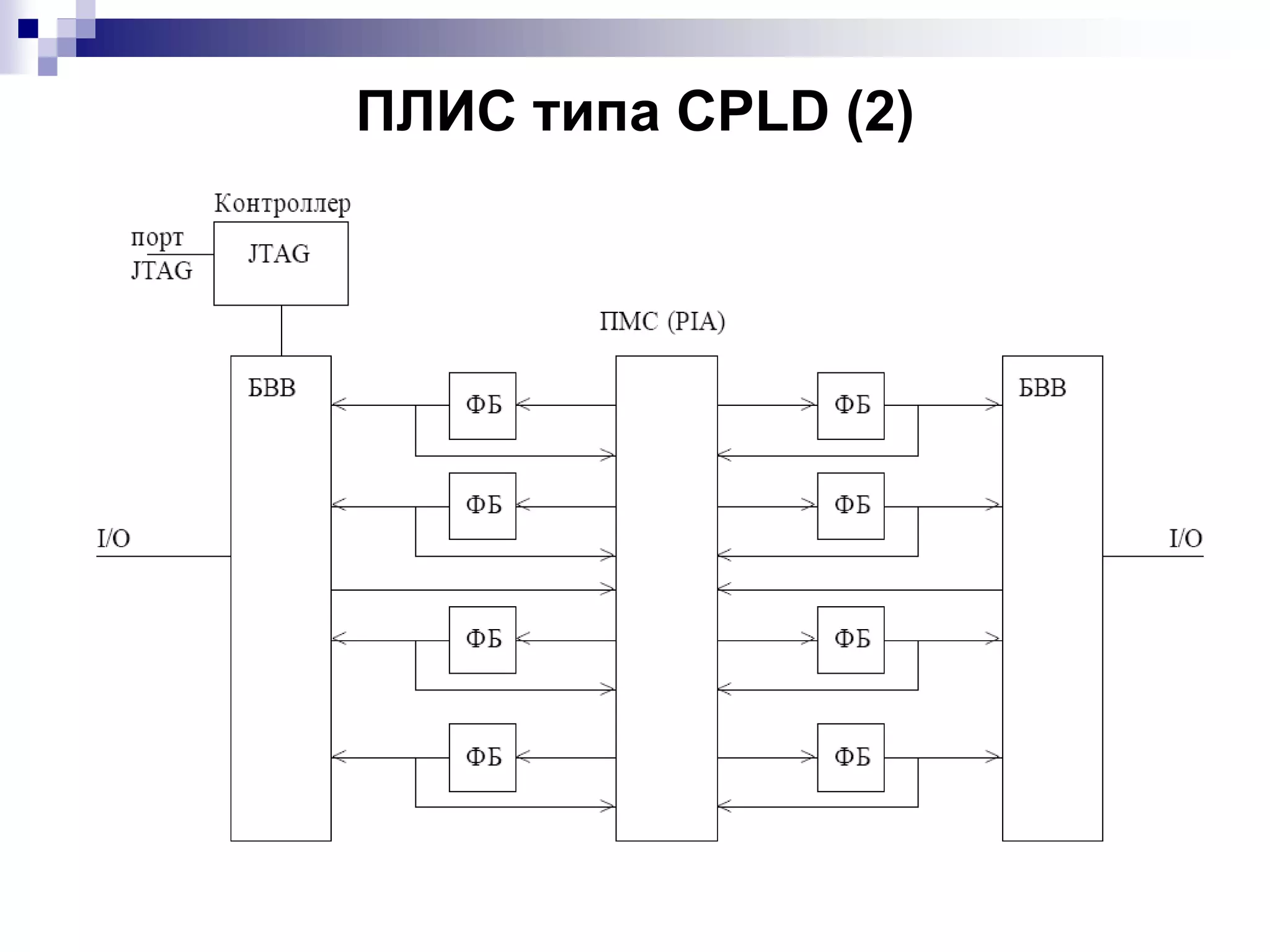

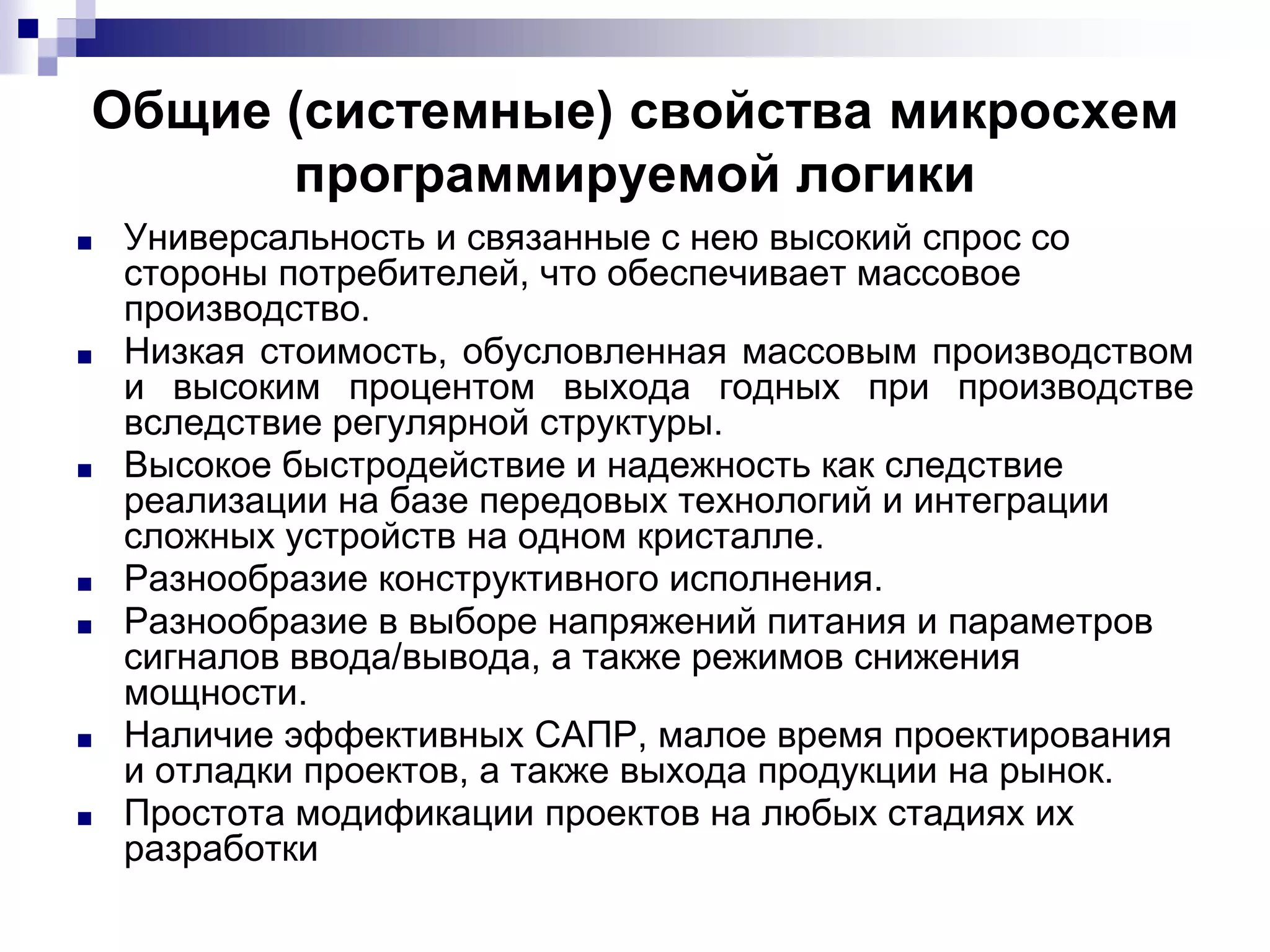

Документ посвящен цифровым программируемым логическим интегральным схемам (ПЛИС), их классификации и архитектурным особенностям. Обсуждаются преимущества ПЛИС, такие как снижение стоимости и сроков разработки, а также их применение в специализированных и массовых проектах. Основное внимание уделяется структуре ПЛИС, базовым матричным кристаллам и различным типам, включая FPGA и CPLD.