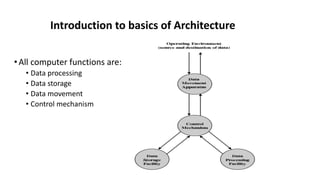

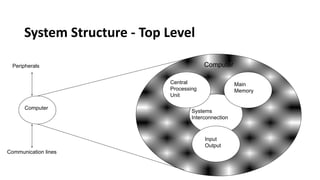

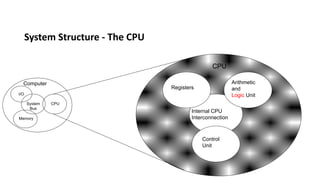

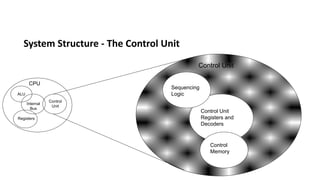

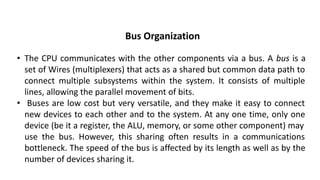

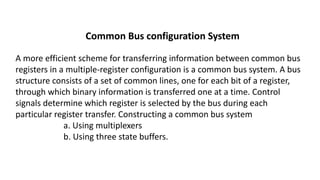

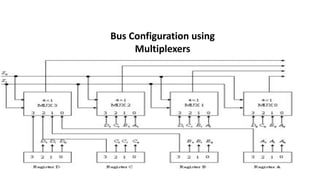

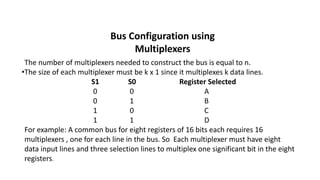

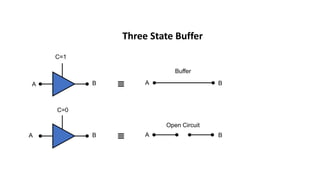

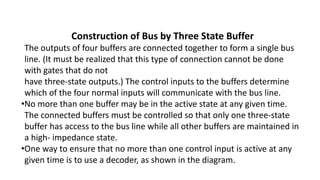

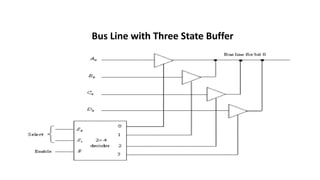

The document provides an overview of computer architecture, detailing functions such as data processing, storage, movement, and control. It explains the structure of a computer system, focusing on the CPU, bus systems, and common bus configurations for efficient information transfer. The document also highlights the use of multiplexers and three-state buffers in constructing bus systems to manage data flow among various components.