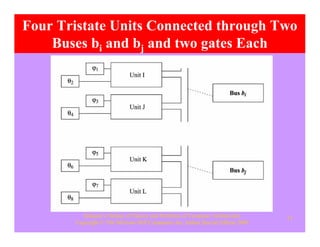

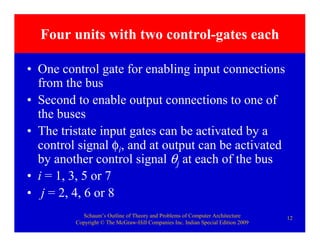

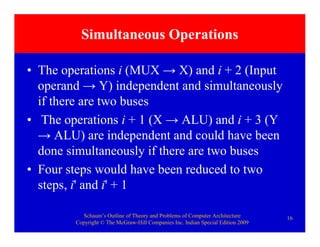

Multiple bus organization allows a processor to perform independent operations simultaneously. A single bus configuration requires units to share a common bus sequentially, whereas multiple independent buses allow multiple transfers to occur in parallel. This reduces the number of clock cycles needed to complete a set of independent operations, improving processor performance.