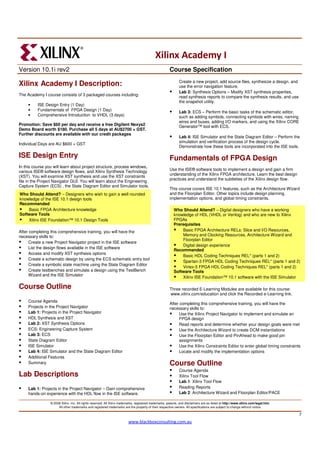

The document is a brochure for Black Box Consulting, outlining their products and services, including recruitment, consulting, and training related to Xilinx technologies. It details various training courses, recruitment processes, and consulting services aimed at improving design implementation and efficiency for FPGA projects. Additionally, it includes information on pricing, terms, and contact details for potential clients.