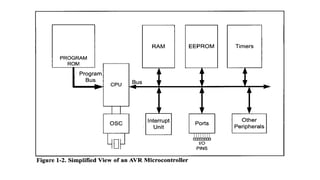

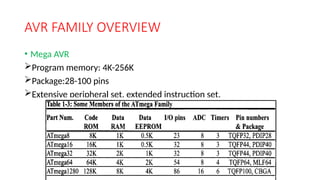

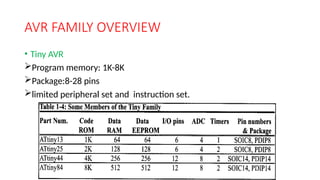

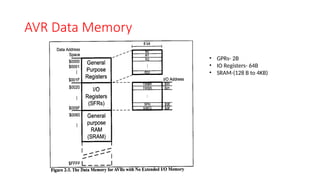

The document provides an overview of the AVR family of microcontrollers, detailing different types including classic AVR, mega AVR, tiny AVR, and special purpose AVR. It outlines features such as program memory capacities, package sizes, and the data memory structure, as well as instructions related to data handling and assembly language directives. Additionally, it discusses the architecture of RISC processors, highlighting their fixed instruction sizes, register usage, and execution efficiency.