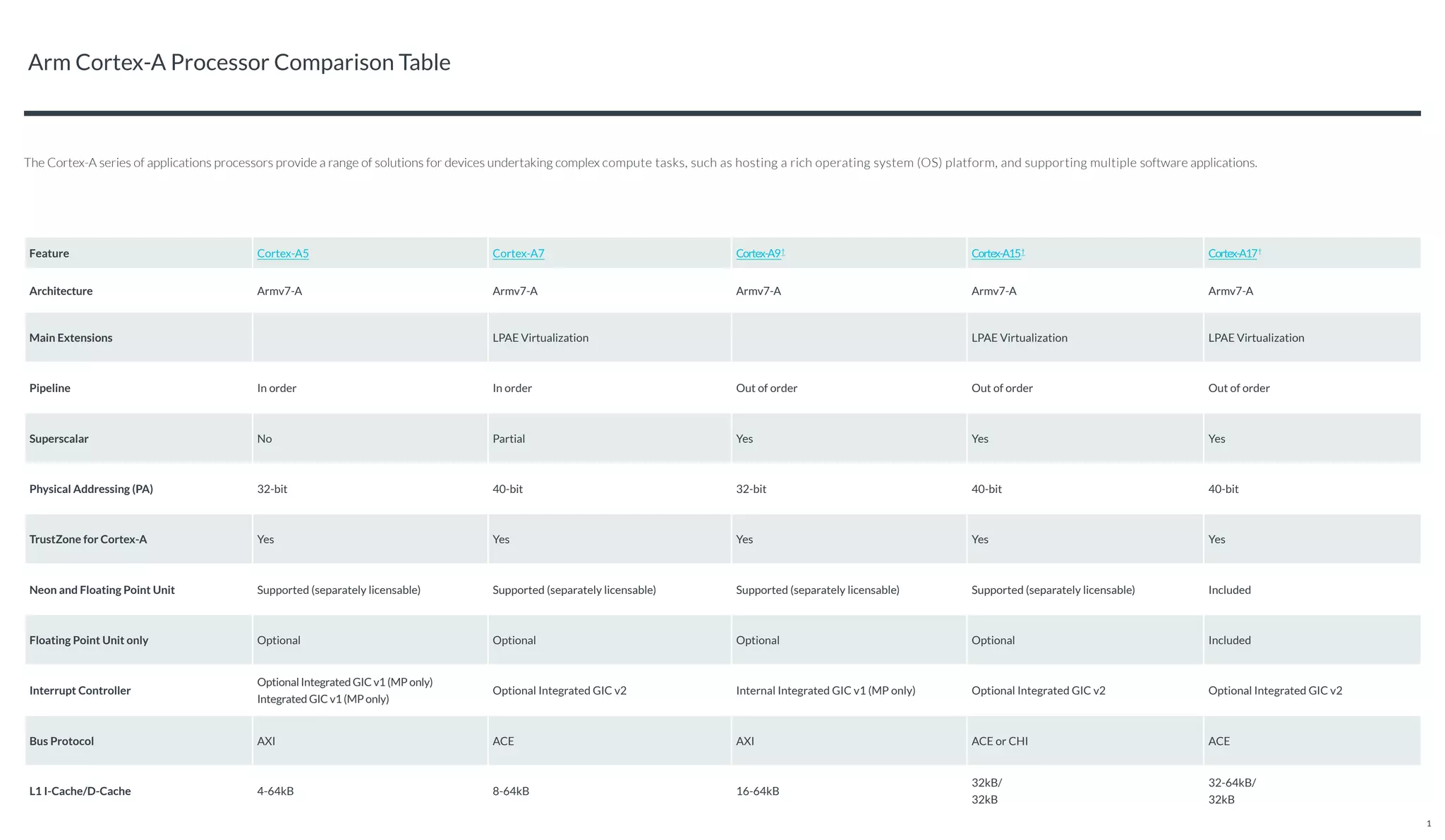

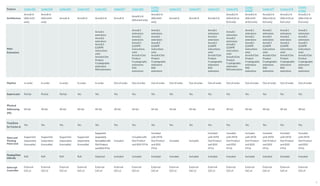

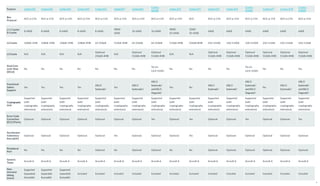

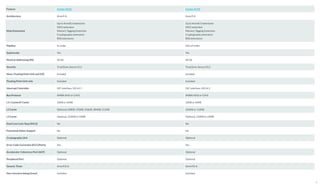

The document provides a comparison table of Cortex-A series applications processors from Arm. It details the key features of different processor models including the Cortex-A5, A7, A9, up to the latest Cortex-A78AE. The table outlines specifications such as architecture, extensions, pipeline, address width, cache sizes, and safety/security features. The Cortex-A series provides solutions for complex compute tasks in devices, supporting operating systems and multiple applications.