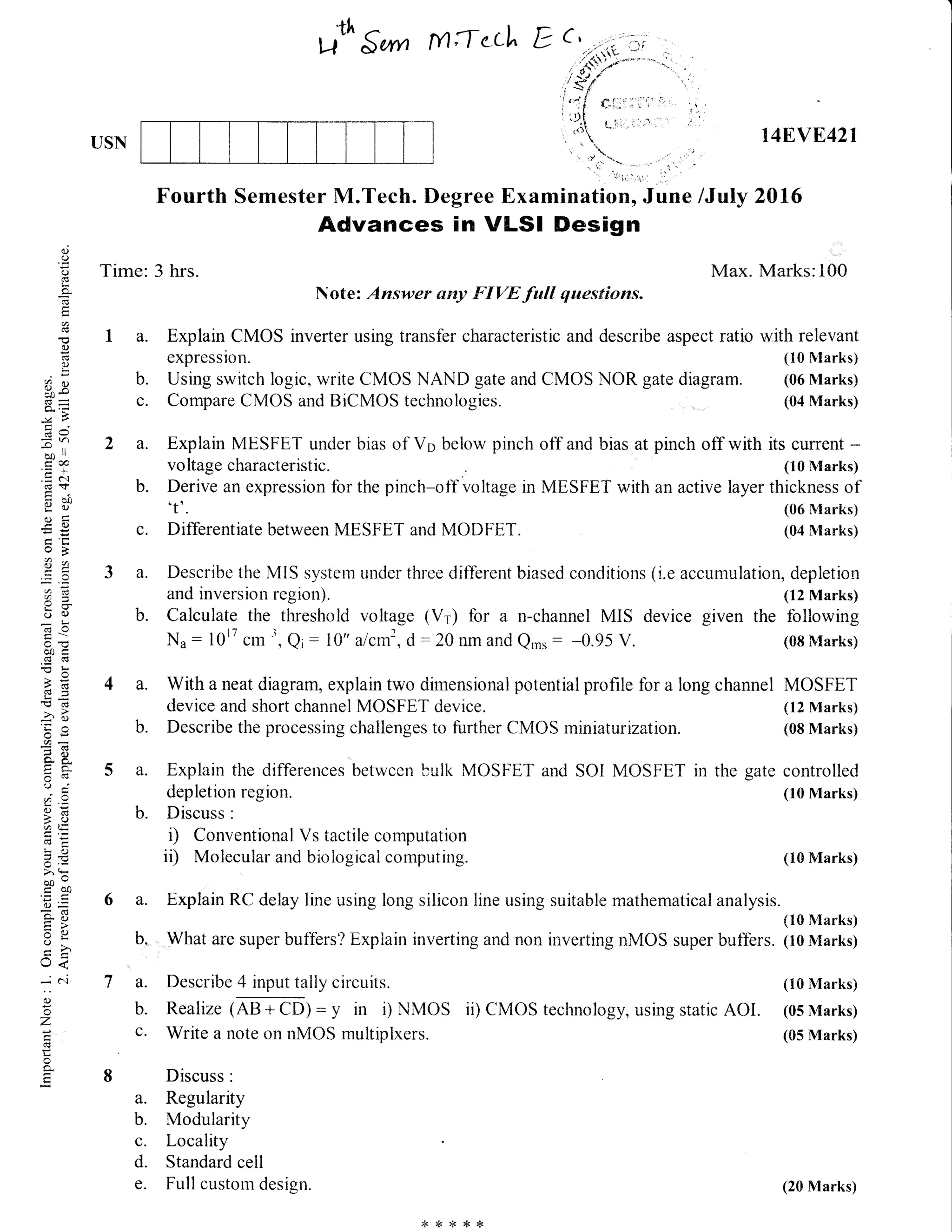

This document appears to be an exam for a digital circuits course, as it covers topics like CMOS inverters, MESFETs, MOSFETs, finite state machines, logic minimization techniques, and hardware description languages. The exam consists of 20 multi-part questions worth a total of 100 marks. Students are instructed to answer any 5 full questions from the list provided.