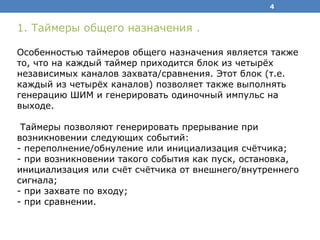

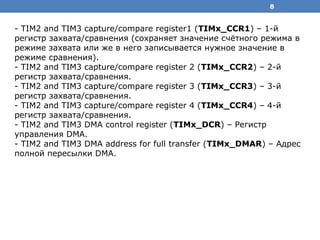

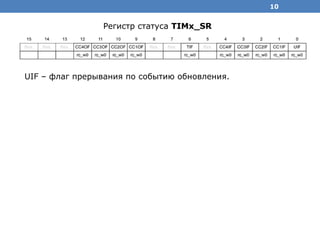

Документ описывает таймеры микроконтроллеров STM32, классифицируя их на три типа: базовые таймеры, таймеры общего назначения и расширенные таймеры управления. Приведены характеристики и функции каждого типа таймеров, включая блока независимых каналов захваченного/сравнившего и особенности работы с прерываниями. Также обсуждаются основные регистры, управляющие функциональностью таймеров, и их роль в настройке и работе таймеров.