MANUAL TEST ENGINEER

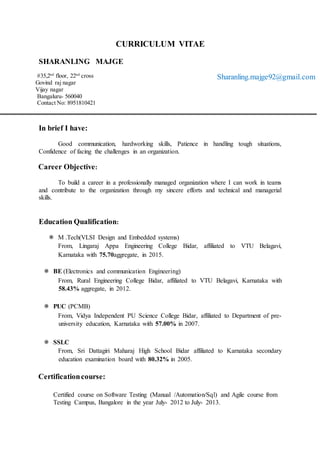

- 1. CURRICULUM VITAE SHARANLING MAJGE In brief I have: Good communication, hardworking skills, Patience in handling tough situations, Confidence of facing the challenges in an organization. Career Objective: To build a career in a professionally managed organization where I can work in teams and contribute to the organization through my sincere efforts and technical and managerial skills. Education Qualification: M .Tech(VLSI Design and Embedded systems) From, Lingaraj Appa Engineering College Bidar, affiliated to VTU Belagavi, Karnataka with 75.70aggregate, in 2015. BE (Electronics and communication Engineering) From, Rural Engineering College Bidar, affiliated to VTU Belagavi, Karnataka with 58.43% aggregate, in 2012. PUC (PCMB) From, Vidya Independent PU Science College Bidar, affiliated to Department of pre- university education, Karnataka with 57.00% in 2007. SSLC From, Sri Dattagiri Maharaj High School Bidar affiliated to Karnataka secondary education examination board with 80.32% in 2005. Certificationcourse: Certified course on Software Testing (Manual /Automation/Sql) and Agile course from Testing Campus, Bangalore in the year July- 2012 to July- 2013. #35,2nd floor, 22nd cross Govind raj nagar Vijay nagar Bangaluru- 560040 Contact No: 8951810421 Sharanling.majge92@gmail.com

- 2. Work Experience: Area - Manual testing (software) and Automation Organization - Testing campus, Vijay Nagar, Bangalore Profile - As Intern Quality Assurance Engineer Period - From 1st July 2015 to 31st oct 2015 Technical Skills: Software skills: Basic computer skills, MS office. Operating Systems :Windows XP/2000/07, VxWorks (RTOS) Knowledge of: SDLC (Software Development Life Cycle) Software Developmental Model such as (Water fall model, Spiral model, Prototype model, V-model, Hybrid modeland Derived model…etc.) Software Testing Types such as (White box testing , Black box testing, functional testing, Integration testing, System testing, Acceptance testing, Smoke testing, Exploratory testing, Adhoc testing, Compatibility testing, Globalization testing….etc.) Root cause Analysis Descriptive programming. Test case design techniques Defect Life cycle SQL Project1:AUTOMATE A WEBSITE CRM (Customer Relationship Management Tool) Here, I have updated contents in the website called salesforce.com by changing the features in the site with the help of CMS (content management system) by constructing frame work. Project2:AUTOMATING A WEB APPLICATIONS Here, I have automated web applications by the help of CRM tool by constructing frame work and writing test cases. Ex: Gmail web application and air India web application etc. And also worked on banking application and train ticket booking applications to check the functionality of application while doing manual testing.

- 3. Academic projects: Project title:GSM based border security alert system by sing microcontroller AT89s52 Duration: 4 Months. Team Size: 2 Members. Hardware used: Sensors circuit ADC Module GSM Modem Microcontroller module LCD module Software used: Kiel microvision3 Preload Embedded c for coding • It was an SMS alert system, where vibration sensors and camera were used to identify the unauthorized person entry into specified territory so that e-security can be achieved by wireless communication network with the help of GSM technology. Project title:A novel SDR trans-receiver architecture for communication systems on FPGA Duration: 8 Months. Team Size: 1Members. Workedin VED LABS Bengaluru. Hardware used: Intel Pentium IV Processor Spartan III FPGA Xilinx Spartan III FPGA development board JTAG cable, Power supply Software used: Operating System: Windows XP with SP2 Synthesis Tool: Xilinx 12.2. Simulation Tool: Modelsim6.3c. Language: Verilog • The SDR provides high processing capability, which means configurable higher data rates and modulation techniques. In this design, we are developing the whole QPSK Trans- receiver architecture using Verilog on Xilinx 13.4.

- 4. • The primary target of the venture is to outline and create building design for SDR Based QPSK Transceiver framework and its execution on FPGA. Paperpublications: ‘A NOVEL SDR TRANS- RECEIVERARCHITECTURE FOR COMMUNICATION SYSTEMS ON FPGA’ IJRET: International Journal of Research in Engineering and Technology, eISSN: 2319- 1163 | pISSN: 2321-7308,Certificate ID 110417004_1, Volume: 04 Special Issue: 05 | NCATECS-2015 | May-2015, Available @ http://www.ijret.org Extracurricular Activities: • Interested in sports, reading newspaper, learning new technical skills and music. Achievements: • Participated in INTERNATIONAL CONFERENCE ON COMMUNICATIONCOMPUTATION, CONTROL AND NANO TEACHNOLOGY-2010 Personal Details: Father Name : Shivasharnappa Majge Mother Name : Sri devi Date ofBirth : 11/06/1989 Marital status : Single Nationality : Indian Mother Tongue : Kannada Languages known : English, Hindi & Kannada Permanent Address : Sharanling s/o Shivasharnappa Majge Plot no 61, OPP 17-4-225 ‘SHARAN KRUPE’,Mahesh Nagar Bidar -585403 Mobile No. : 8951810421 E-mail ID : sharanling.majge92@gmail.com I hereby certify that the above details are correct and complete to the best my knowledge and belief. Date: Place: Bangaluru (Sharanling Majge)