Resume_Venkatesh

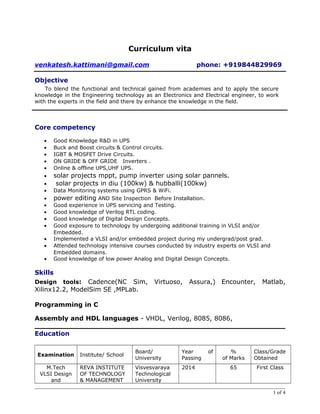

- 1. Curriculum vita venkatesh.kattimani@gmail.com phone: +919844829969 Objective To blend the functional and technical gained from academies and to apply the secure knowledge in the Engineering technology as an Electronics and Electrical engineer, to work with the experts in the field and there by enhance the knowledge in the field. Core competency · Good Knowledge R&D in UPS · Buck and Boost circuits & Control circuits. · IGBT & MOSFET Drive Circuits. · ON GRIDE & OFF GRIDE Inverters . · Online & offline UPS,UHF UPS. · solar projects mppt, pump inverter using solar pannels. · solar projects in diu (100kw) & hubballi(100kw) · Data Monitoring systems using GPRS & WiFi. · power editing AND Site Inspection Before Installation. · Good experience in UPS servicing and Testing. · Good knowledge of Verilog RTL coding. · Good knowledge of Digital Design Concepts. · Good exposure to technology by undergoing additional training in VLSI and/or Embedded. · Implemented a VLSI and/or embedded project during my undergrad/post grad. · Attended technology intensive courses conducted by industry experts on VLSI and Embedded domains. · Good knowledge of low power Analog and Digital Design Concepts. Skills Design tools: Cadence(NC Sim, Virtuoso, Assura,) Encounter, Matlab, Xilinx12.2, ModelSim SE ,MPLab. Programming in C Assembly and HDL languages - VHDL, Verilog, 8085, 8086, Education Examination Institute/ School Board/ University Year of Passing % of Marks Class/Grade Obtained M.Tech VLSI Design and REVA INSTITUTE OF TECHNOLOGY & MANAGEMENT Visvesvaraya Technological University 2014 65 First Class 1 of 4

- 2. Embedded System Bangalore.Karnata ka, India Belgaum B.E. Electronics & Communicati on R.L.Jallappa Institute Of Technology, Bangalore, Karnataka, India Visvesvaraya Technological University Belgaum 2011 51.15 Second Class Diploma E & C Dr.G.S.Melkote rural polytechnic, Kuknoor, Karnataka, India Department of Technical Education, Bangalore, 2005 47 Second Class S.S.L.C Govt junior college Yelburga, Karnataka, India Karnataka Secondary Education Examination Board, Bangalore 2000 48.64 Second Class Experience 2. As a Sr.Engg in R&D: One Year (01/09/12 to still Date) Experience as a Sr.Engg in Power One Pvt Ltd, Bangalore. 1.As Service Engineer: Two Year experience in UPS testing and service field, During the year 2005-07,in POM Syetems & Services Pvt,Ltd, Bangalore. 2.As a Testing Engg: 0ne year (19/12/2011) in POM Syetems & Services Pvt,Ltd, Bangalore. Academic Projects: Title: Accident monitoring and data decimation for vehicular net works Role: Design engg Organization: R L J I T Bangalore Duration of Project in 2 Months: Description: Project uses Microcontroller AT89S52 and RF Transmitter and Receiver... This project makes it simple and easy for people to get information about accident conditions using GSM and GPS service. Tools Used : Keil Title: A low-cost VLSI implementation for efficient removal of Impulse noise Role: Design and Verification engg Organization: Reva Institute of Technology & Management Bangalore.Karnataka, India Duration of Project in 12 Months: Description: Image and video signals might be corrupted by impulse noise in the process of signal acquisition and transmission. In this paper, an efficient VLSI implementation for removing impulse noise is presented. Our extensive experimental results show that the proposed technique preserves the edge features and obtains excellent performances in terms of quantitative evaluation and visual 2 of 4

- 3. quality. The design requires only low computational complexity and two line memory buffers. Its hardware cost is quite low. Compared with previous VLSI implementations, our design achieves better image quality with less hardware cost. Synthesis results show that the proposed design yields a processing rate of about 167 M samples/second by using TSMC 0.18 m technology. Tools Used : Xilinx12.2, ModelSim SE. Title: Card and Code locker System Role: Design engg Organization: Dr.G.S.Melkote rural polytechnic, Duration of Project in 1 Months: Personal Details Name - Venkatesh kattimani Date of Birth - 10/06/1983 Sex - Male Marital Status - Single Country: - India Telephone No. (Mob) - +99844829969 Present address - Venkatesh kattimani #28/29,23rdcross, 1st main road, Maruthinagar, Yelahanka,Bengalore-560064 Permanent Address - Venkatesh Kattimani S/O Sureshappa kattimani Marnal Tq:Yelburga Dist:Koppal E-mail ID - venkatesh.kattimani@gmail.com Languages Known - English, Kannada, and Hindi. I hereby declare that all the details furnished above are correct to my knowledge. 3 of 4

- 4. Date:- Place:- Venkatesh Kattimani 4 of 4