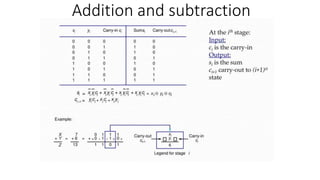

This document discusses addition, subtraction, and multiplication operations in a CPU. It describes the components involved like the ALU, registers, and control signals. It provides details on how specific instructions like addition, storing/fetching from memory, and a full instruction cycle are executed step-by-step through the control of signals within the CPU. Different types of control units like hardwired and microprogrammed control are also briefly mentioned.

![⦁ The ALU performs arithmetic operations on the 2

operands applied to its A and B inputs.

⦁ One of the operands is output of MUX;

⦁ The result (produced by the ALU) is stored temporarily in

register Z.

⦁ The sequence of operations for [R3] [R1]+[R2] is as

follows:

1. R1out, Yin

2. R2out, SelectY, Add, Zin

3. Zout, R3in

⦁ Instruction execution proceeds as follows:

Step 1 --> Contents from register R1 are loaded into

register Y.

Step2 --> Contents from Y and from register R2 are

applied to the A and B inputs of ALU;

Addition is performed &

Result is stored in the Z register.

Step 3 --> The contents of Z register is stored in the R3

register.

⦁ The signals are activated for the duration of the clock cycle

corresponding to that step. All other signals are inactive.](https://image.slidesharecdn.com/module4-230606001536-f3a9f446/85/module-4-pptx-17-320.jpg)