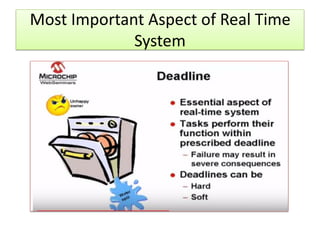

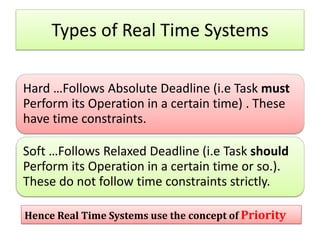

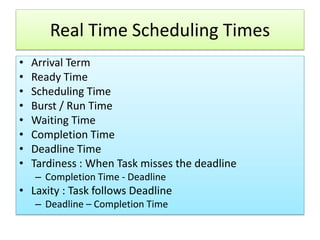

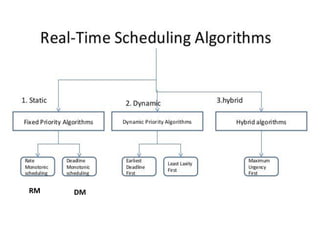

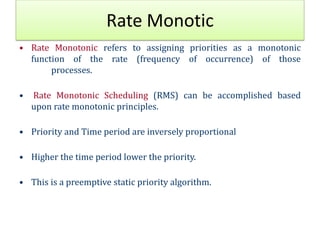

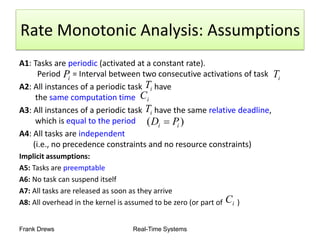

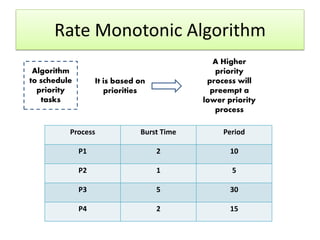

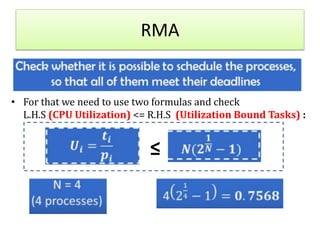

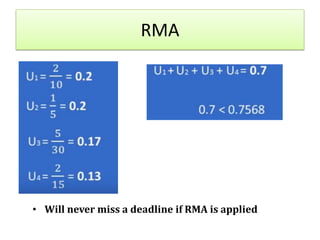

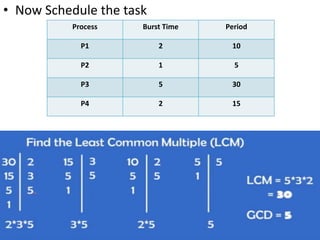

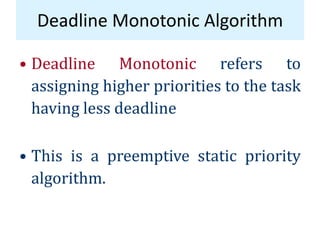

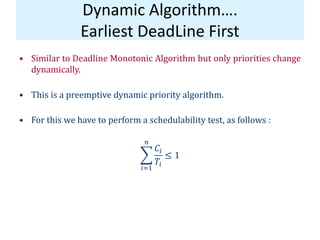

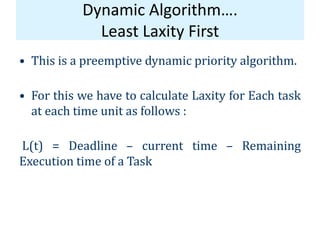

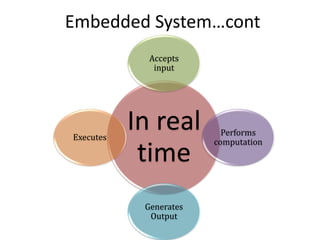

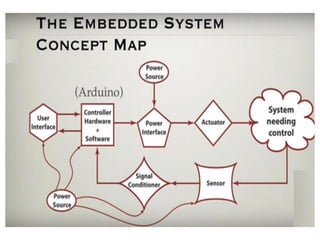

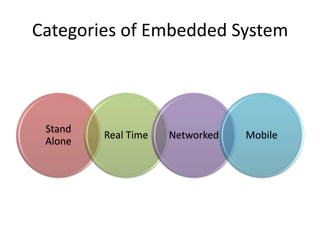

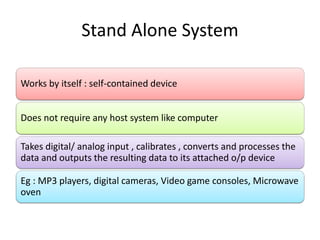

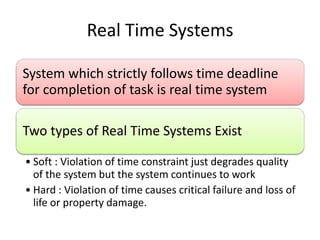

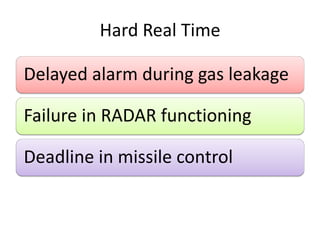

The document provides an introduction to embedded systems and Internet of Things. It discusses embedded systems, their characteristics, categories including stand-alone, real-time, networked and mobile systems. It also covers ARM processors, their architecture featuring RISC load/store architecture and features like reduced instruction set. Real-time scheduling algorithms like Rate Monotonic, Deadline Monotonic and dynamic algorithms like Earliest Deadline First, Least Laxity First are also summarized.

![ARM Architecture….Contd[2]

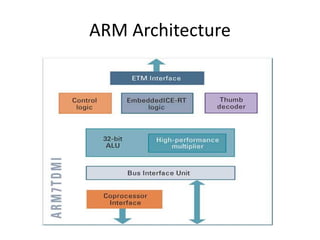

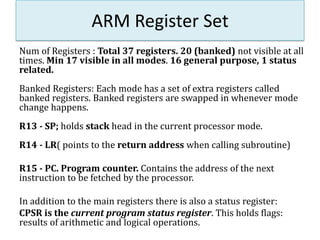

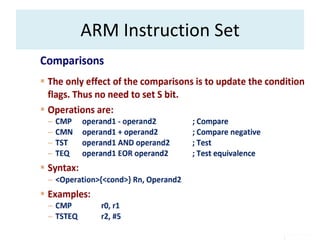

The main Features of ARM7 is,

• 32/16-bit RISC architecture.

• 32-bit ARM instruction set for maximum performance and

flexibility.

• 16-bit Thumb instruction set for increased code density.

• Unified bus interface, 32-bit data bus carries both instructions and

data.

• Three-stage pipeline : FETCH, DECODE and EXECUTE.

• 32-bit ALU.

• Very small die size and low power consumption.

• Fully static operation.

• Coprocessor interface.

• Extensive debug facilities (Embedded ICE debug unit accessible via

JTAG interface unit) : that allows programs to be downloaded and

fully debugged in-system.](https://image.slidesharecdn.com/unit-ies-230829074703-fd9d97b3/85/Unit-I_ES-pdf-24-320.jpg)

![ARM Reference

[1] https:// www. computerhope.com /jargon /a/

arm.htm

[2]

https://www.pantechsolutions.net/microcontroller-

tutorials/getting-started-with-arm-architecture

[3]

http://users.ece.utexas.edu/~valvano/EE345M/Arm_E

E382N_4.pdf](https://image.slidesharecdn.com/unit-ies-230829074703-fd9d97b3/85/Unit-I_ES-pdf-39-320.jpg)