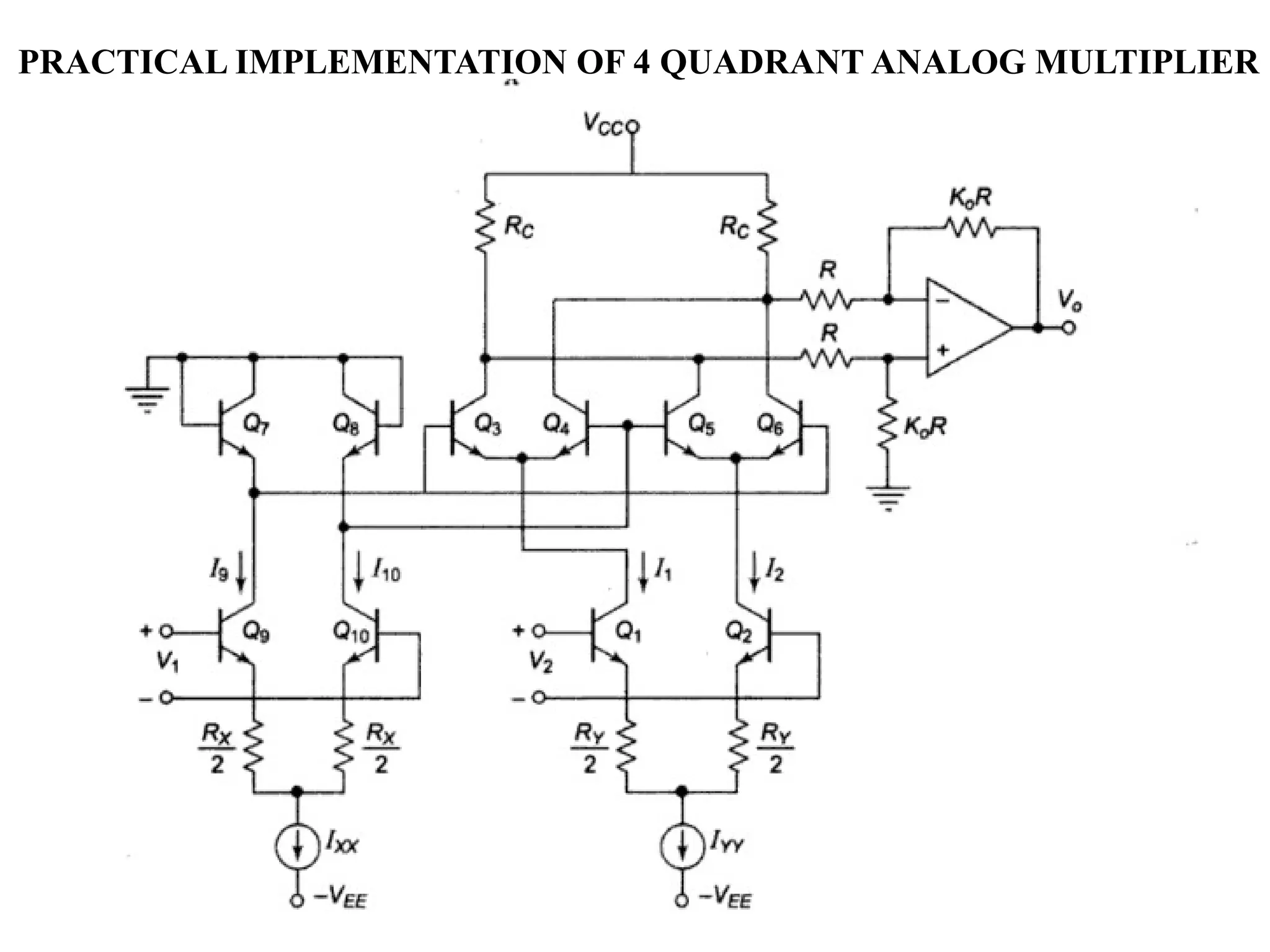

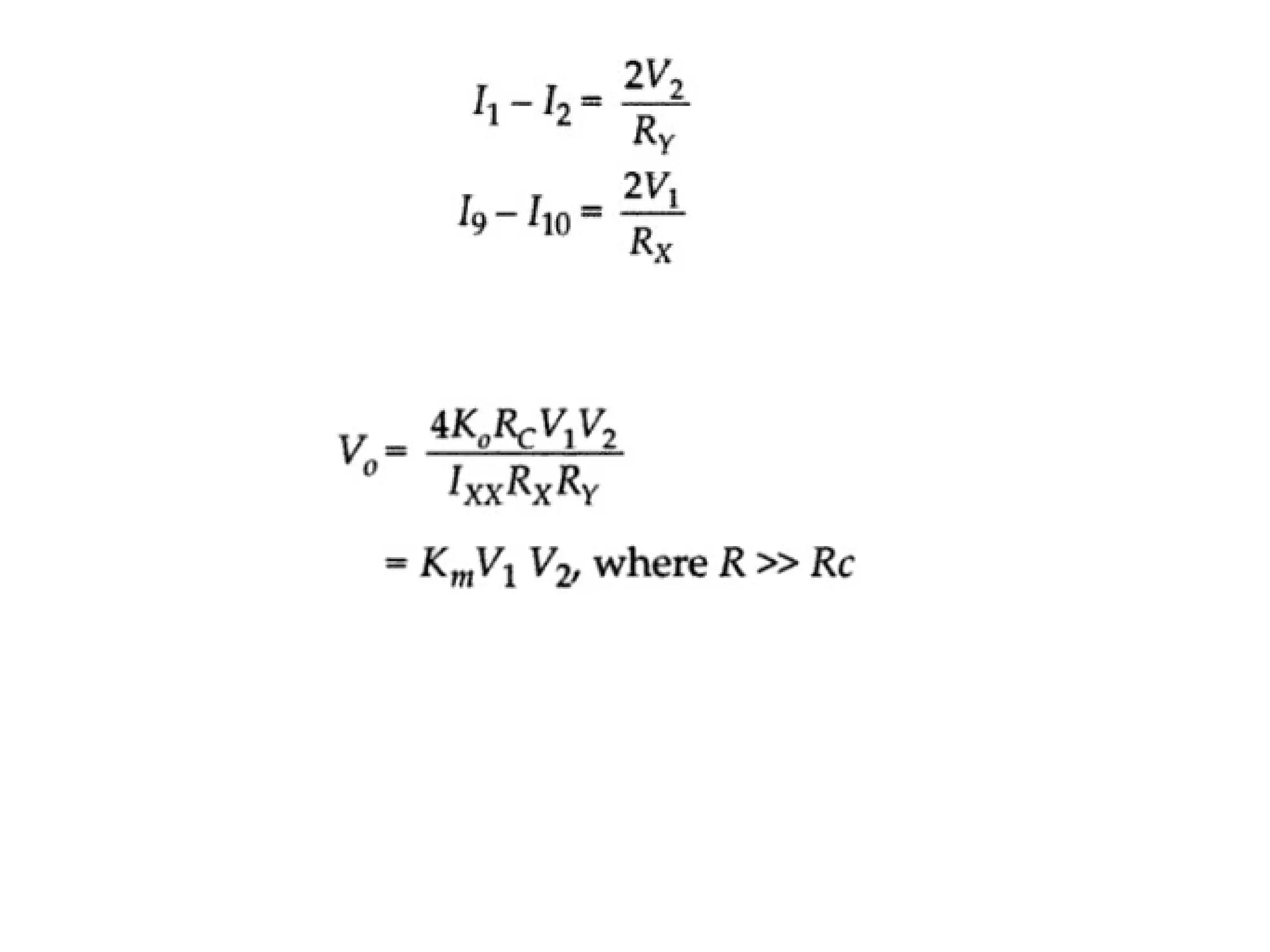

The document discusses the practical implementation of a four-quadrant analog multiplier using a variable transconductance technique that leverages the dependence of transistor transconductance on emitter current bias. It describes a differential circuit arrangement and how the multiplication of two input voltages occurs irrespective of their polarity. The circuit design incorporates compensation for nonlinearity to ensure a linear output proportional to the product of the input voltages.