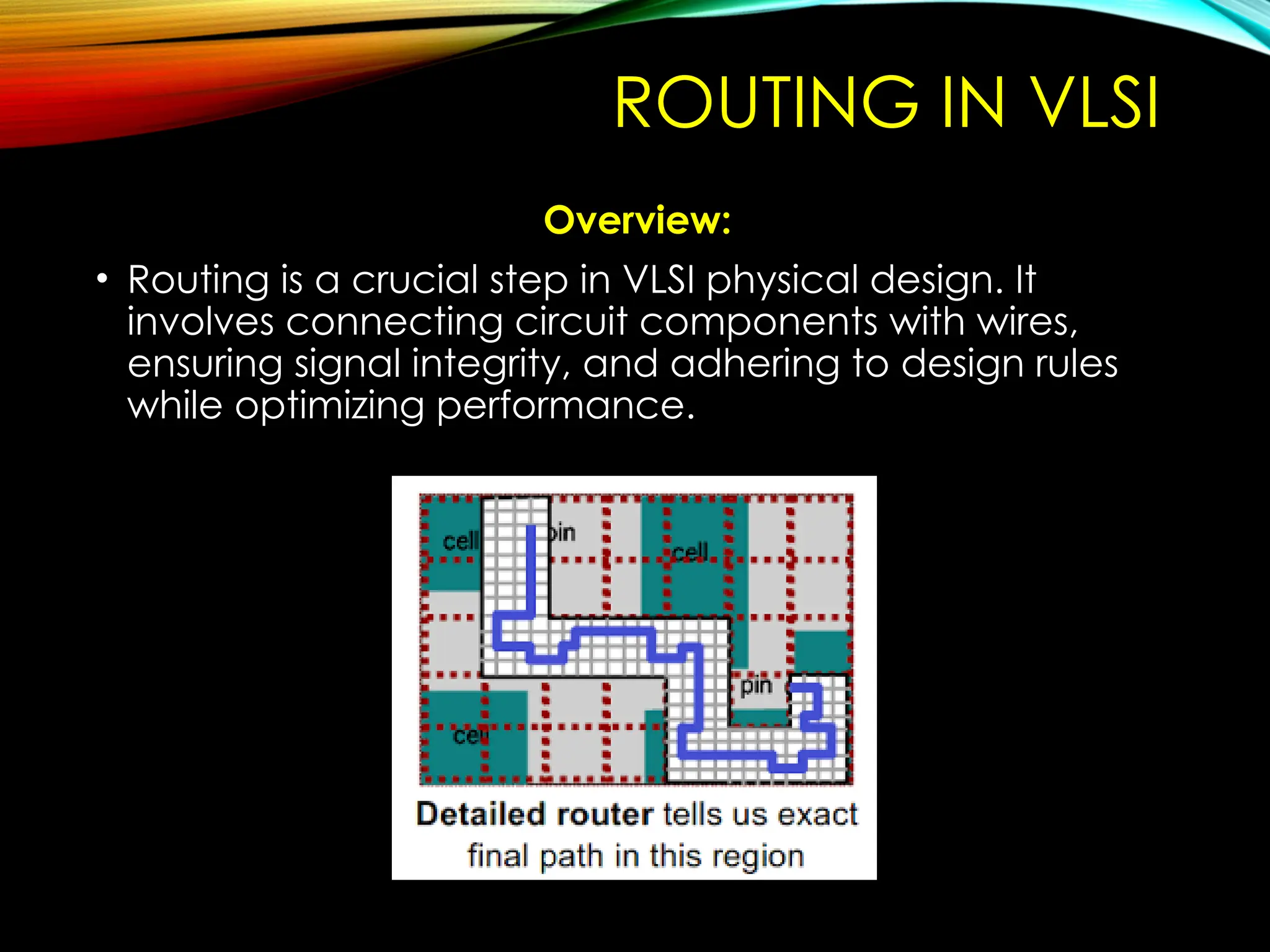

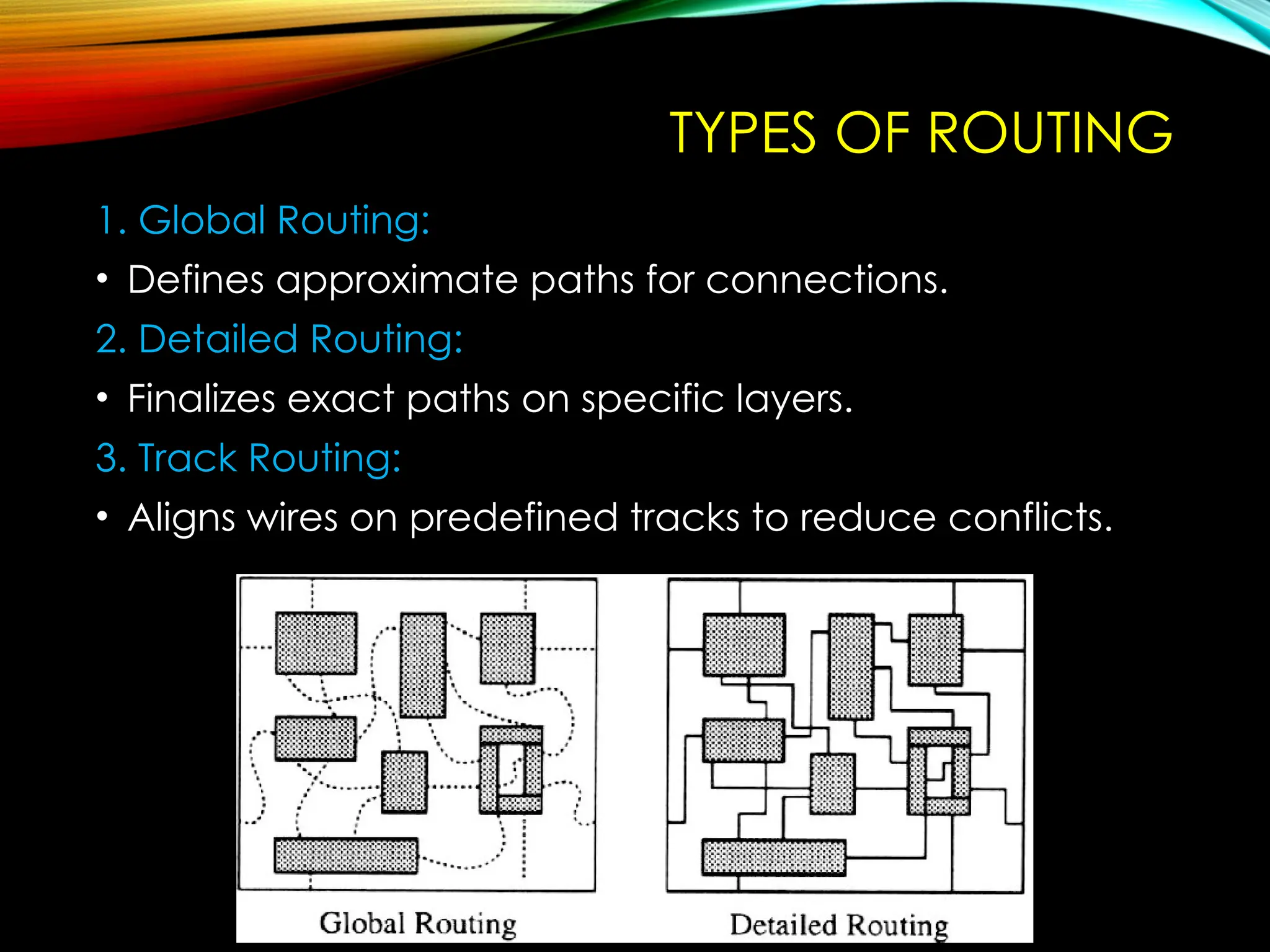

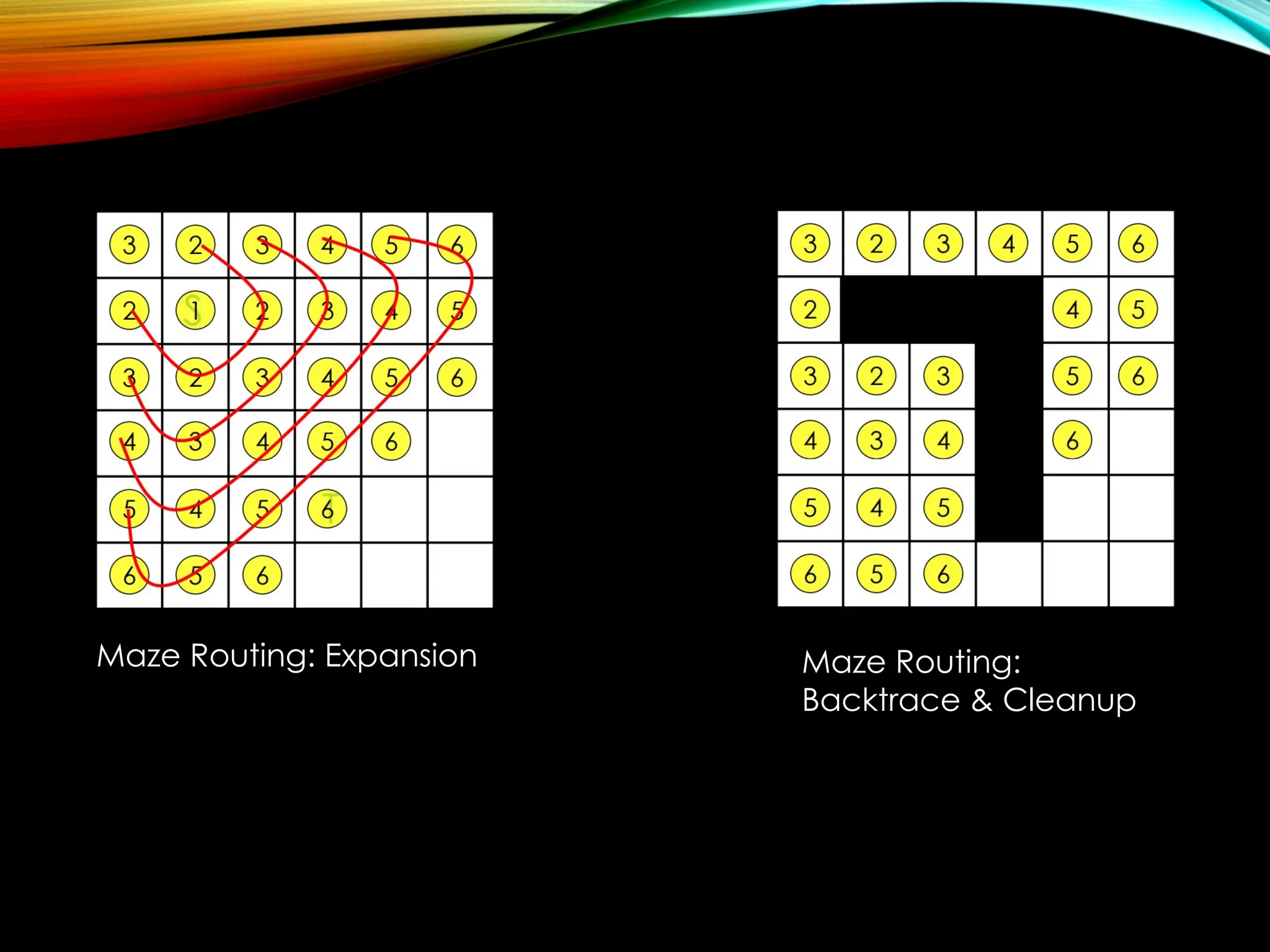

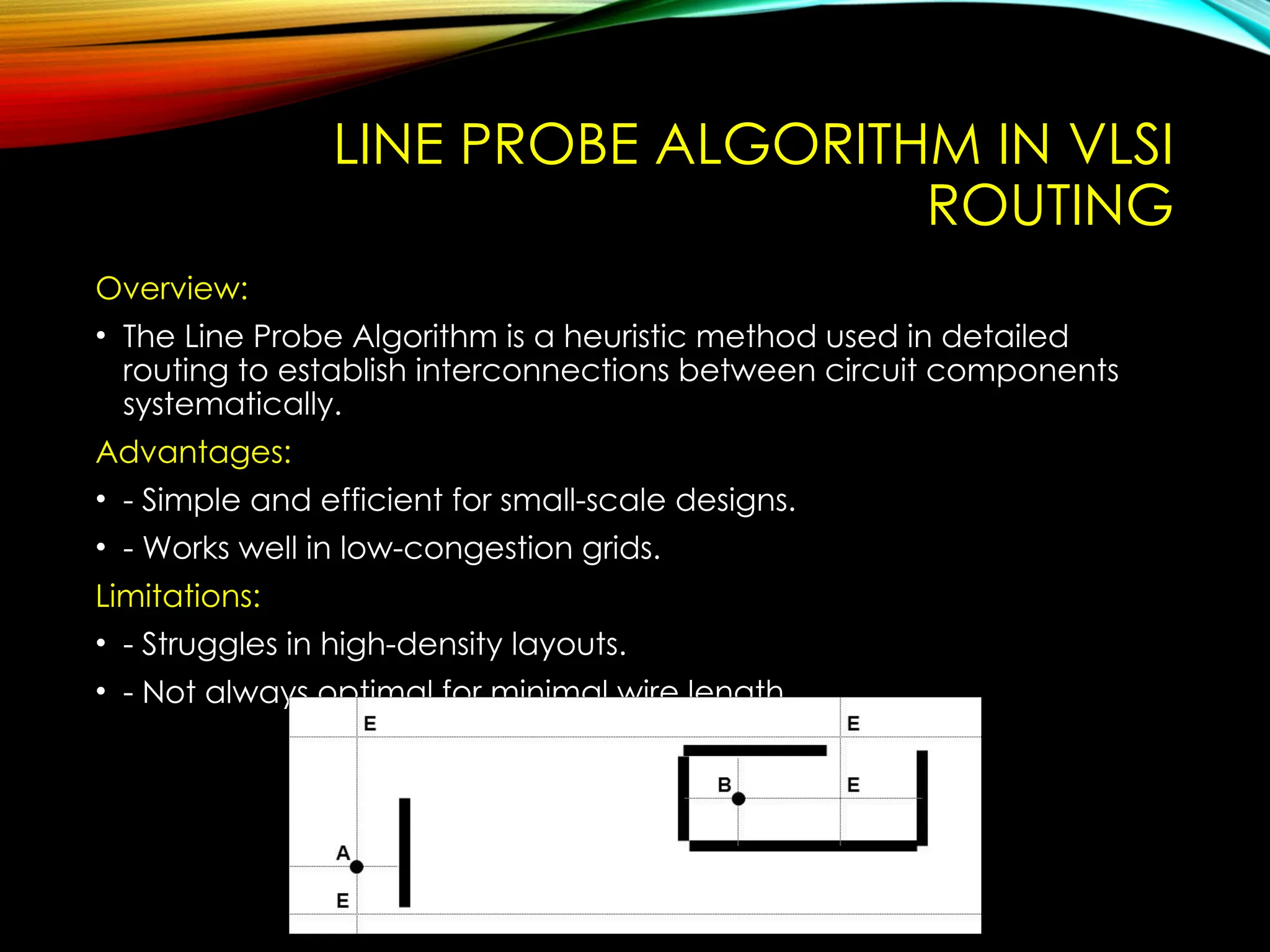

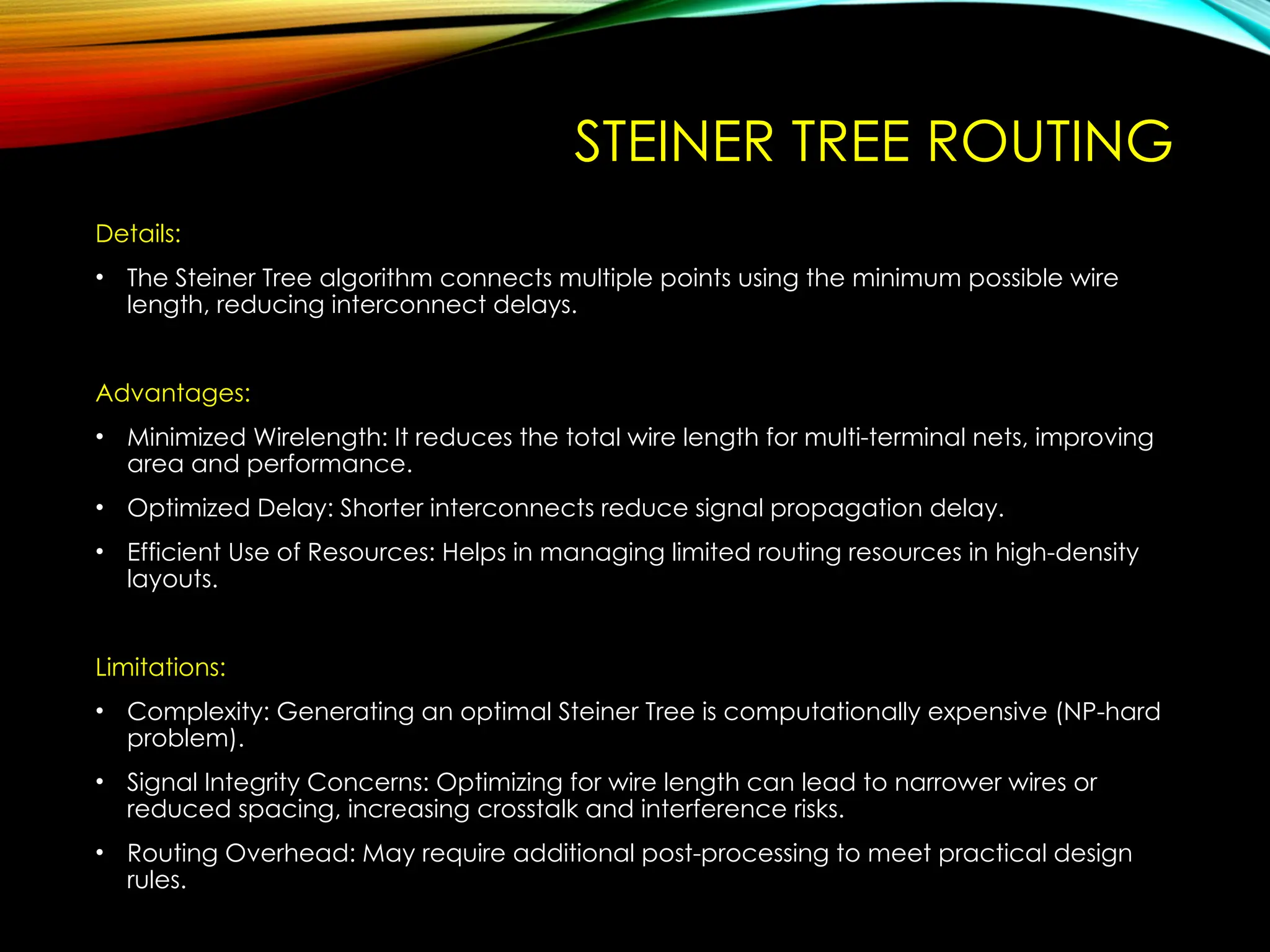

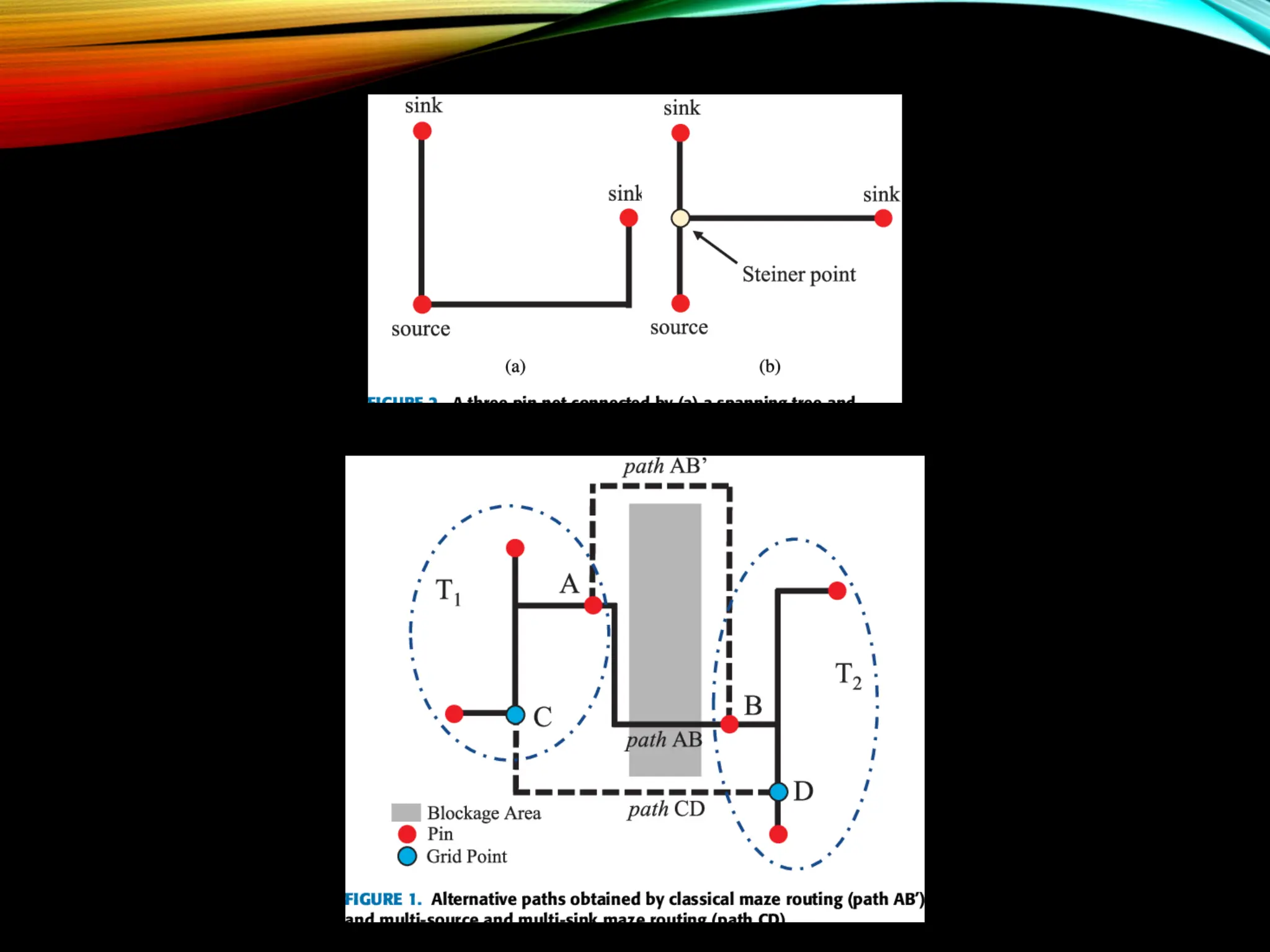

Routing in VLSI is essential for connecting circuit components, ensuring signal integrity while optimizing performance. It encompasses global, detailed, and track routing, facing challenges such as congestion and timing issues. Advanced techniques like maze routing and the Steiner tree algorithm are critical for minimizing wire lengths and delays, while emerging trends point towards AI-driven optimizations and new materials.