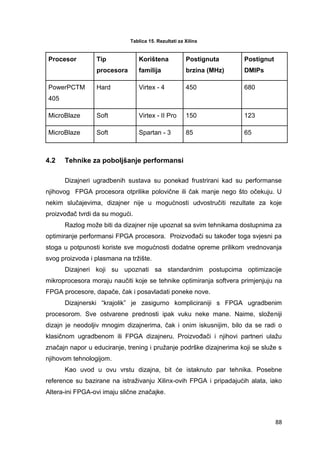

Ovaj diplomski rad proučava implementaciju procesora u FPGA sklopovima, s posebnim osvrtom na AVR jezgru s poboljšanom protočnom strukturom (PAVR). Dokument detaljno opisuje arhitekture procesora, specifikacije različitih inačica te analize performansi uz primjenu standardnih optimizacijskih tehnika. Rad se temelji na suradnji s Končar institutom za elektrotehniku i obuhvaća testiranje izvedenih rješenja u Xilinx alatima.

![100

6. Literatura

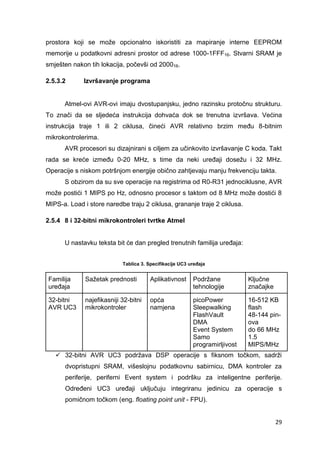

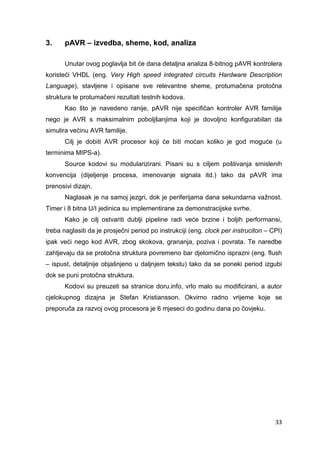

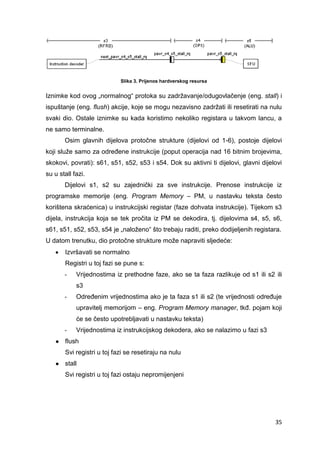

[1] Vučić M. , Molnar G.; Alati za razvoj digitalnih sustava – Materijali za

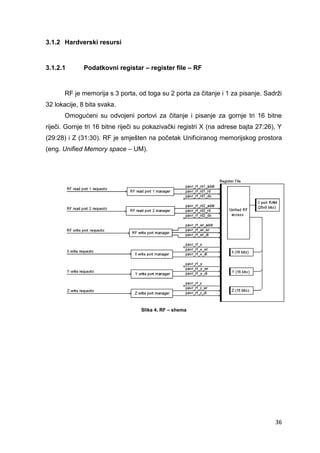

predavanja I, II, III; FER; 2010.

[2] Fletcher B. H. ; FPGA Embedded Processors: Revealing True System

Performance; Memec, San Diego, California; 2005.

[3] S interneta, http://www.1-core.com/resources/ , Third-party open-source

projects,

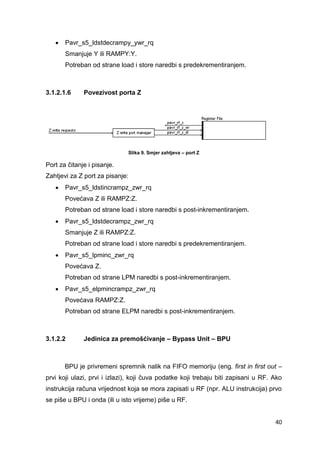

[4] S interneta, http://www.actel.com/products/ip/ ,

[5] S interneta, http://doru.info/projects/hdl/pavr/group__pavr__pavr.html

[6] S interneta,

http://support.atmel.no/knowledgebase/avrstudiohelp/mergedProjects/AVR

ASM/AVRASM.htm

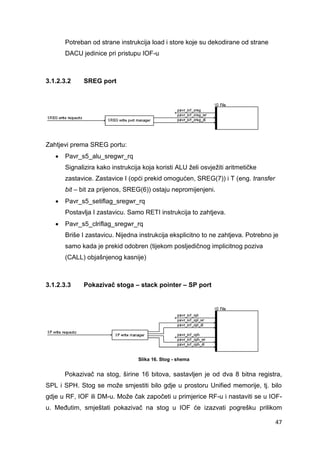

[7] S interneta, http://www.opencores.org/project,pavr](https://image.slidesharecdn.com/bf79d23a-4c9c-43cf-8288-7c50cb7e900b-161021073027/85/ProcFPGA_sklop_dzurovec-110-320.jpg)