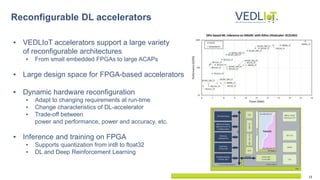

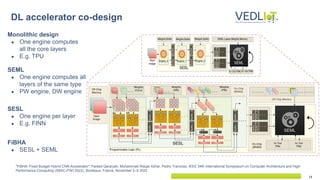

The document provides an overview of the VEDLIOT project focused on optimizing deep learning for the Internet of Things (IoT), detailing its hardware platform and standardization efforts. Coordinated by Bielefeld University, the project involves 12 partners and covers several use cases across industrial IoT, automotive, and smart home applications with a budget of approximately €8 million. It emphasizes the importance of a reconfigurable architecture for accelerators and compliance with regulatory constraints through its compositional architecture framework.

![9

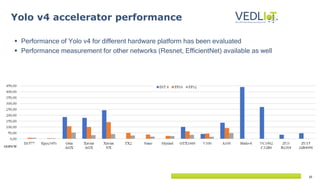

Peak performance values of specialized accelerators, provided by the vendors

(precisions varying from INT8 to FP32)

Peak Performance of DL Accelerators

Average efficiency at 1000 GOPS /W

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

[CELLRANGE]

1

10

100

1,000

10,000

100,000

1,000,000

10,000,000

0.01 0.1 1 10 100 1000

Performance

[GOPS]

Power [Watt]

ASIC

GPU

FPGA

Ultra Low Power

High Performance

Low Power](https://image.slidesharecdn.com/vedliotoverviewandstandards-240206111704-05523659/85/NGIoT-standardisation-workshops_Jens-Hagemeyer-presentation-9-320.jpg)