This presentation discusses the implementation of logic gates using NAND and NOR gates. It covers:

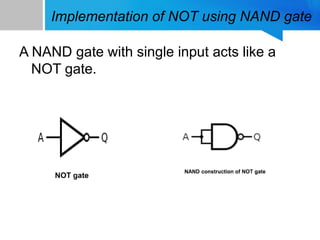

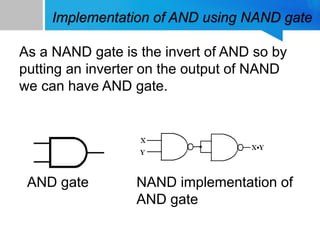

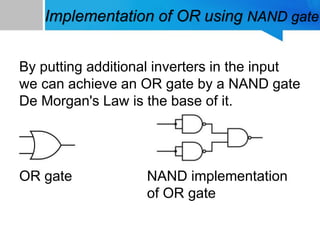

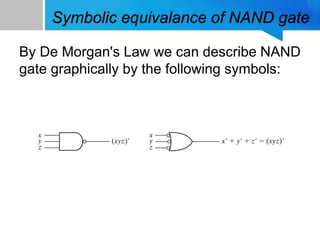

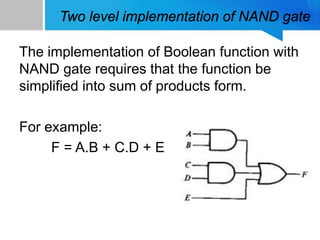

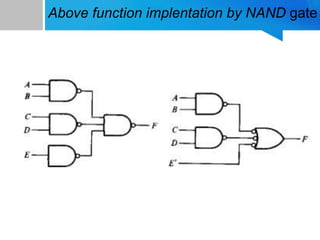

1) How to implement NOT, AND, and OR gates using only NAND gates by taking advantage of NAND gate properties and De Morgan's laws.

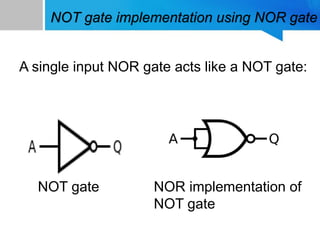

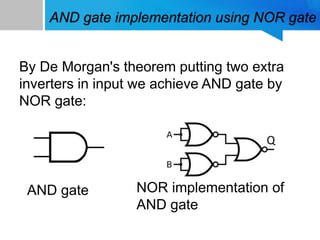

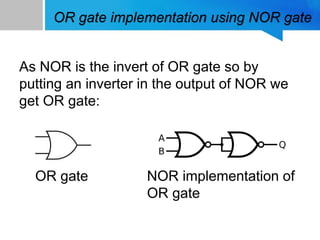

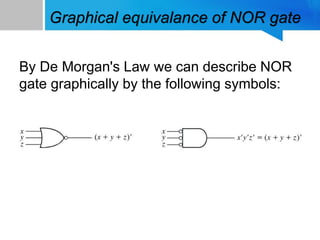

2) How to implement NOT, AND, and OR gates using only NOR gates in a similar manner.

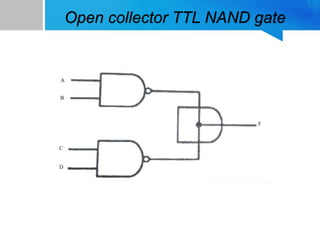

3) Wired logic implementations using open collector NAND gates and ECL NOR gates.

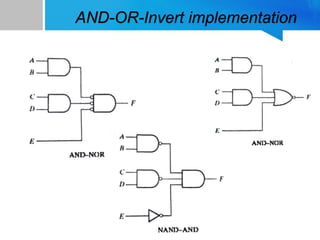

4) The eight non-degenerate two-level logic forms and examples of AND-OR Invert and OR-AND Invert implementations.

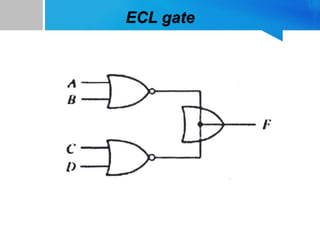

![ECL gate

• ECL stands for Emitter Coupled Logic

• The NOR outputs of the ECL gate are tied

together to perform a wired-OR function.

• The following logic implemented by the circuit is

called OR-AND-Invert function.

F = (A+B)'+(C+D)' = [(A+B).(C+D)]'](https://image.slidesharecdn.com/zubaid-170125173225/85/NAND-and-NOR-implementation-and-Other-two-level-implementation-24-320.jpg)

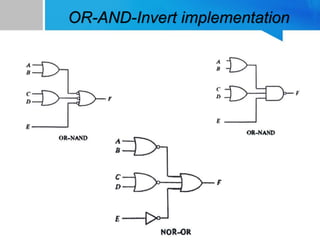

![OR-AND-Invert implementation

• The OR-NAND and NOR-OR forms are

equivalant.

• Both performs OR-AND-Invert function.

• OR-AND-Invert implementation requires the

expression in product of sums form.

• The following function is implemented:

F=[(A+B).(C+D).E]'](https://image.slidesharecdn.com/zubaid-170125173225/85/NAND-and-NOR-implementation-and-Other-two-level-implementation-30-320.jpg)