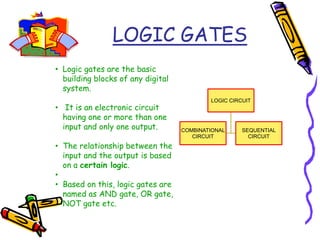

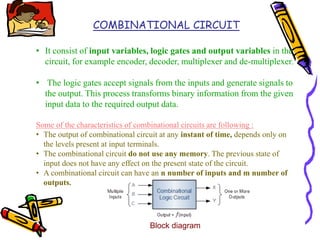

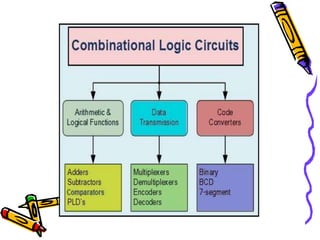

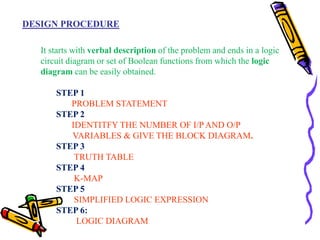

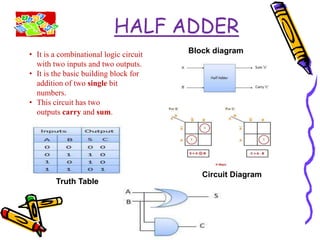

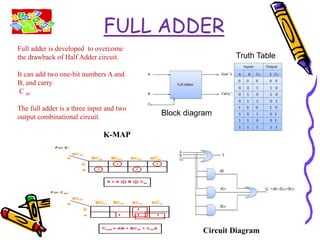

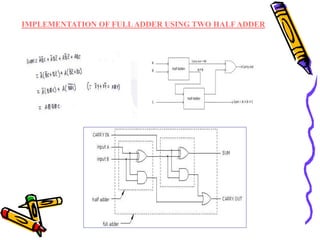

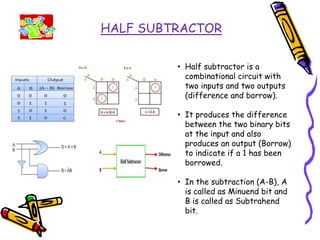

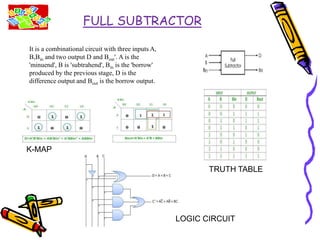

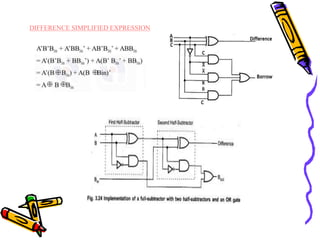

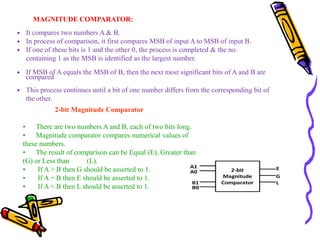

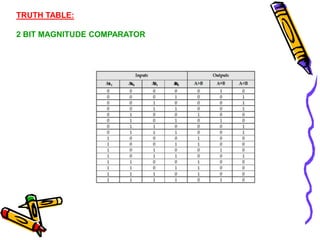

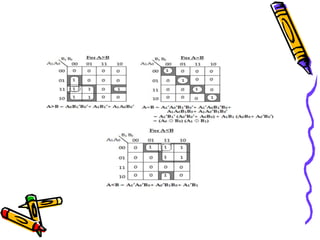

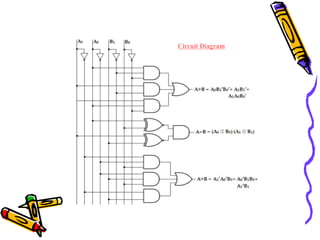

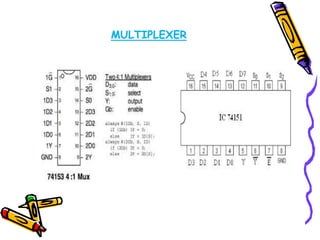

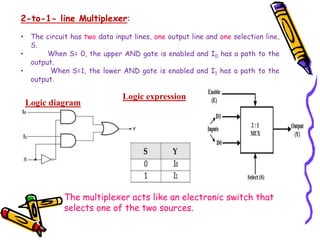

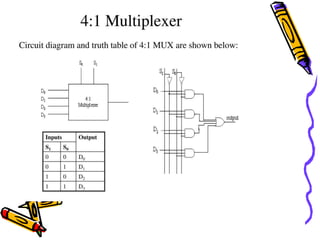

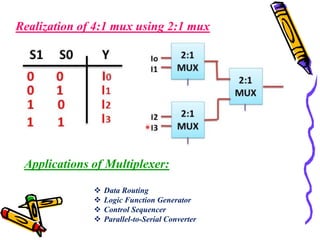

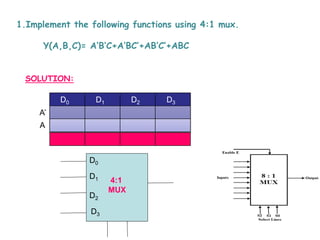

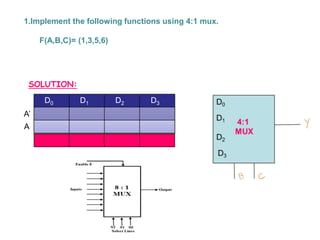

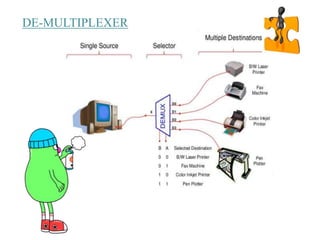

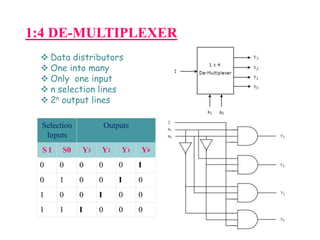

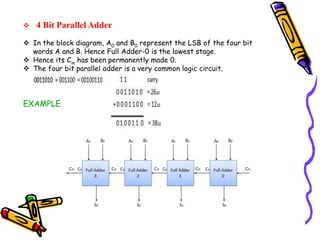

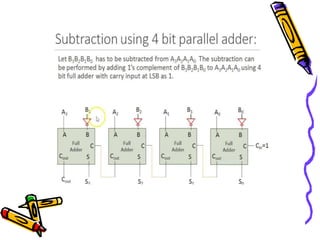

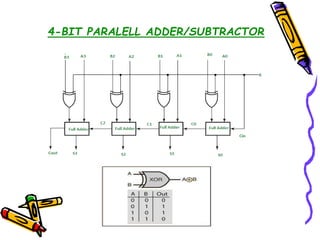

This document covers the fundamentals of digital electronics, specifically combinational circuit design, including components such as adders, subtractors, multiplexers, and comparators. It elaborates on the characteristics, applications, and design procedures for these circuits, highlighting their functional relationships and Boolean algebra. Key examples include the half adder, full adder, and various logic gates that operate without memory, relying solely on current input states.