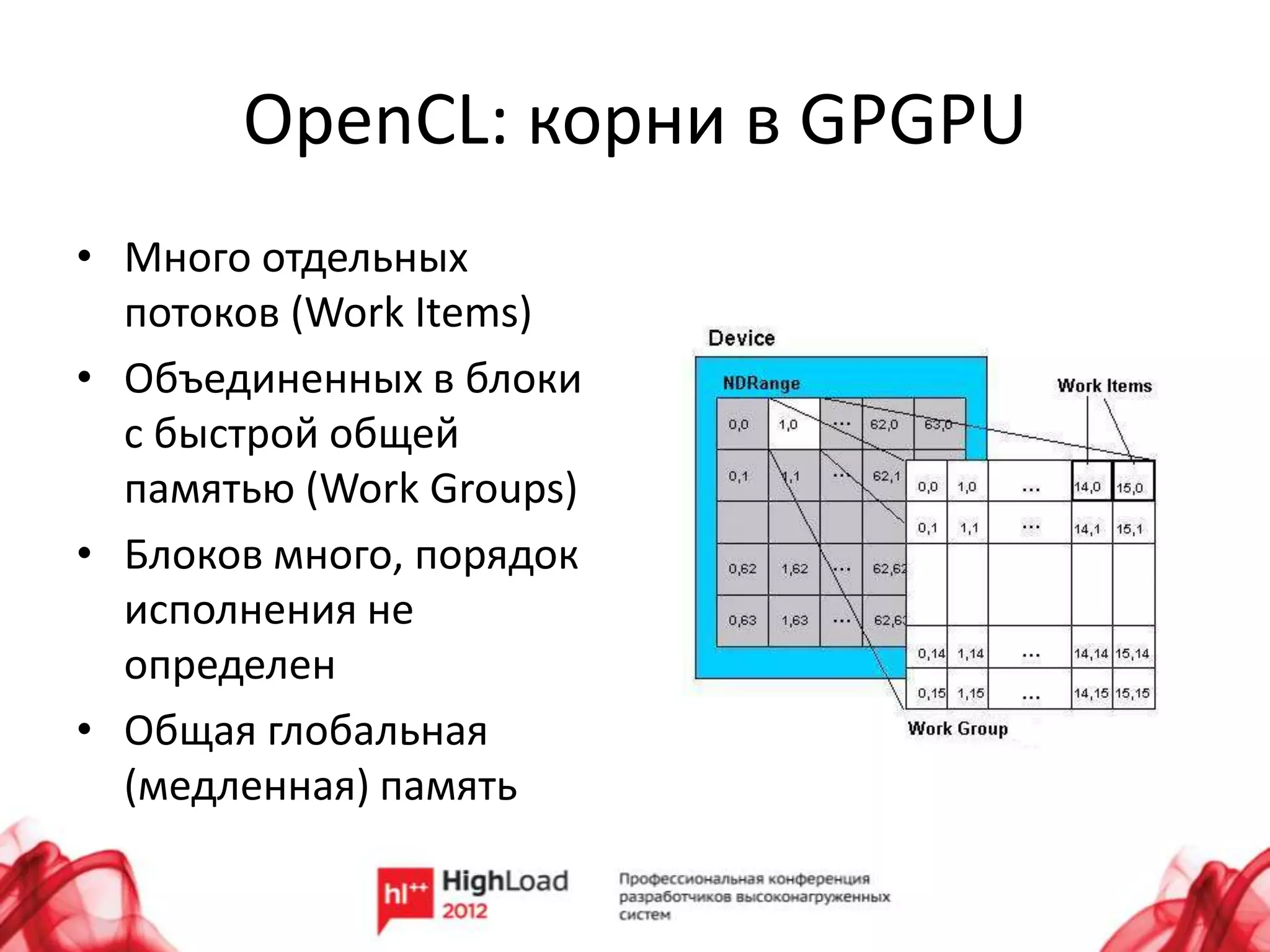

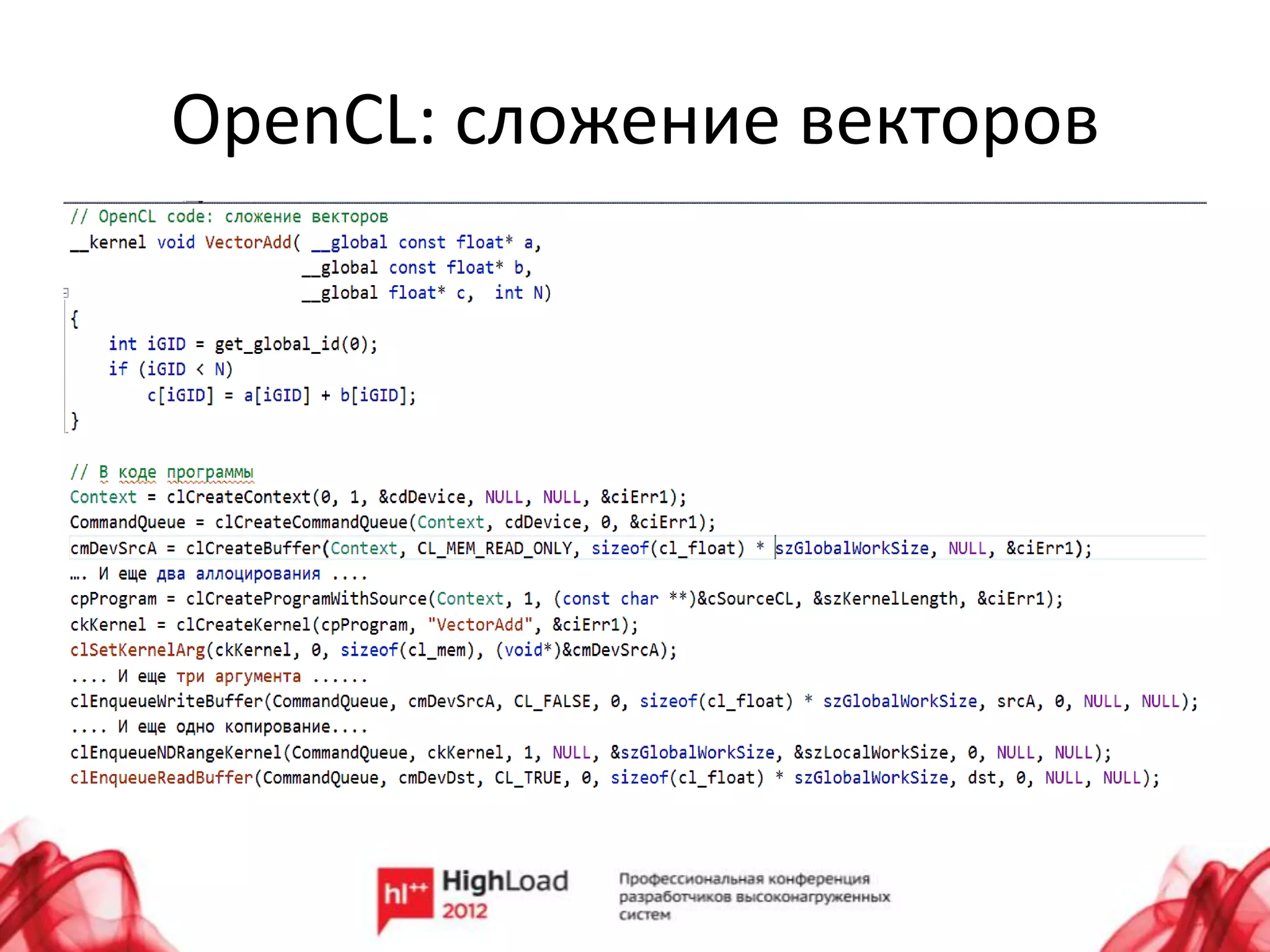

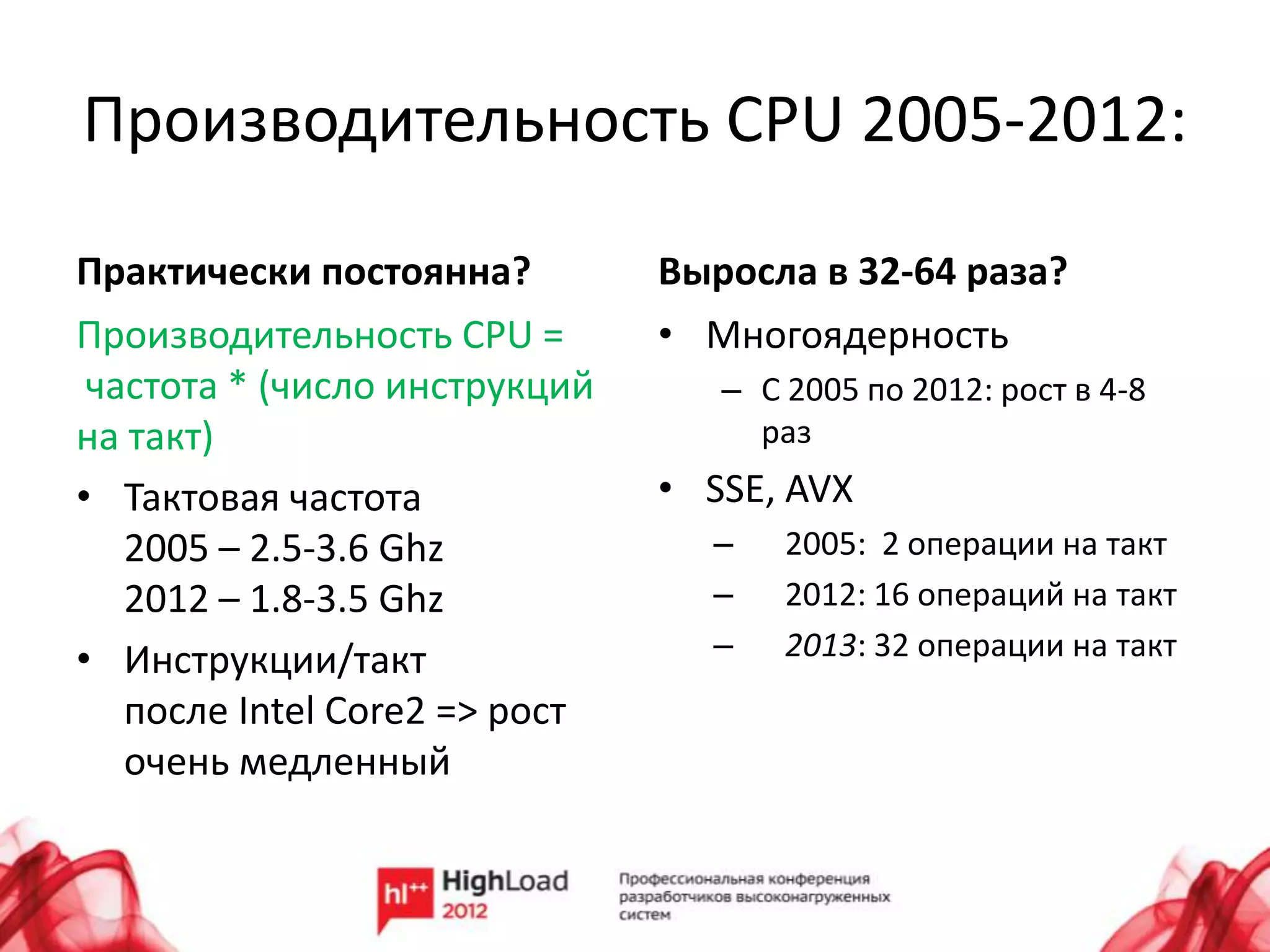

Документ обсуждает эффективное использование многоядерных процессоров и SIMD-расширений (SSE, AVX) для повышения производительности вычислений между 2005 и 2012 годами. Автор описывает различные техники параллелизма, векторизации и их влияние на производительность, а также проблемы, связанные с многопоточностью и оптимизацией кода. Документ также рассматривает альтернативные инструменты программирования для достижения более высокой эффективности, такие как OpenMP и ISPC.

![OpenMP

• Простой синтаксис: #pragma в

последовательном коде

#pragma omp parallel for

for(i=0;i<N;i++)

a[i] = b[i]+c[i];

• Возможности: reduction, atomics, critical

sections, режим доступа к переменным:

sum=0.0;

#pragma omp parallel for reduction(+:sum)

for(i=0;i<N;i++)

sum+=vector[i];](https://image.slidesharecdn.com/mailru20121101-121101132237-phpapp01/75/Mail-ru-01-11-12-6-2048.jpg)

![SSE/AVX: что это такое?

• SSE: одновременные операции

над 128-битными векторами

addps xmm0,xmm1

означает:

for(i=0;i<4;i++)

xmm0[i]+=xmm1[i];

• AVX: вектор 128 или 256 бит, 3-адресность:

vaddps ymm0,ymm1,ymm2

означает:

for(i=0;i<8;i++)

ymm0[i]=ymm1[i]+ymm2[i];](https://image.slidesharecdn.com/mailru20121101-121101132237-phpapp01/75/Mail-ru-01-11-12-11-2048.jpg)

![SSE/AVX: упаковка данных

Стандартный ООП-вариант Structure of Arrays (SoA)

Array Of Structures (AoS)

class foo_vector {

class foo {

vector<float> x,y,z;

float x,y,z;

};

void calc_z(){z=A*x+B*y;}

foo_vector::calc_z()

};

for(..) z[i]=A*x[i]+B*y[i];

vector<foo> fv(..);

for(…..) fv[i].calc_z();

calc_z() – хорошо векторизуется:

• for(..)calc_z() – плохо – 2 чтения

векторизуется: – 3 оп. арифметики

– 4-8 чтений – 1 запись

– 3 оп. арифметики

– 4 записи](https://image.slidesharecdn.com/mailru20121101-121101132237-phpapp01/75/Mail-ru-01-11-12-14-2048.jpg)

![С/C++: выравнивание

• Переменные и поля в структурах:

Gcc: int bar[64] __attribute_((aligned(16)));

MSVC:__declspec(align(16)) float baz[32];

• Простые аллокации:

– MSVC: _aligned_malloc(size, align)/_aligned_free()

– Gcc: _mm_malloc(size, align)/_mm_free()

• STL: выравнивающий аллокатор:

std::vector<T, AlignmentAllocator<T, 16> > foo;

Все элементы вектора выровнены на 16:

class __attribute__ ((aligned (16))) Foo {

__attribute__ ((aligned (16))) float bar[4];

};

std::vector<Foo, AlignmentAllocator<Foo, 16> > baz;

У последнего примера – проблемы с Microsoft STL (починено в VS2012)](https://image.slidesharecdn.com/mailru20121101-121101132237-phpapp01/75/Mail-ru-01-11-12-16-2048.jpg)

![Векторизация С/C++: алиасинг

Сложение двух векторов:

void sum_vec(float *s1,float *s2, float *d, int N){

for(int i=0;i<N;i++)

d[i] = s1[i]+ s2[i];

}

Вызов:

float A[SZ]; sum_vec(A,A+1,A+2,SZ-2);

Решение: restrict (C99), __restrict__(gcc C++), __restrict (MSVC):

void sum_vec(float * __restrict__ s1,

float* __restrict__ s2, float* __restrict__ d….

Но:

• Алиасинг бывает и на this

• В библиотечных классах – может не быть указан restrict](https://image.slidesharecdn.com/mailru20121101-121101132237-phpapp01/75/Mail-ru-01-11-12-19-2048.jpg)

![Compiler intrinsics: нудную работу

должен делать компилятор

Стандартные типы данных Макросы для команд

__m128

__m128 => SSE-регистр _mm_add_ps(__m128,__m128)

(float[4] или int16[8] или еще 6

вариантов) => addps (или vaddps)

Компилятор:

__m128d => double[2] • Распределяет регистры

• Подставляет адреса C-

Типы AVX-256: переменных

__m256 => float[8] • Генерирует код под целевую

архитектуру (SSE, AVX)

__m256d => double[4]

• Может переупорядочить

команды](https://image.slidesharecdn.com/mailru20121101-121101132237-phpapp01/75/Mail-ru-01-11-12-21-2048.jpg)