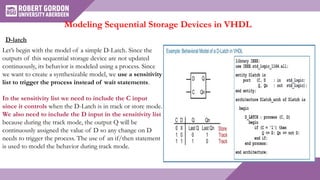

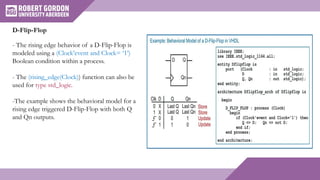

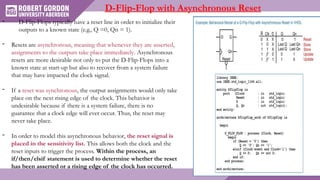

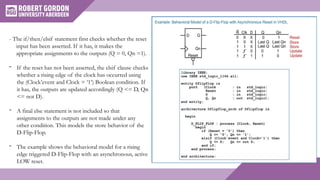

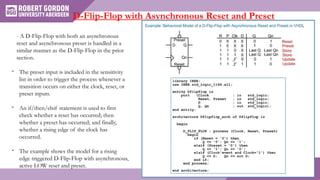

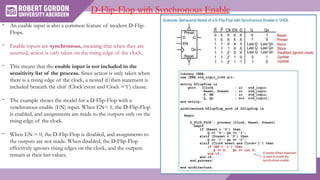

The document discusses the behavioral modeling of sequential logic devices using VHDL, focusing on various types of storage devices such as d-latches and d-flip-flops. It emphasizes the importance of using sensitivity lists for asynchronous resets and how to model behavior during different conditions including clock edges and reset states. The document also includes examples of synthesizable VHDL models to illustrate these concepts.