Embed presentation

Download to read offline

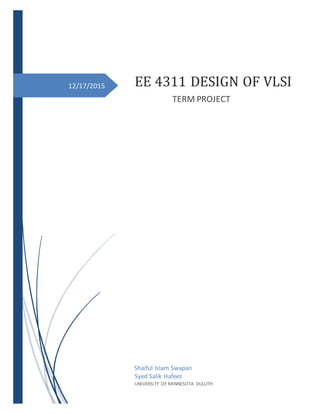

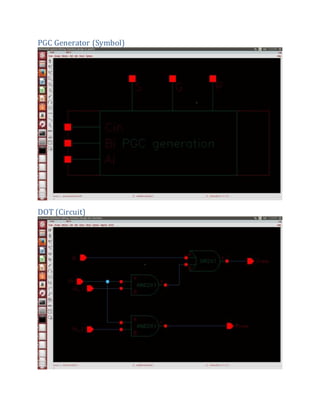

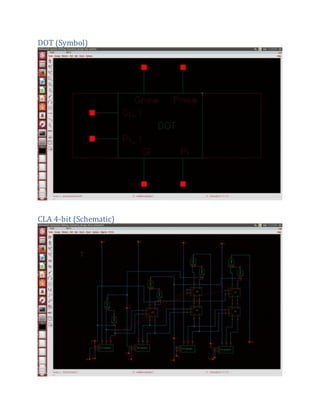

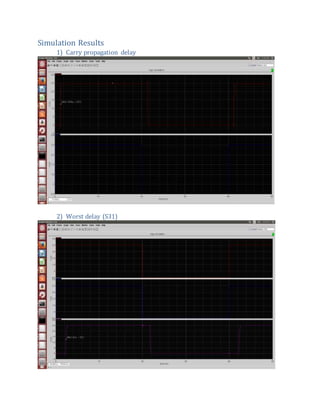

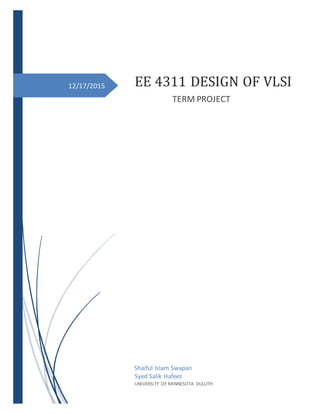

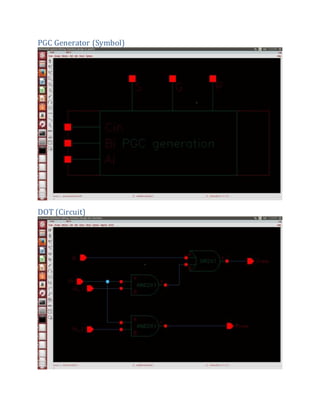

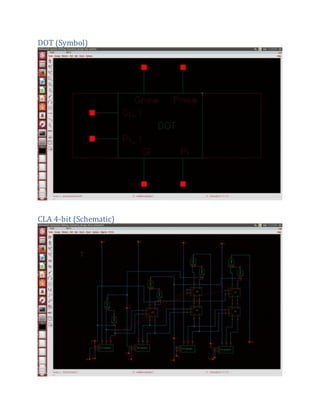

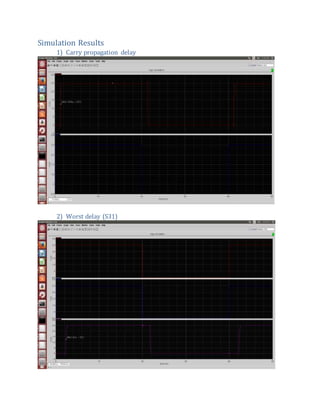

The document summarizes a term project on designing a carry lookahead adder in VLSI. It discusses carry lookahead adders which improve speed over ripple carry adders by reducing the time to determine carry bits. The project includes generating schematics and layouts for 4-bit, 16-bit, and 32-bit carry lookahead adders and verifying the layout against the schematic. Simulation results will analyze carry propagation delay and worst case delay.