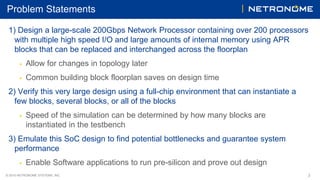

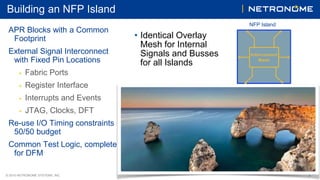

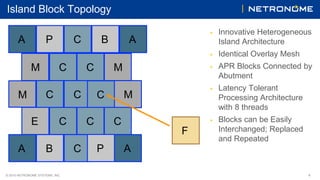

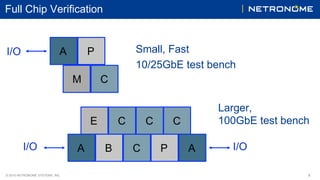

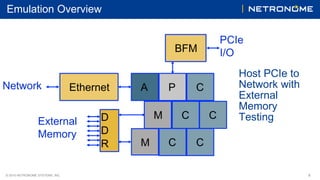

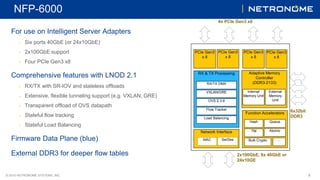

The document outlines the design, verification, and emulation of a 200Gbps network flow processor incorporating over 200 processors with high-speed I/O and significant internal memory. It discusses the creation of a full-chip test environment and an emulation setup aimed at analyzing bottlenecks and performance prior to silicon deployment. The architecture facilitates interchangeable APR blocks within a latency-tolerant processing framework, enhancing flexibility and efficiency in network processing.