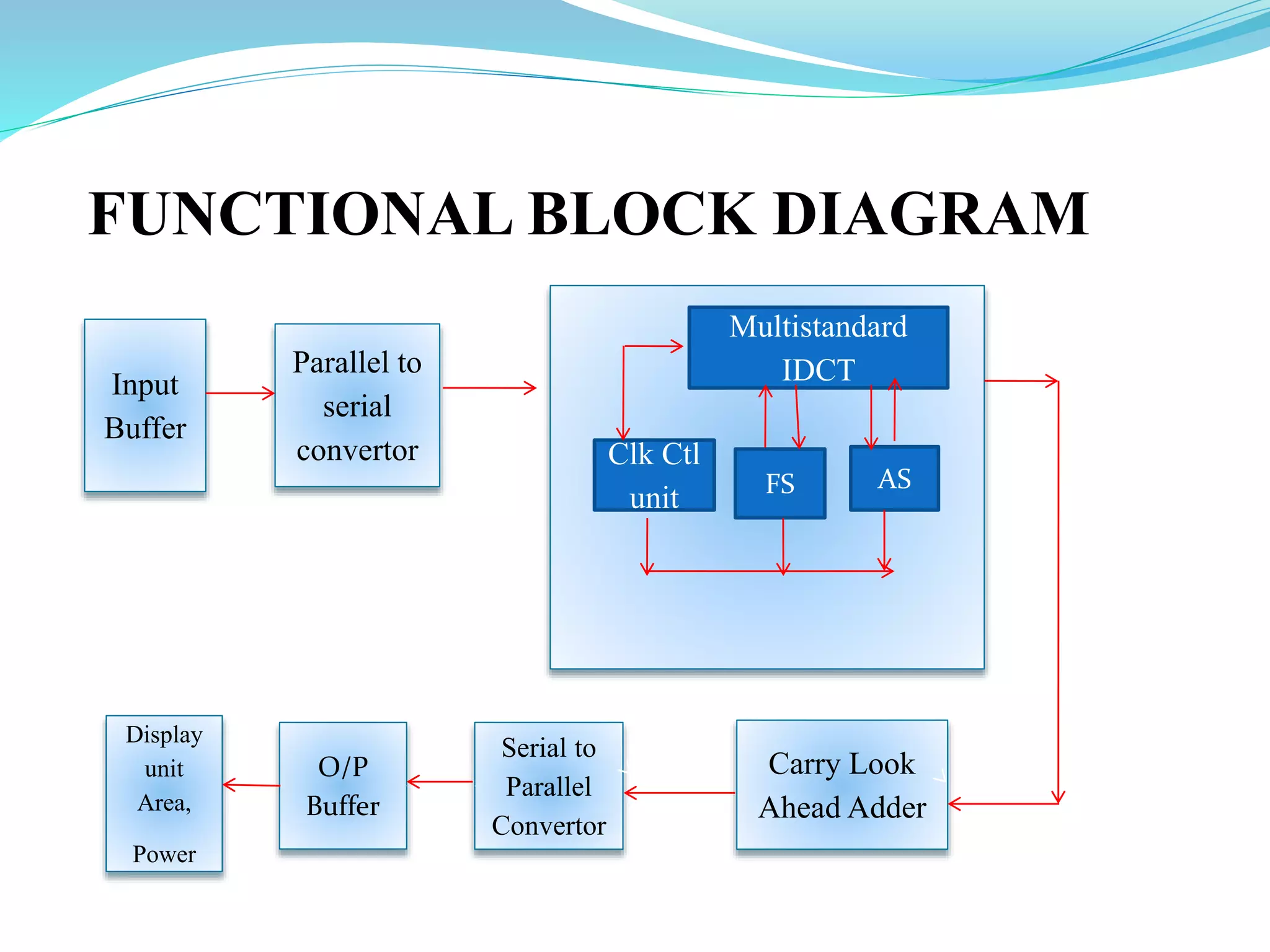

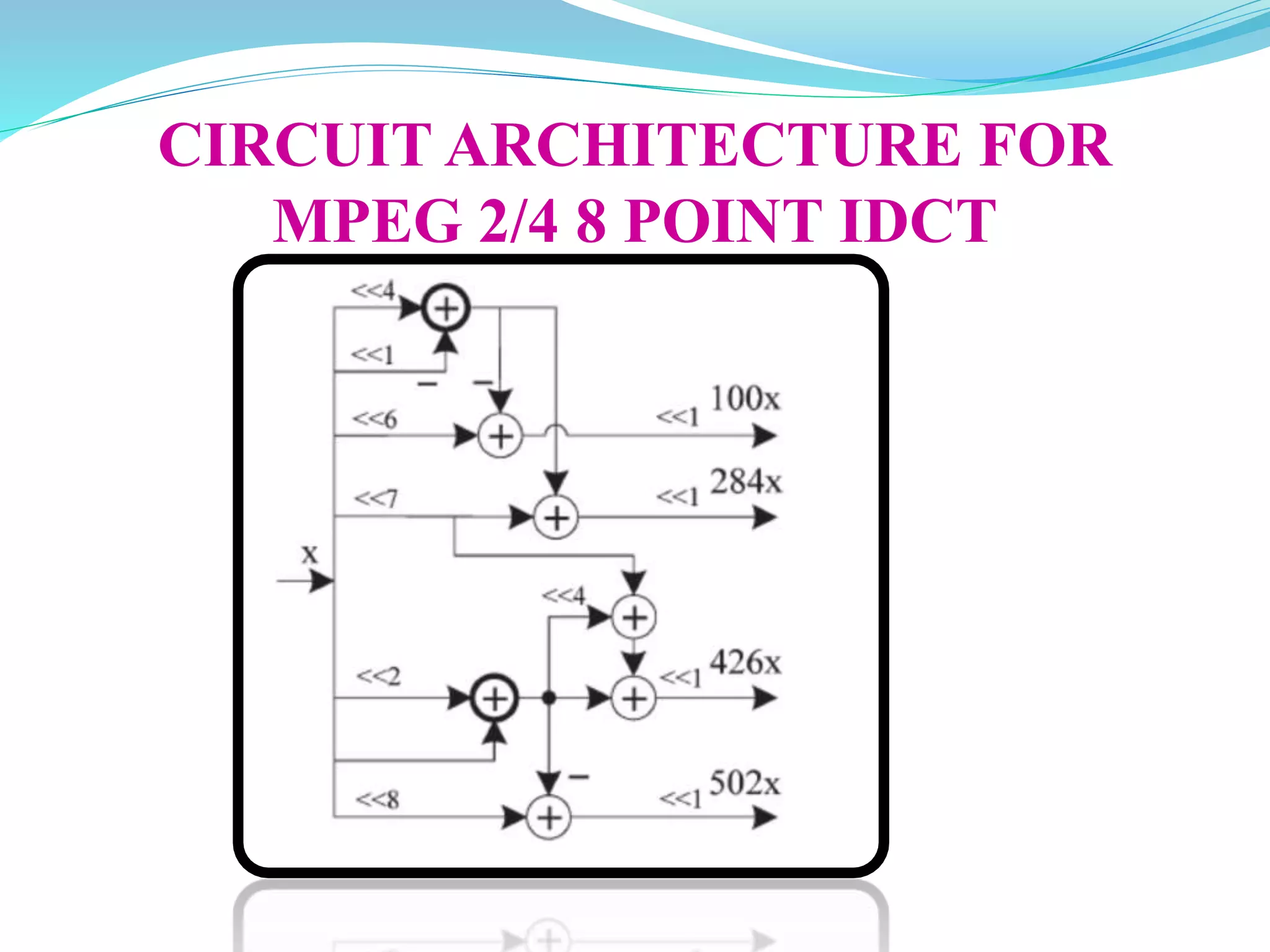

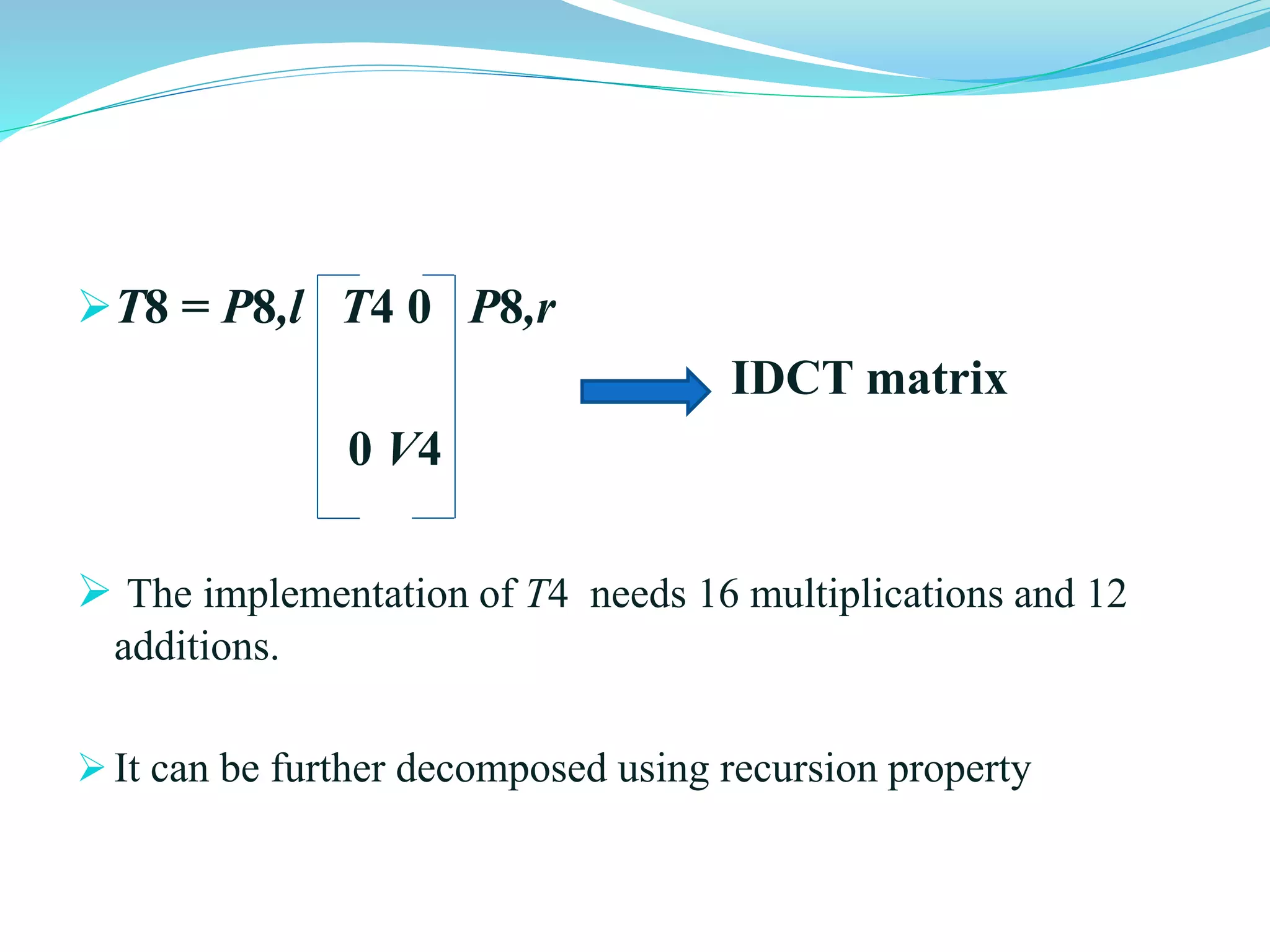

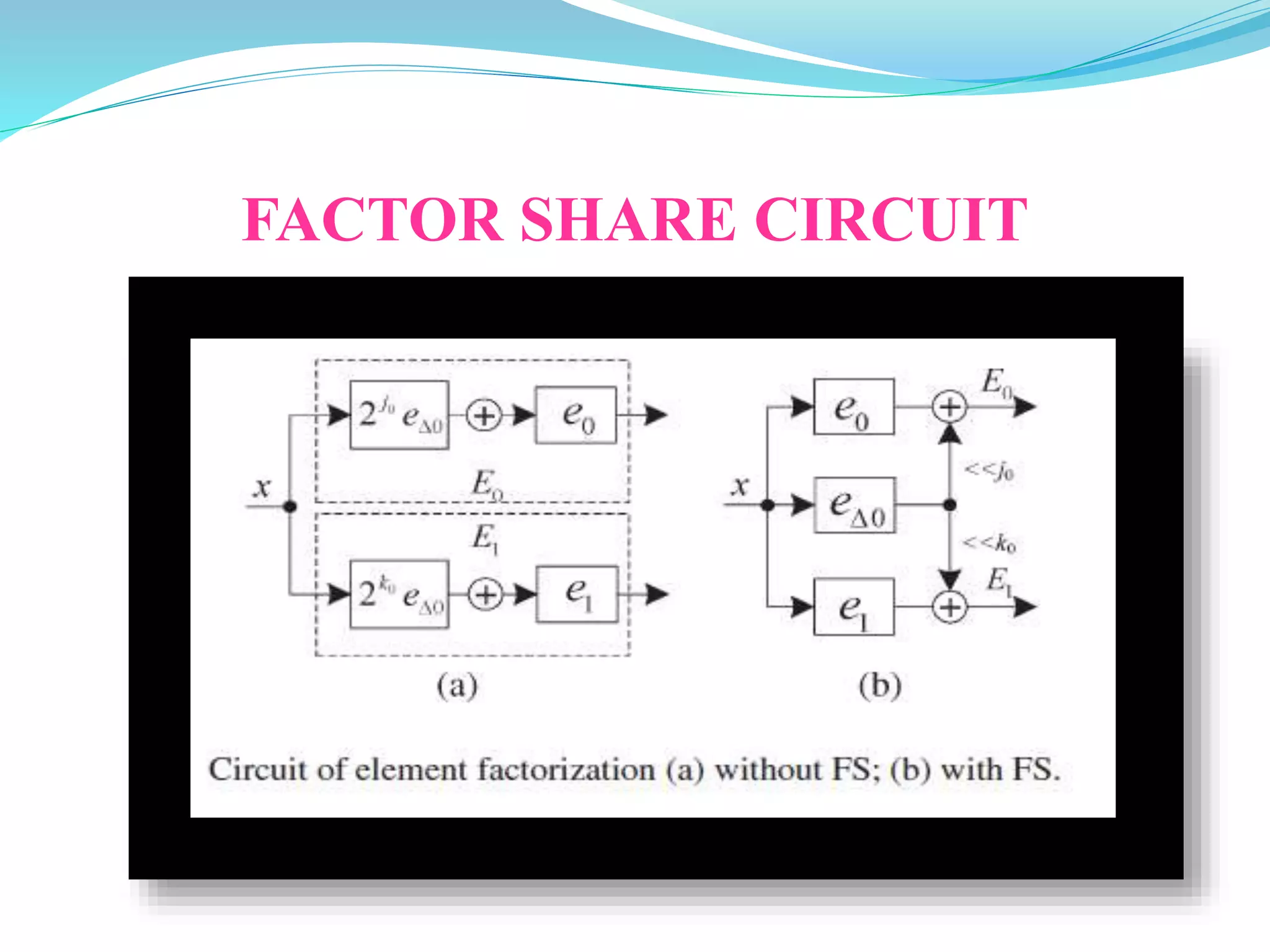

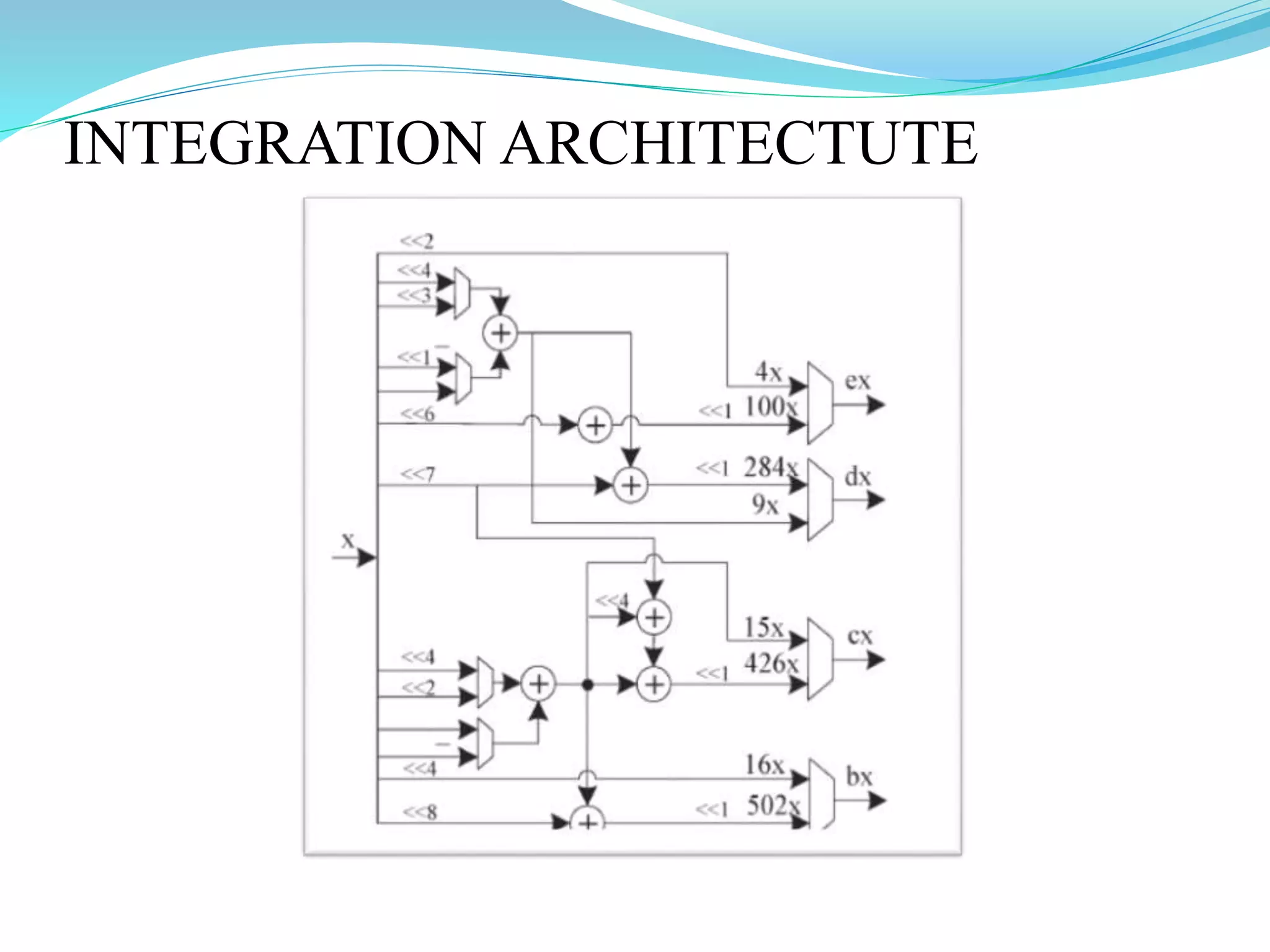

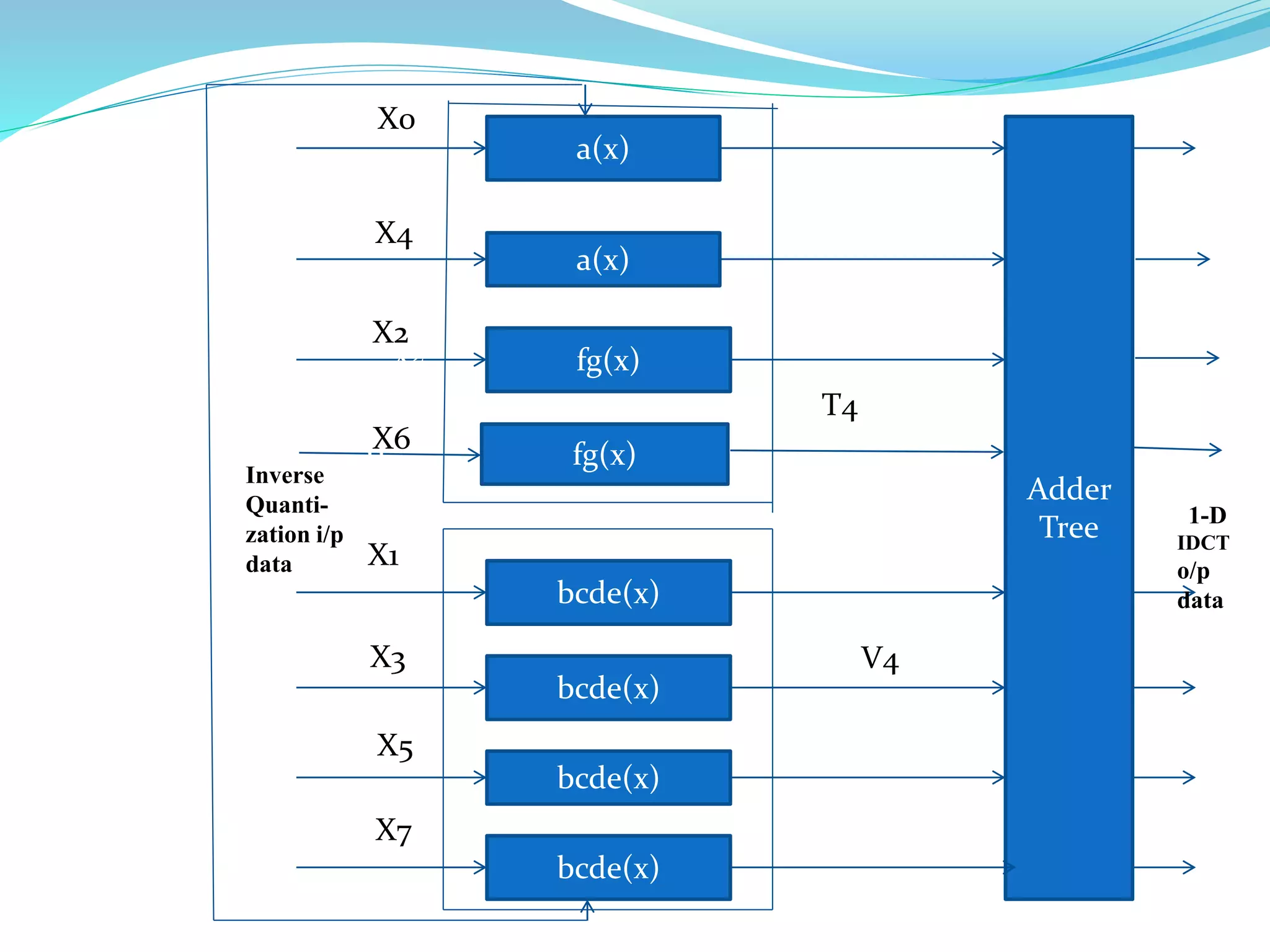

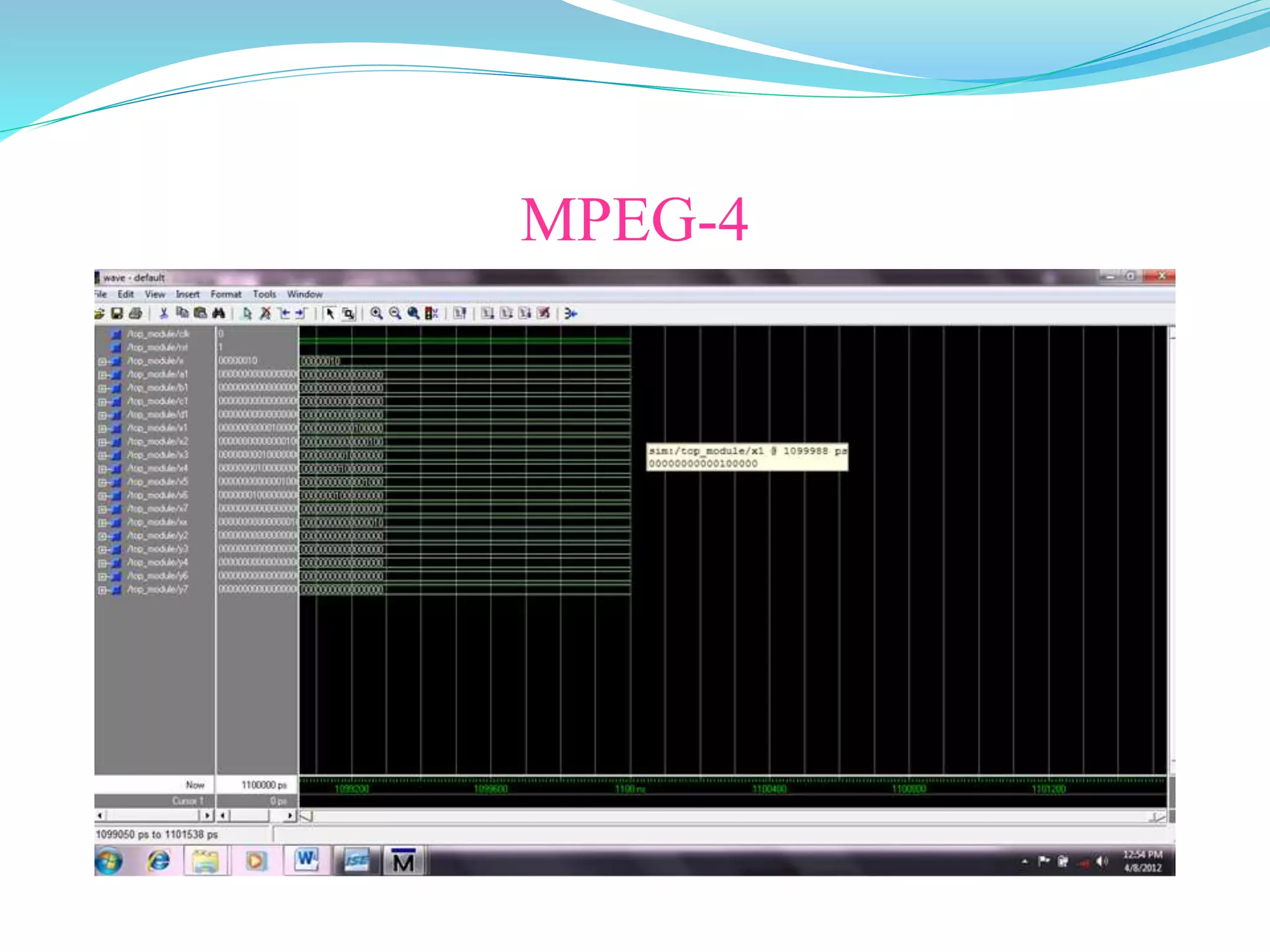

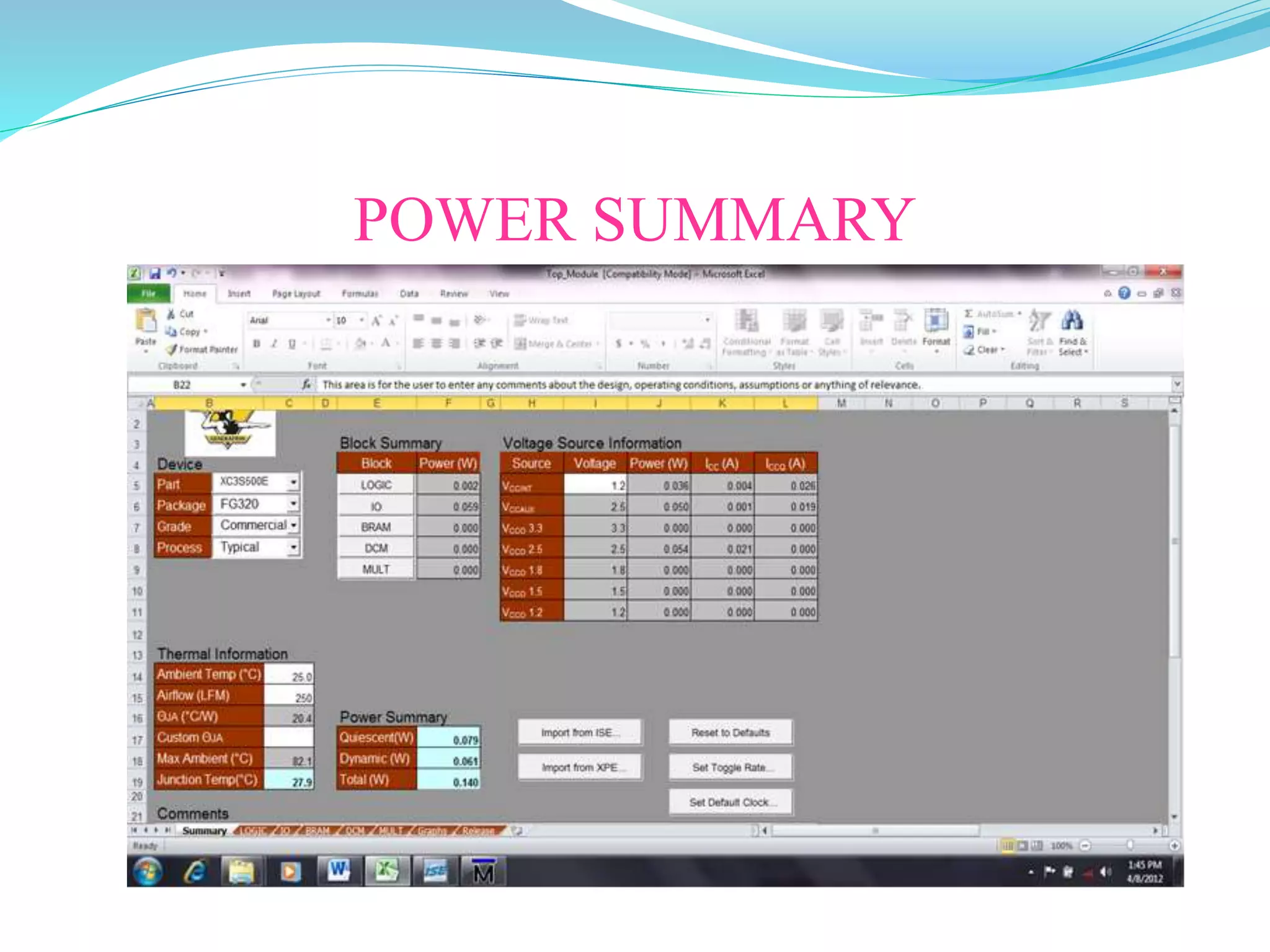

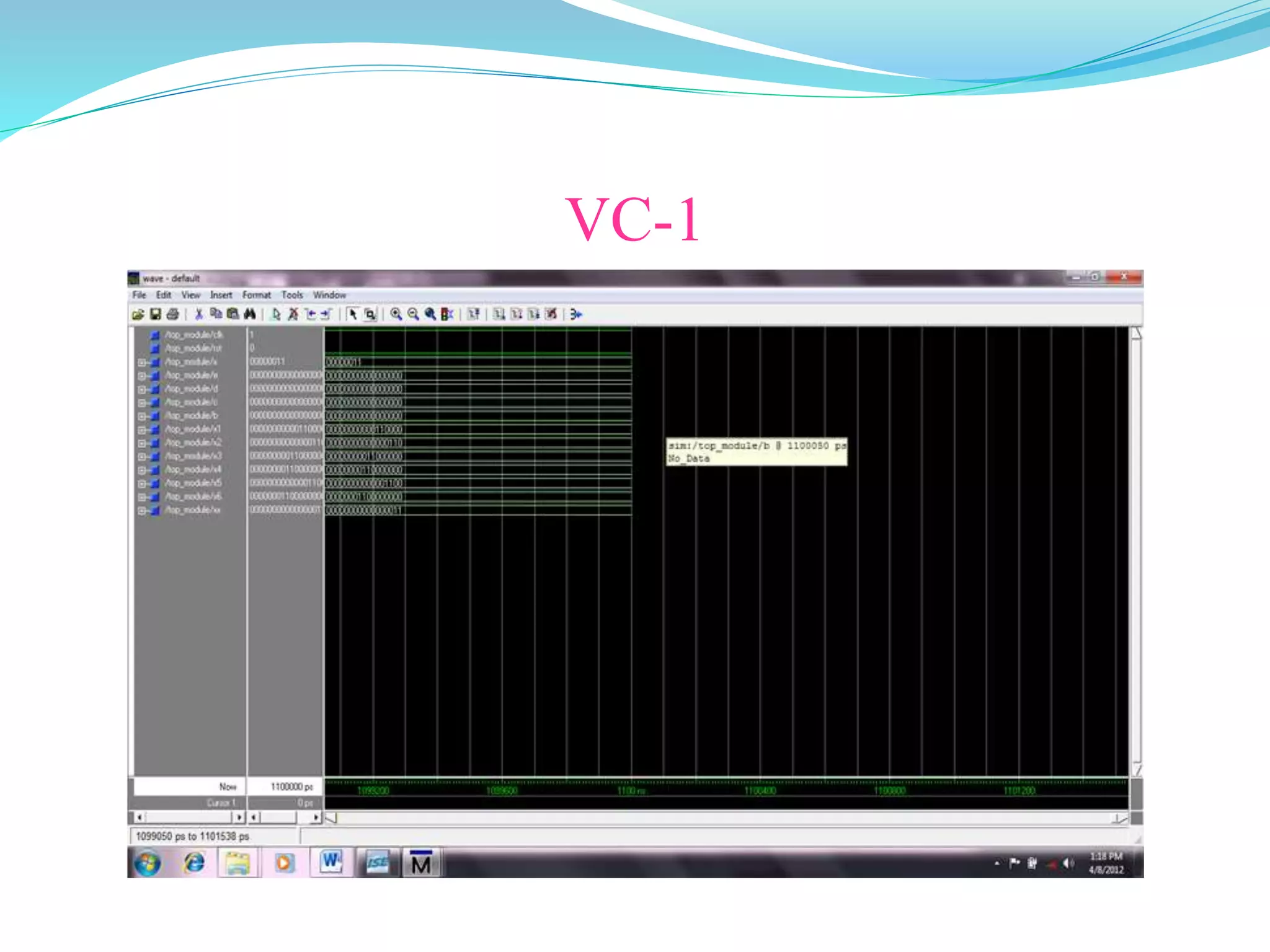

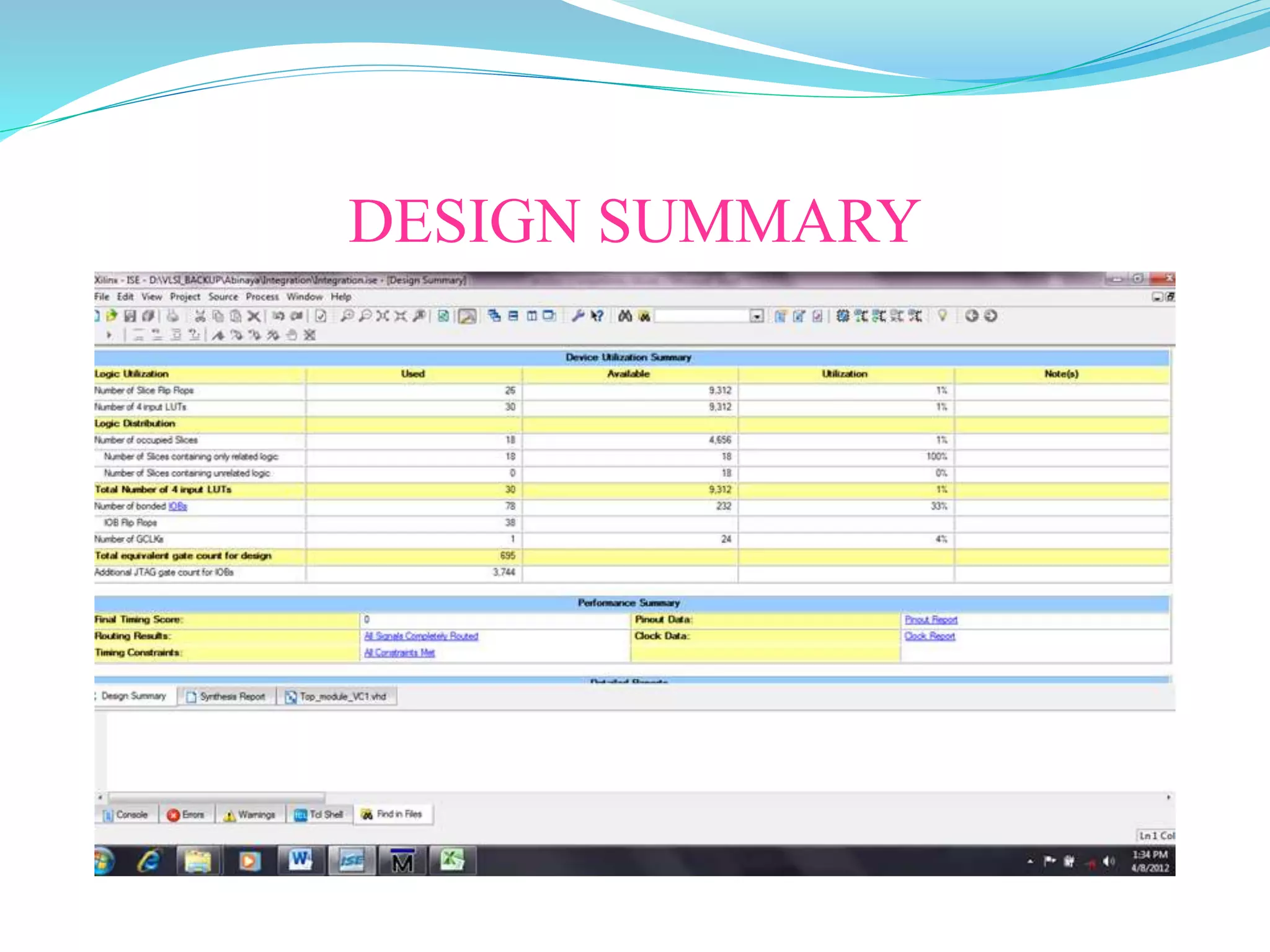

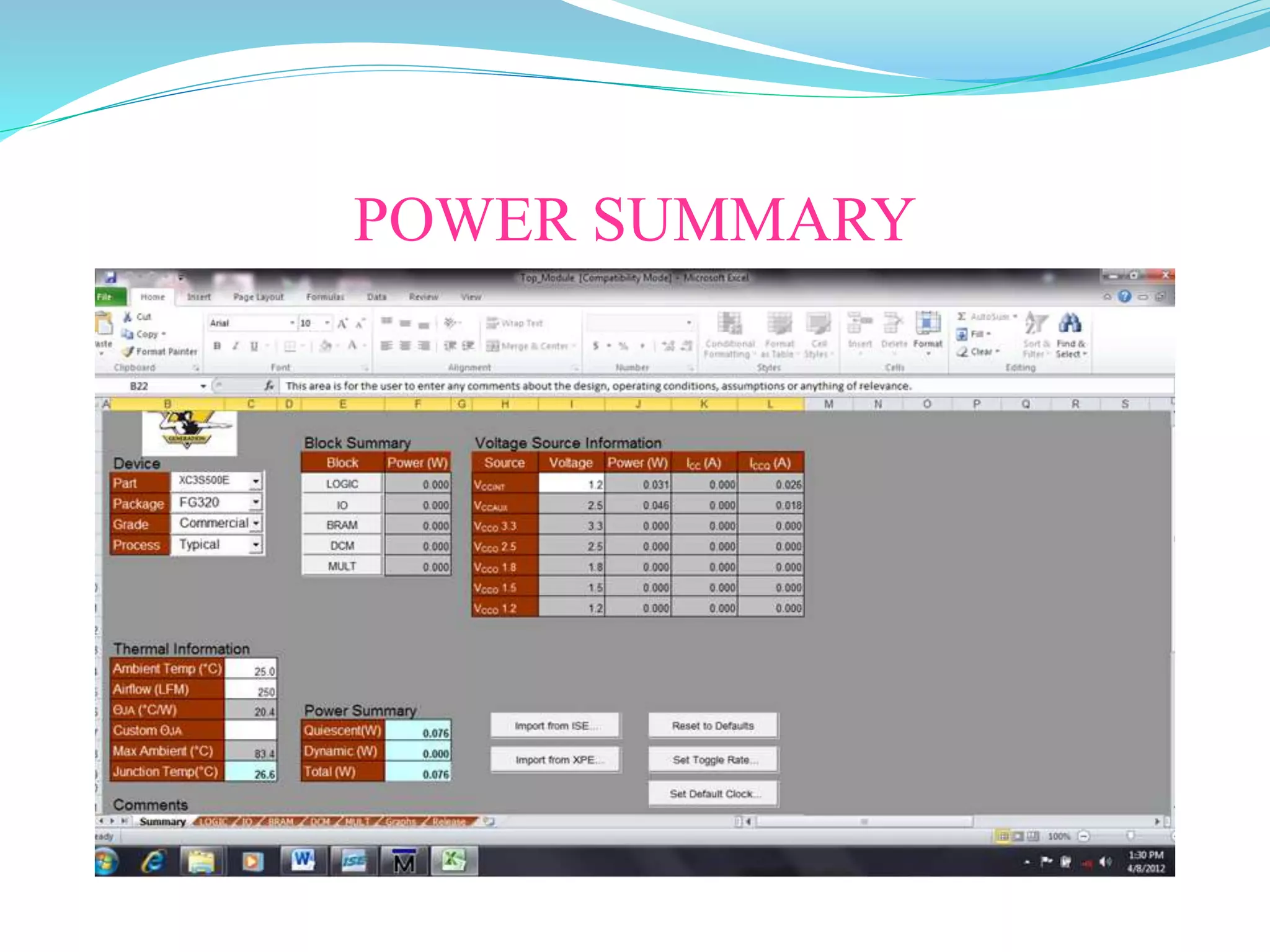

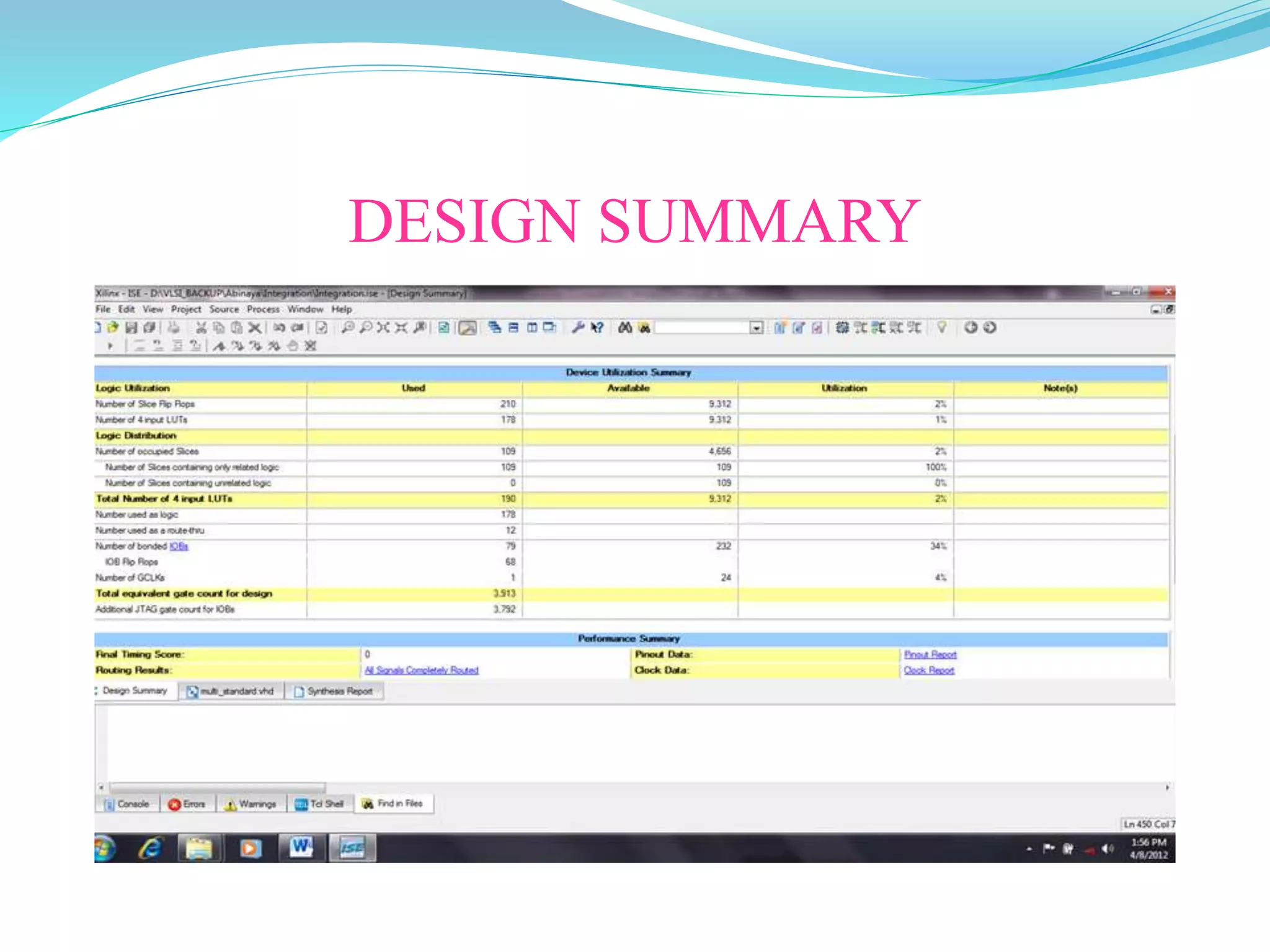

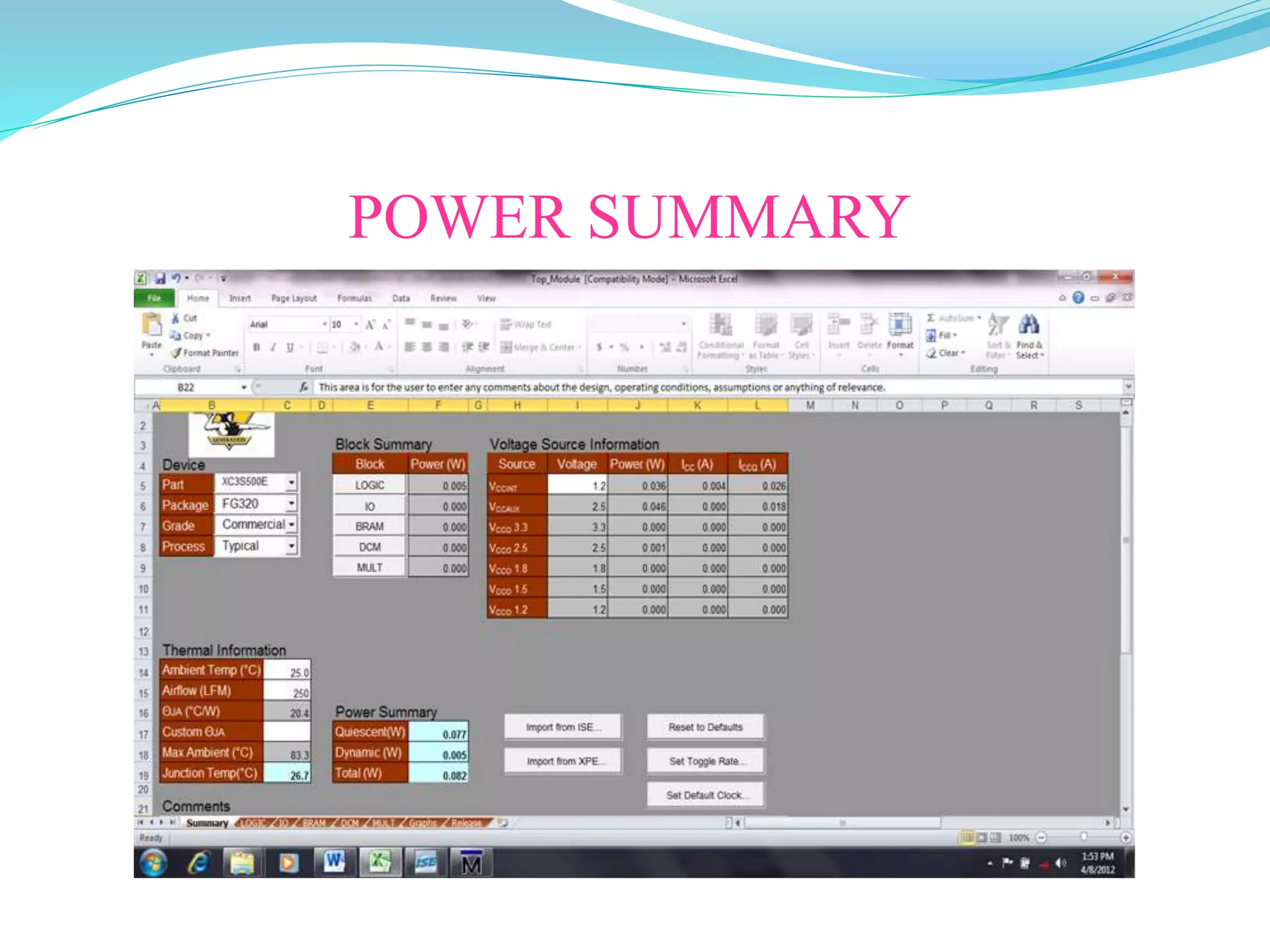

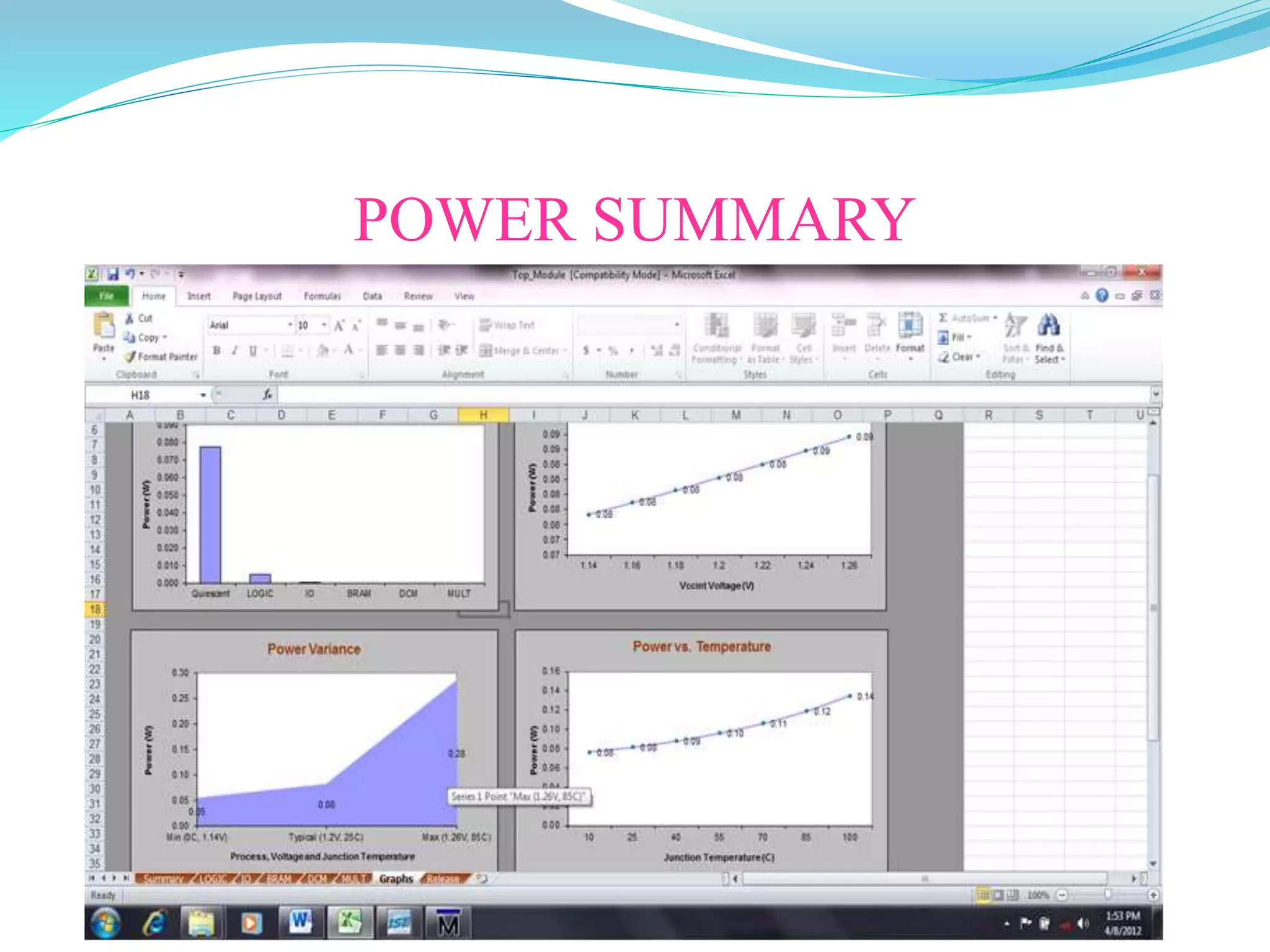

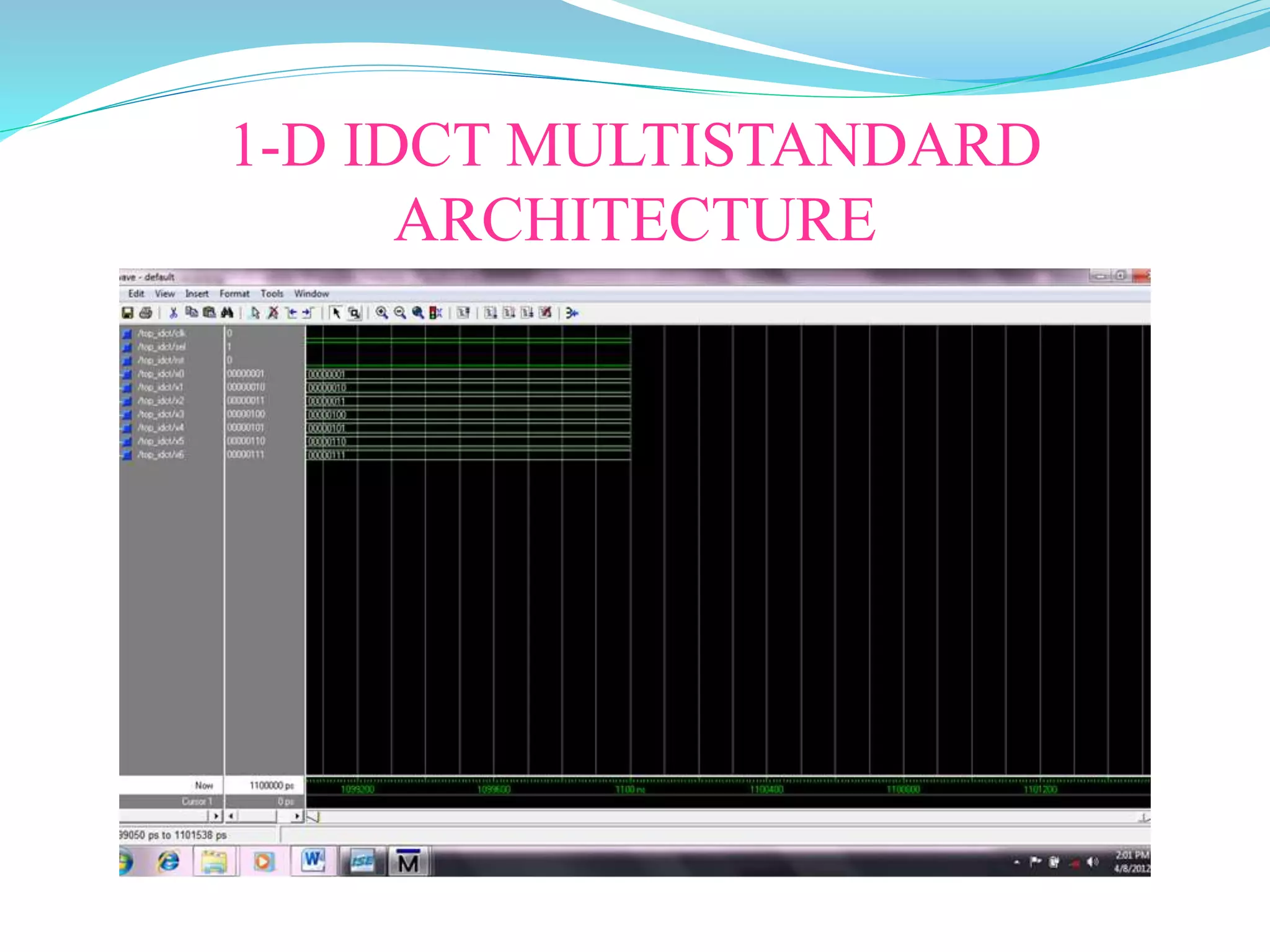

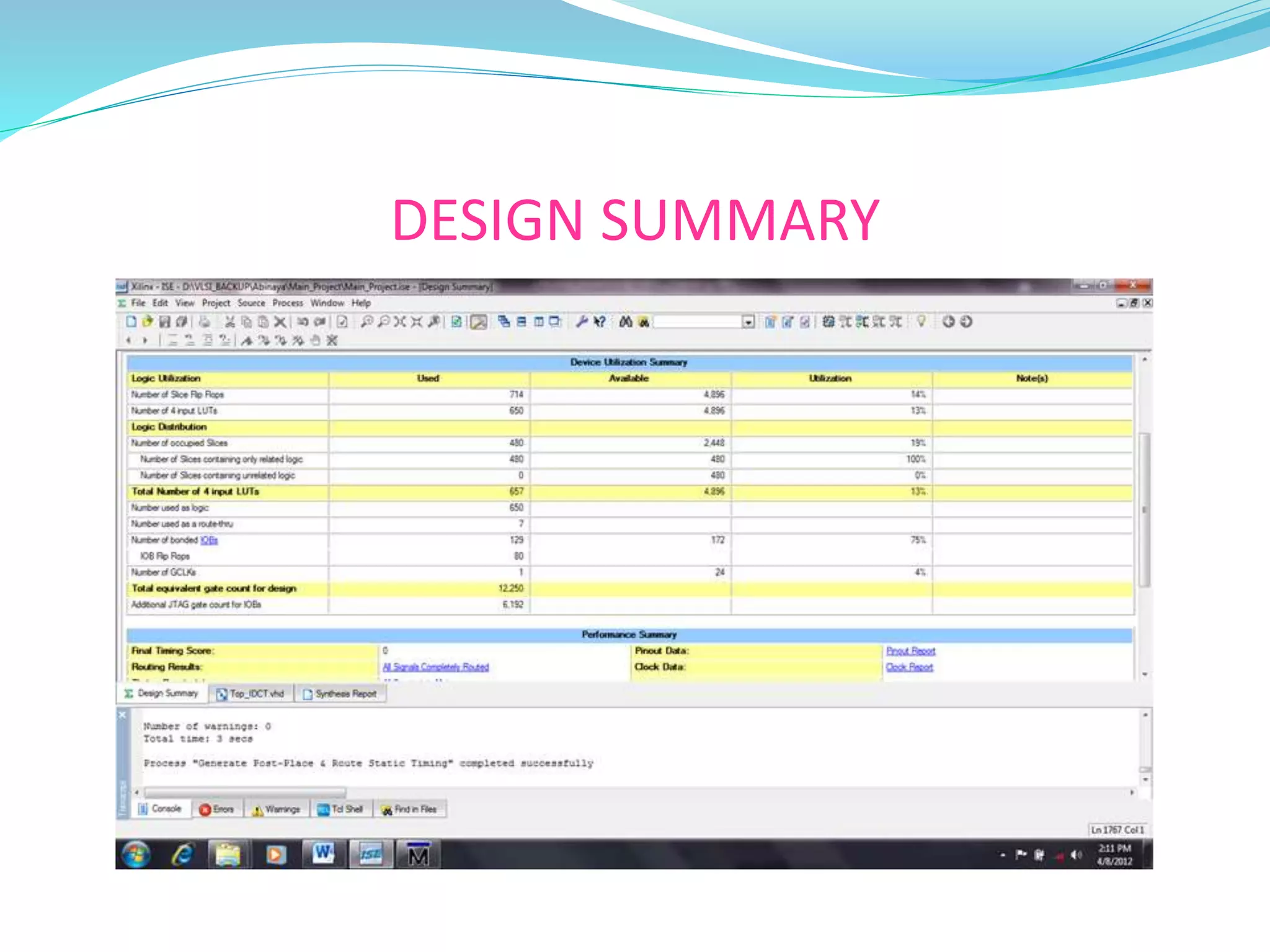

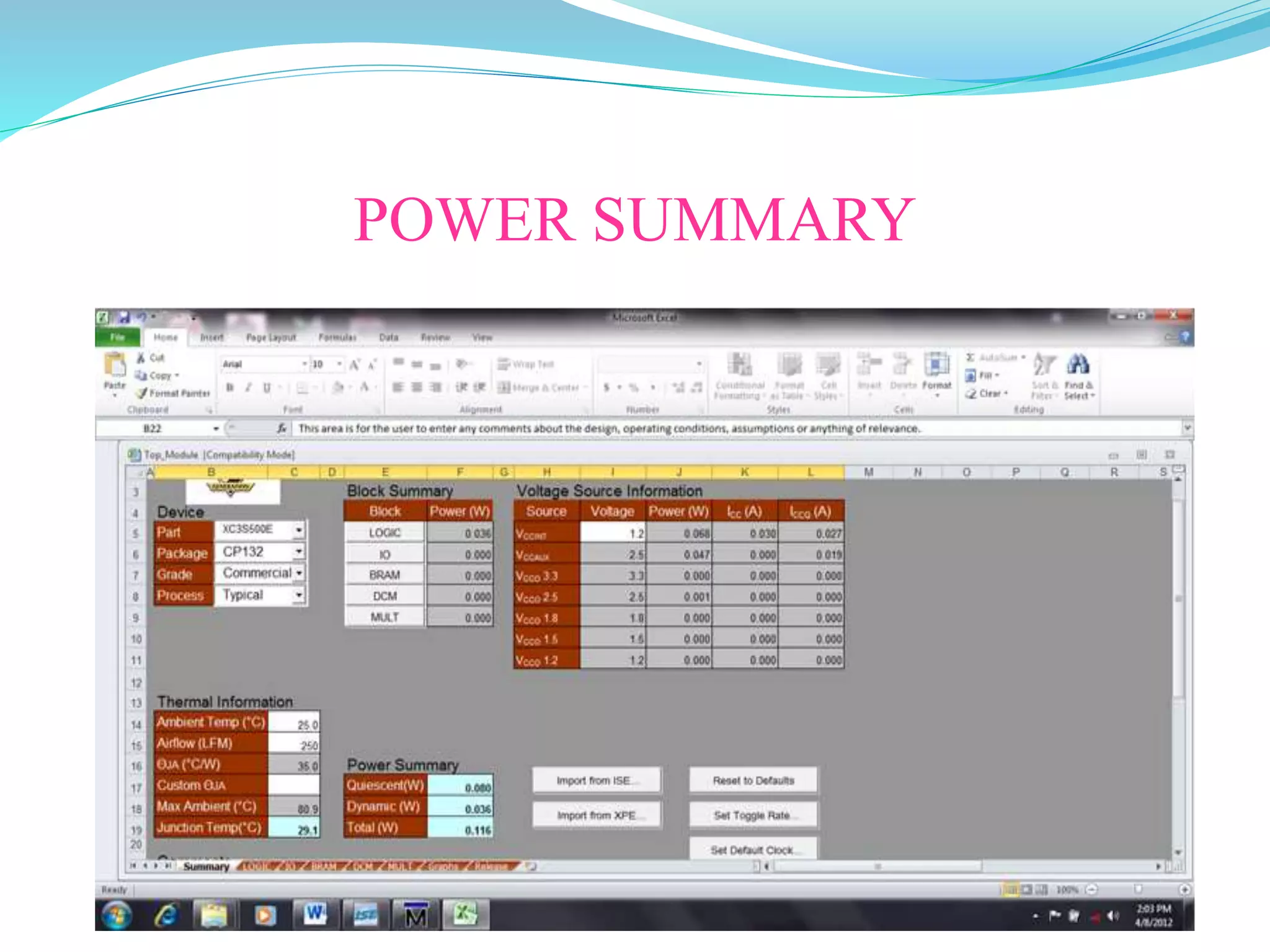

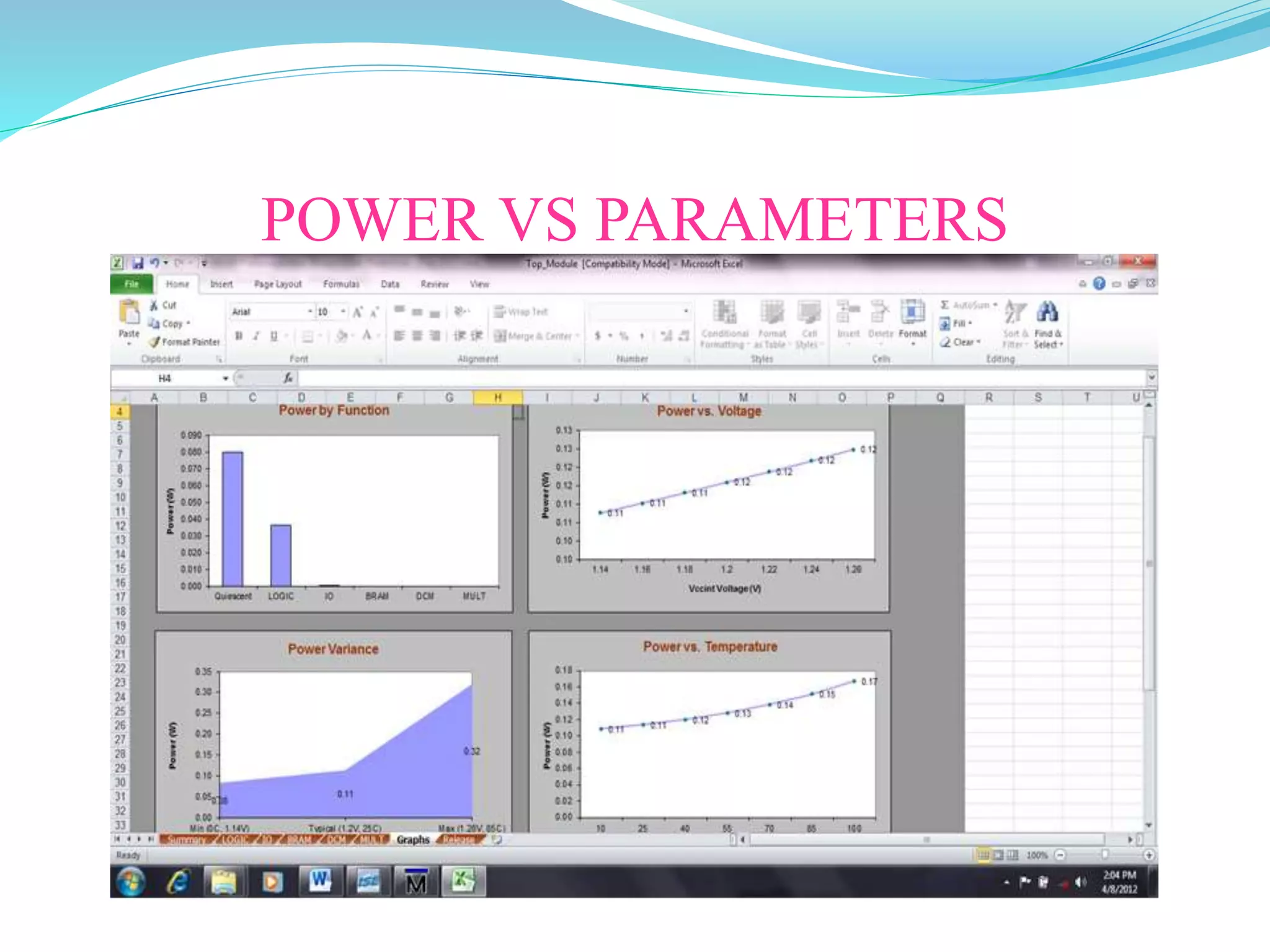

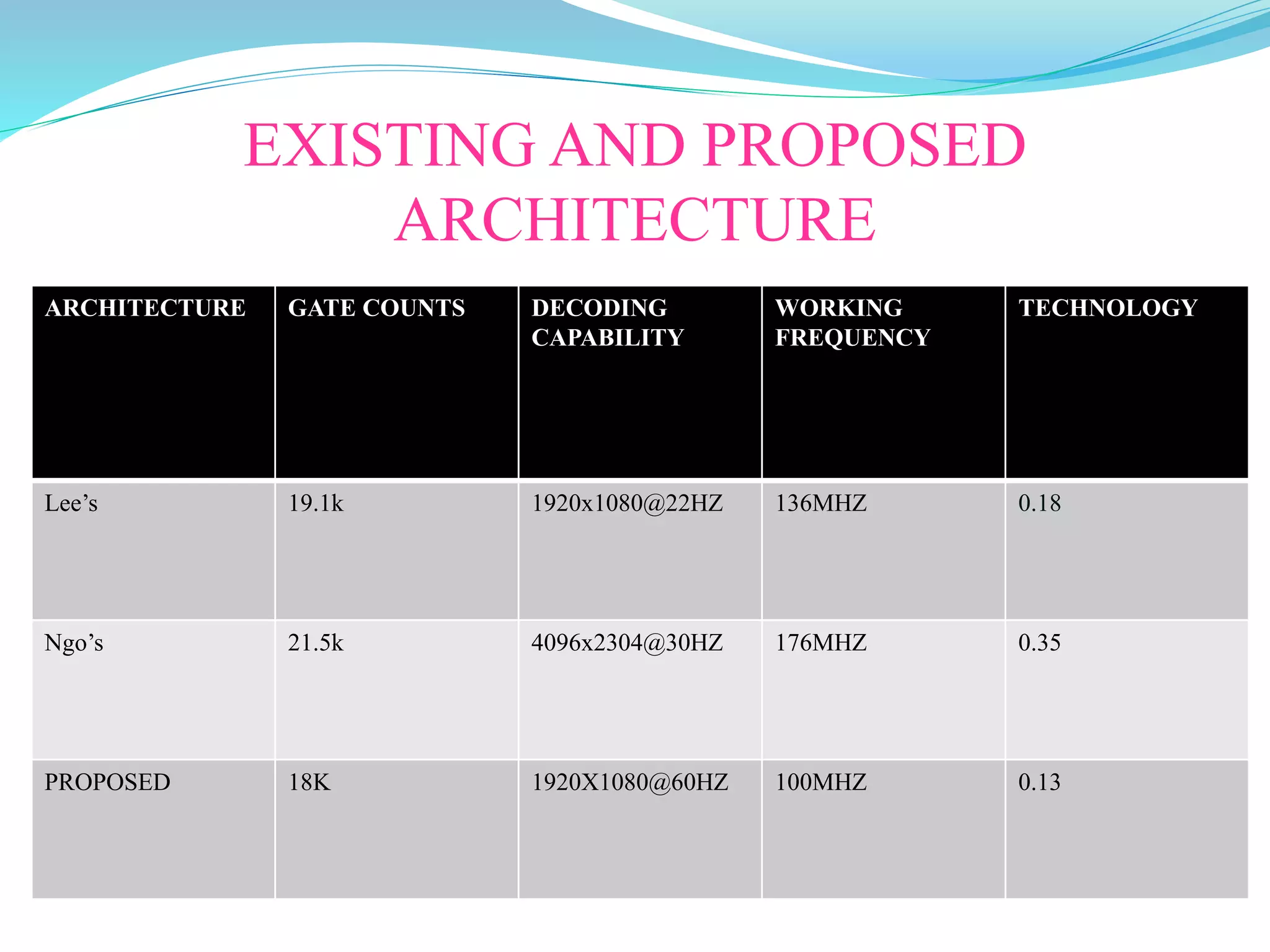

This document describes the design and implementation of a low cost, VLSI architecture for multi-standard inverse discrete cosine transforms (IDCTs). The architecture aims to integrate MPEG-4 and VC-1 decoding standards into a single chip to reduce area and power consumption. It presents circuit designs for the individual MPEG-4 and VC-1 IDCT blocks and an integrated architecture that shares adders and scaling factors between the transforms through factorization. The proposed integrated 1D multi-standard IDCT architecture achieves 1920x1080 video decoding at 60Hz while consuming less than 18k gates, operating at 100MHz in 0.13um technology.