This document contains confidential engineering drawings and schematics for Compal Electronics, Inc. It states that the document is the proprietary property of Compal Electronics and contains trade secret information. It also states that the document and information within it may not be shared with or disclosed to any third party without Compal's prior written consent.

![w

w

w

.

R

a

h

a

s

i

a

L

a

p

t

o

p

.

c

o

m

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

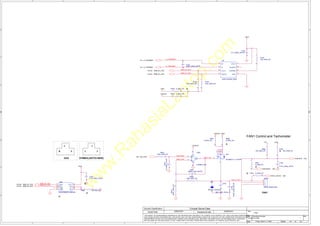

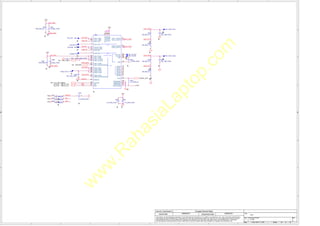

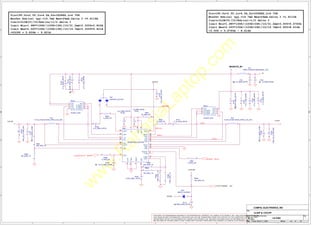

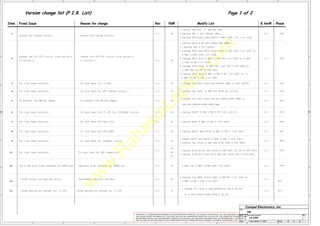

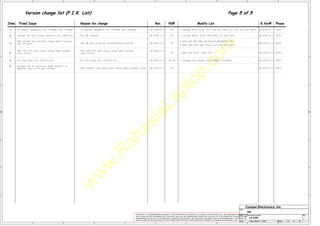

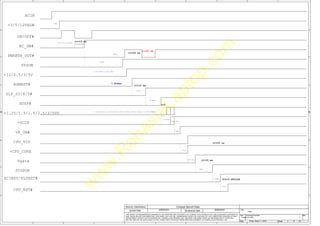

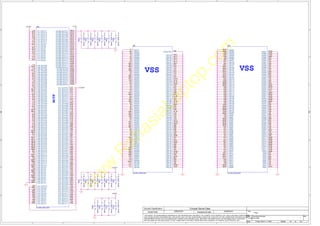

ITP_TDI

ITP_TMS

ITP_TDO

ITP_TRST#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#5

ITP_DBRESET# ITP_TDO

H_RESET#

ITP_TMS

ITP_TDI

ITP_TRST#

ITP_TCK

ITP_DBRESET#

ITP_TCK

ITP_BPM#3

H_PWRGOOD

CLK_ITP_R

CLK_ITP_R#

CLK_ITP#

CLK_ITP

CLK_ITP_R

TEST1

H_RESET#

H_INTR

H_D#27

H_D#19

H_D#16

H_D#8

CLK_CPU_BCLK

H_REQ#4

H_REQ#2

H_A#25

H_D#30

H_D#26

H_D#14

H_D#12

H_A#20

H_FERR#

H_D#56

H_D#5

H_THERMDC

H_RS#2

H_RS#0

H_ADS#

H_A#29

H_A#26

H_A#7

H_A20M#

H_D#41

H_D#29

H_D#24

H_D#21

H_ADSTB#0

H_A#14

H_HIT#

H_BPRI#

H_A#22

H_A#21

H_A#5

H_A#3

H_D#46

H_D#42

H_D#39

ITP_BPM#0

H_BR0#

H_A#28

H_A#23

H_A#15

H_A#13

H_D#58

H_D#37

H_D#0

CLK_CPU_BCLK#

H_A#24

H_A#11

H_A#8

H_INIT#

H_DSTBP#1

H_D#60

H_DRDY#

H_REQ#0

H_A#30

H_A#10

H_DSTBP#3

H_D#57

H_D#48

H_D#47

H_D#28

H_D#22

H_RS#1

H_ADSTB#1

H_A#31

H_A#27

H_A#9

H_NMI

H_D#20

H_D#18

H_D#13

H_DEFER#

H_A#18

H_DSTBN#0

H_D#52

H_D#51

H_D#50

H_D#45

H_D#15

H_D#11

H_D#3

ITP_BPM#3

H_IGNNE#

H_DSTBP#2

H_DSTBN#1

H_D#33

H_D#23

H_D#7

H_D#1

H_REQ#3

H_DSTBP#0

H_D#63

H_D#59

H_D#49

H_D#32

H_D#17

ITP_BPM#2

H_TRDY#

H_HITM#

H_REQ#1

H_D#54

H_D#44

H_D#43

H_D#9

H_D#4

ITP_BPM#1

H_A#19

H_D#53

H_D#40

H_D#36

H_D#2

H_IERR#

CPU_CK_ITP#

CPU_CK_ITP

H_A#12

H_A#6

H_DSTBN#2

H_D#62

H_D#61

H_D#35

H_D#34

H_D#31

H_D#25

H_D#10

H_D#6

H_THERMDA

H_RESET#

H_DSTBN#3

H_D#55

H_D#38

H_LOCK#

H_BNR#

H_A#17

H_A#16

H_A#4

H_DPRSLP#

TEST1

TEST2

ITP_TCK

ITP_TRST#

ITP_TDO

H_CPUSLP#

ITP_TMS

ITP_TDI

ITP_BPM#5

ITP_BPM#4

H_PROCHOT#

H_SMI#

H_STPCLK#

ITP_DBRESET#

H_DPSLP#

H_DBSY#

TEST2

H_PROCHOT#

ITP_BPM#5

ITP_BPM#4

H_A#[3..31]

<8>

H_REQ#[0..4]

<8>

H_ADSTB#0

<8>

H_ADSTB#1

<8>

CLK_ITP

<18>

CLK_ITP#

<18>

CLK_CPU_BCLK

<18>

CLK_CPU_BCLK#

<18>

H_ADS#

<8>

H_BNR#

<8>

H_BR0#

<8>

H_BPRI#

<8>

H_DEFER#

<8>

H_DRDY#

<8>

H_HIT#

<8>

H_HITM#

<8>

H_LOCK#

<8>

H_RESET#

<8>

H_RS#[0..2]

<8>

H_TRDY#

<8>

H_DPSLP#

<20>

H_DPRSLP#

<20>

H_CPUSLP#

<8,20>

H_DBSY#

<8>

H_DPWR#

<8>

H_PWRGOOD

<20>

H_THERMDA

<34>

H_THERMDC

<34>

H_THERMTRIP#

<8,20>

H_A20M# <20>

H_FERR# <20>

H_IGNNE# <20>

H_INIT# <20>

H_INTR <20>

H_NMI <20>

H_STPCLK# <20>

H_SMI# <20>

H_DINV#0 <8>

H_DINV#1 <8>

H_DINV#2 <8>

H_DINV#3 <8>

H_DSTBN#[0..3] <8>

H_DSTBP#[0..3] <8>

H_D#[0..63] <8>

PROCHOT# <32>

+VCCP

+VCCP

+VCCP

+3V

+VCCP

+VCCP

+VCCP

+3VS

Title

Size Document Number Rev

Date: Sheet of

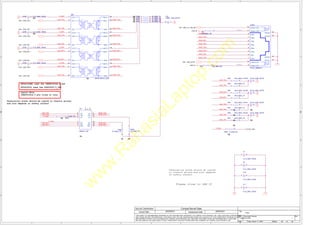

Security Classification Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date Deciphered Date

LA-2362 1

<Title>

Custom

5 52

Friday, March 11, 2005

2005/03/01 2006/03/01

This shall place near CPU

Add pullups for PWRGOOD and THERMTRIP per INTEL

Place near JITP

Check ITP connector.

Place near JITP 0.5"

Test pad as closed as posible

39.4

T7

PAD

T12

PAD

R100

680_0402_5%

1 2

R110 0_0402_5%

@

1 2

T5 PAD

R464

1K_0402_5%

@

1 2

R87

22.6_0402_1%

1 2

T14

PAD

T15

PAD

R90

54.9_0603_1%

1 2

R79

150_0402_5%

1 2

T17

PAD

R109 0_0402_5%

@ 1 2

R530

1K_0402_5%

@

1 2

R132

1K_0402_5%

1

2

R76

54.9_0603_1%

1 2

T9

PAD

C359

0.1U_0402_10V6K

1

2

R458

200_0402_5%

1 2

T16

PAD

R124

56_0402_5%

1

2

C

B

E

Q6

2SC2411K_SC59

1

2

3

T39 PAD

T13

PAD

T8

PAD

R78

56_0402_5%

1 2

T11

PAD

R745 56_0402_5%

1 2

T4

PAD

R479

37.4_0402_1%

1 2

R112 0_0402_5%

@

1 2

T10

PAD

ADDR GROUP

CONTROL GROUP

HOST CLK

MISC

DATA GROUP

THERMAL

DIODE

LEGACY CPU

Dothan

JCPU1A

TYCO_1612365-1_Dothan

A3#

P4

A4#

U4

A5#

V3

A6#

R3

A7#

V2

A8#

W1

A9#

T4

A10#

W2

A11#

Y4

A12#

Y1

A13#

U1

A14#

AA3

A15#

Y3

A16#

AA2

A17#

AF4

A18#

AC4

A19#

AC7

A20#

AC3

A21#

AD3

A22#

AE4

A23#

AD2

A24#

AB4

A25#

AC6

A26#

AD5

A27#

AE2

A28#

AD6

A29#

AF3

A30#

AE1

A31#

AF1

REQ0#

R2

REQ1#

P3

REQ2#

T2

REQ3#

P1

REQ4#

T1

ADSTB0#

U3

ADSTB1#

AE5

BCLK0

B15

BCLK1

B14

ITP_CLK0

A16

ITP_CLK1

A15

ADS#

N2

BNR#

L1

BPRI#

J3

BR0#

N4

DEFER#

L4

DRDY#

H2

HIT#

K3

HITM#

K4

IERR#

A4

LOCK#

J2

RESET#

B11

RS0#

H1

RS1#

K1

RS2#

L2

TRDY#

M3

BPM0#

C8

BPM1#

B8

BPM2#

A9

BPM3#

C9

DBR#

A7

DBSY#

M2

DPSLP#

B7

DPWR#

C19

PRDY#

A10

PREQ#

B10

PROCHOT#

B17

PWRGOOD

E4

SLP#

A6

TCK

A13

TDI

C12

TDO

A12

TEST1

C5

TEST2

F23

TMS

C11

TRST#

B13

THERMDA

B18

THERMDC

A18

THERMTRIP#

C17

D0# A19

D1# A25

D2# A22

D3# B21

D4#

A24

D5#

B26

D6#

A21

D7#

B20

D8#

C20

D9#

B24

D10#

D24

D11#

E24

D12#

C26

D13#

B23

D14#

E23

D15#

C25

D16#

H23

D17#

G25

D18# L23

D19# M26

D20# H24

D21# F25

D22# G24

D23# J23

D24# M23

D25# J25

D26# L26

D27# N24

D28# M25

D29# H26

D30# N25

D31# K25

D32# Y26

D33# AA24

D34# T25

D35# U23

D36# V23

D37# R24

D38# R26

D39# R23

D40# AA23

D41# U26

D42# V24

D43# U25

D44# V26

D45# Y23

D46#

AA26

D47#

Y25

D48#

AB25

D49#

AC23

D50#

AB24

D51#

AC20

D52#

AC22

D53#

AC25

D54#

AD23

D55#

AE22

D56#

AF23

D57#

AD24

D58#

AF20

D59#

AE21

D60#

AD21

D61#

AF25

D62#

AF22

D63#

AF26

DINV0#

D25

DINV1#

J26

DINV2#

T24

DINV3#

AD20

DSTBN0#

C23

DSTBN1#

K24

DSTBN2#

W25

DSTBN3#

AE24

DSTBP0#

C22

DSTBP1#

L24

DSTBP2#

W24

DSTBP3#

AE25

A20M#

C2

FERR#

D3

IGNNE#

A3

INIT#

B5

LINT0

D1

LINT1

D4

STPCLK#

C6

SMI#

B4

DPRSTP#

G1

R106

27.4_0402_1%

1 2

T19

PAD

R111 0_0402_5%

@ 1 2

R123

56_0402_5%

1

2

R85

150_0402_5%

1 2

T6

PAD

R74

22.6_0402_1%

1 2](https://image.slidesharecdn.com/acer80a-231231163455-e3ad905d/85/ACER-80A-pdf-5-320.jpg)

![w

w

w

.

R

a

h

a

s

i

a

L

a

p

t

o

p

.

c

o

m

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

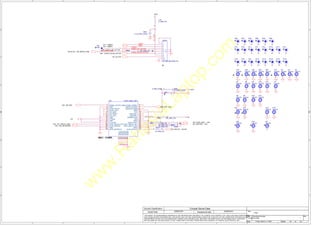

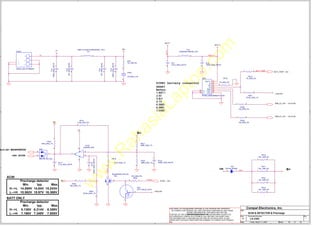

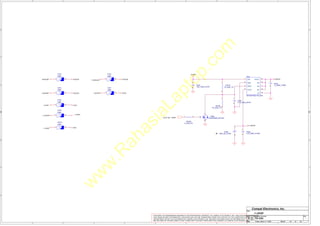

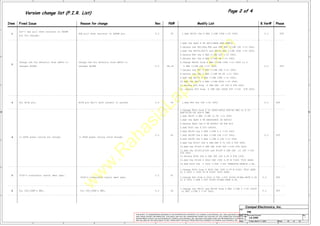

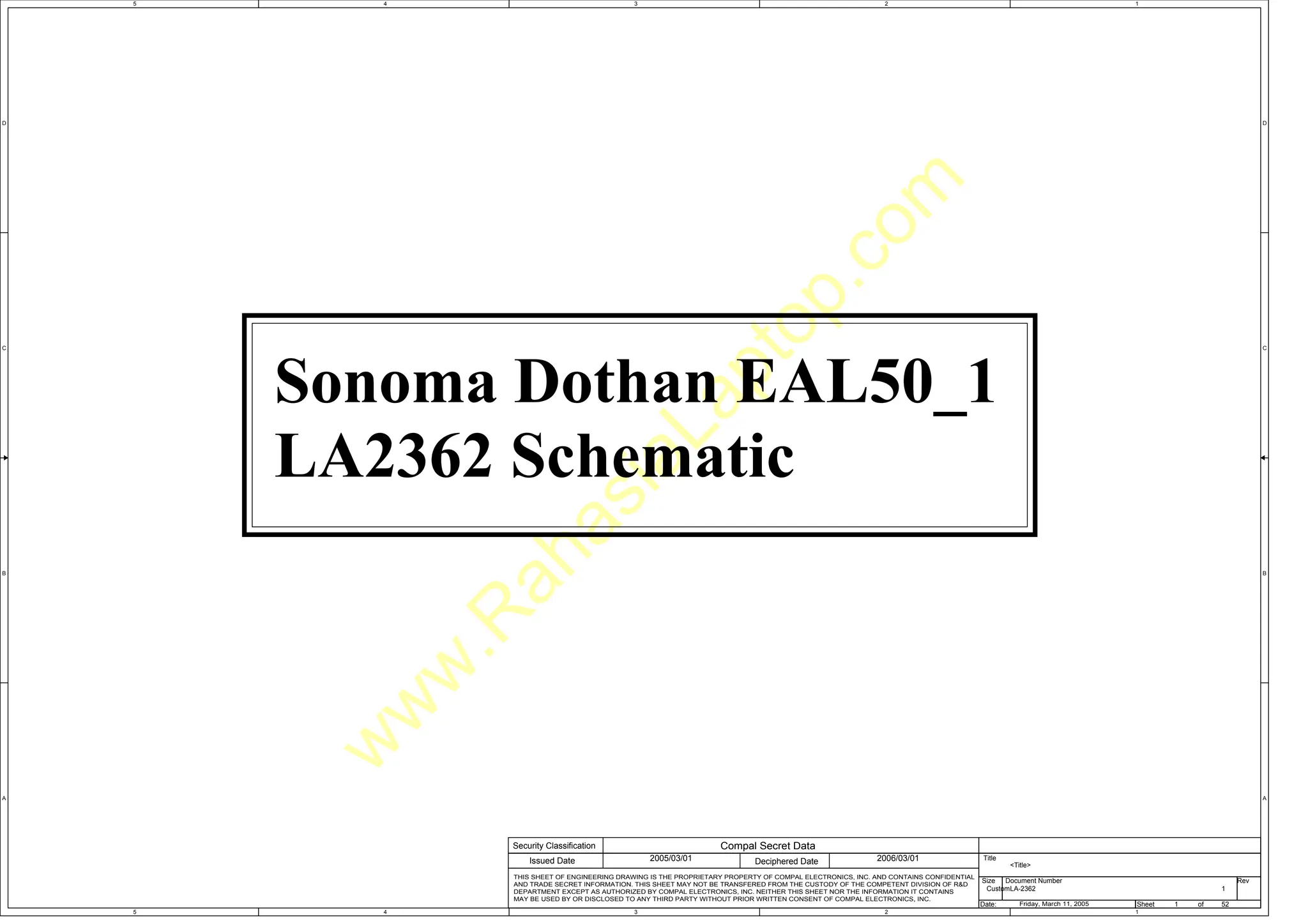

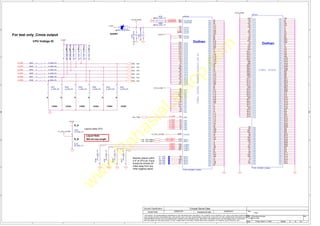

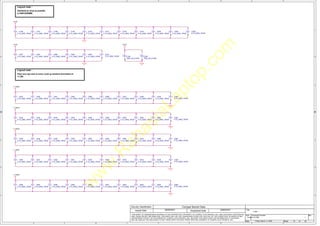

H_SWNG1

PM_EXTTS#0

PM_EXTTS#1

PLTRST_R#

H_ADSTB#1

H_R_CPUSLP#

H_RS#2

H_RS#0

H_RS#1

H_YSCOMP

H_YRCOMP

H_SWNG0

H_SWNG1

H_SWNG0

PM_EXTTS#0

PM_EXTTS#1

MCH_CLKSEL0

CFG6

CFG5

CFG7

CFG12

CFG13

CFG19

CFG16

CFG18

MCH_CLKSEL1

DDR_SCS#3

DDR_SCS#2

DDR_SCS#0

DDR_SCS#1

DDR_CKE3

DDR_CKE1

DDR_CKE2

DDR_CKE0

DDR_CLK0#

DDR_CLK1#

DDR_CLK3#

DDR_CLK4#

DDR_CLK0

DDR_CLK1

DDR_CLK3

DDR_CLK4

DMI_RXP1

DMI_RXP0

DMI_RXN0

DMI_RXN1

DMI_TXP0

DMI_TXP1

DMI_TXN0

DMI_TXN1

SMRCOMPP

SMRCOMPN

H_CPUSLP# H_R_CPUSLP#

CFG0

CFG9

DMI_RXP3

DMI_RXP2

DMI_RXN2

DMI_RXN3

DMI_TXP2

DMI_TXP3

DMI_TXN2

DMI_TXN3

M_OCDOCMP0

M_OCDOCMP1

M_OCDOCMP0

M_OCDOCMP1

H_THERMTRIP#

H_DRDY#

H_A#25

H_A#24

H_A#23

H_REQ#3

H_DSTBP#0

H_REQ#2

H_A#12

H_A#5

H_A#4

H_BNR#

H_A#18

H_DSTBN#0

H_A#21

H_A#20

H_A#14

H_A#9

TP_H_EDRDY#

H_ADS#

H_A#29

H_REQ#0

H_A#31

H_A#30

H_BPRI#

H_RESET#

H_DBSY#

H_DSTBN#3

TP_H_PCREQ#

H_A#28

H_DSTBN#1

H_VREF

H_A#16

H_A#15

H_BR0#

H_A#17

H_A#13

H_LOCK#

H_A#8

H_ADSTB#0

H_DSTBP#1

H_REQ#4

H_A#26

H_A#19

H_A#6

H_TRDY#

H_A#11

H_A#7

H_DSTBN#2

H_REQ#1

H_A#22

H_A#10

H_DSTBP#3

H_DEFER#

H_DSTBP#2

H_A#27

H_A#3

H_XRCOMP

H_D#21

H_D#61

H_D#35

H_D#6

H_D#47

H_D#58

H_D#51

H_D#31

H_D#26

H_D#13

H_D#55

H_D#48

H_D#15

H_D#0

H_D#59

H_D#23

H_D#3

H_D#1

H_D#32

H_D#11

H_D#5

H_D#62

H_D#29

H_D#49

H_D#44

H_D#25

H_D#16

H_D#50

H_D#43

H_D#27

H_D#56

H_D#45

H_D#18

H_D#40

H_D#38

H_D#36

H_D#34

H_D#24

H_D#42

H_D#39

H_D#22

H_D#37

H_D#9

H_D#8

H_D#46

H_D#33

H_D#60

H_D#52

H_D#28

H_D#19

H_D#7

H_D#2

H_D#54

H_D#14

H_D#4

H_D#41

H_D#20

H_D#10

H_D#30

H_D#63

H_D#57

H_D#53

H_D#17

H_D#12

H_XSCOMP

CFG5

CFG7

CFG6

CFG0

CFG12

CFG13

CFG18

CFG19

CFG9

CFG16

H_HIT#

H_HITM#

H_A#[3..31]

<5>

H_REQ#[0..4]

<5>

H_ADSTB#0

<5>

H_ADSTB#1

<5>

CLK_MCH_BCLK#

<18>

CLK_MCH_BCLK

<18>

H_DSTBN#[0..3]

<5>

H_DSTBP#[0..3]

<5>

H_DINV#0

<5>

H_DINV#1

<5>

H_DINV#2

<5>

H_DINV#3

<5>

H_RESET#

<5>

H_ADS#

<5>

H_TRDY#

<5>

H_DPWR#

<5>

H_DRDY#

<5>

H_DEFER#

<5>

H_BR0#

<5>

H_BNR#

<5>

H_BPRI#

<5>

H_DBSY#

<5>

H_HITM#

<5>

H_HIT#

<5>

H_LOCK#

<5>

H_RS#[0..2]

<5>

H_CPUSLP#

<5,20>

H_D#[0..63] <5>

DMI_TXN0

<21>

DMI_TXN1

<21>

DMI_TXN2

<21>

DMI_TXN3

<21>

DMI_TXP0

<21>

DMI_TXP1

<21>

DMI_TXP2

<21>

DMI_TXP3

<21>

DMI_RXN0

<21>

DMI_RXN1

<21>

DMI_RXN2

<21>

DMI_RXN3

<21>

DMI_RXP0

<21>

DMI_RXP1

<21>

DMI_RXP2

<21>

DMI_RXP3

<21>

DDR_CLK0

<13>

DDR_CLK1

<13>

DDR_CLK3

<14>

DDR_CLK4

<14>

DDR_CLK0#

<13>

DDR_CLK1#

<13>

DDR_CLK3#

<14>

DDR_CLK4#

<14>

DDR_CKE0

<13>

DDR_CKE1

<13>

DDR_CKE2

<14>

DDR_CKE3

<14>

DDR_SCS#0

<13>

DDR_SCS#1

<13>

DDR_SCS#2

<14>

DDR_SCS#3

<14>

MCH_CLKSEL1 <18>

MCH_CLKSEL0 <18>

PM_BMBUSY# <21>

H_THERMTRIP# <5,20>

VGATE <18,21,45>

DREFCLK# <18>

DREFCLK <18>

SSC_DREFCLK <18>

SSC_DREFCLK# <18>

PLTRST_MCH# <19>

+VCCP

+VCCP

+VCCP

+VCCP

+2.5VS

+2.5V

+VCCP

+SDREF_DIMM

+VCCP

+2.5VS

Title

Size Document Number Rev

Date: Sheet of

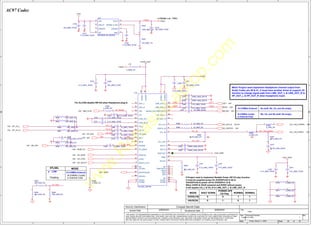

Security Classification Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date Deciphered Date

LA-2362 1

<Title>

Custom

8 52

Friday, March 11, 2005

2005/03/01 2006/03/01

Layout Guide

will show these

signals routed

differentially.

Layout Guide will show

these signals routed

differentially.

Note:

"Do not install R for Dothan-A,

Install R97 for Dothan-B"

Layout Note:

Rote as short

as possible

CFG[17:3] have internal pull-up

CFG[19:18] have internal pull-down

CFG[2:0]

Refer to sheet 6 for FSB

frequency select

CFG19

(VTT Select)

*

*

CFG18

(VCC Select)

Low = DMI x 2

CFG7

High = DMI x 4

CFG5

Low = DT/Transportable CPU

High = Mobile CPU

CFG6

High = DDR-I

Low = DDR-II

CFG[13:12]

CFG16

(FSB Dynamic

ODT)

Low = 1.05V (Default)

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation (Default)

High = 1.2V

Low = 1.05V (Default)

High = 1.5V

High = Enabled

Low = Disabled

Low = Reverse Lane

CFG9

High = Normal Operation

*

*

*

*

*

*

10/20 mils

3.5 k reserve for choose

3.5 k reserve for choose

Alviso CFG[17:3] has internal pull-up

R387 10K_0402_5%

@

1

2

R35

2.2K_0402_5% @ 1

2

R367 10K_0402_5%

1

2

HOST

Alviso

U5A

ALVISO_BGA1257

HD0#

E4

HD1#

E1

HD2#

F4

HD3#

H7

HD4#

E2

HD5#

F1

HD6#

E3

HD7#

D3

HD8#

K7

HD9#

F2

HD10#

J7

HD11# J8

HD12# H6

HD13# F3

HD14# K8

HD15# H5

HD16# H1

HD17# H2

HD18# K5

HD19# K6

HD20# J4

HD21# G3

HD22# H3

HD23# J1

HD24# L5

HD25# K4

HD26# J5

HD27# P7

HD28# L7

HD29# J3

HD30# P5

HD31# L3

HD32# U7

HD33# V6

HD34# R6

HD35# R5

HD36# P3

HD37# T8

HD38# R7

HD39#

R8

HD40#

U8

HD41#

R4

HD42#

T4

HD43#

T5

HD44#

R1

HD45#

T3

HD46#

V8

HD47#

U6

HD48#

W6

HD49#

U3

HD50#

V5

HD51#

W8

HD52#

W7

HD53#

U2

HD54#

U1

HD55#

Y5

HD56#

Y2

HD57#

V4

HD58#

Y7

HD59#

W1

HD60#

W3

HD61#

Y3

HD62#

Y6

HD63#

W2

HA3#

G9

HA4#

C9

HA5#

E9

HA6#

B7

HA7#

A10

HA8#

F9

HA9#

D8

HA10#

B10

HA11#

E10

HA12#

G10

HA13#

D9

HA14#

E11

HA15#

F10

HA16#

G11

HA17#

G13

HA18#

C10

HA19#

C11

HA20#

D11

HA21#

C12

HA22#

B13

HA23#

A12

HA24#

F12

HA25#

G12

HA26#

E12

HA27#

C13

HA28#

B11

HA29#

D13

HA30#

A13

HA31#

F13

HREQ#0

A7

HREQ#1

D7

HREQ#2

B8

HREQ#3

C7

HREQ#4

A8

HADSTB#0

B9

HADSTB#1

E13

HPCREQ#

A11

HCLKN

AB1

HCLKP

AB2

HVREF

J11

HXRCOMP

C1

HXSCOMP

C2

HYRCOMP

T1

HYSCOMP

L1

HYSWING

P1

HXSWING

D1

HDSTBN#0

G4

HDSTBN#1

K1

HDSTBN#2

R3

HDSTBN#3

V3

HDSTBP#0

G5

HDSTBP#1

K2

HDSTBP#2

R2

HDSTBP#3

W4

HDINV#0

H8

HDINV#1

K3

HDINV#2

T7

HDINV#3

U5

HCPURST#

H10

HADS#

F8

HTRDY#

B5

HDPWR#

G6

HDRDY#

F7

HDEFER#

E6

HEDRDY#

F6

HHITM#

D6

HHIT#

D4

HLOCK#

B3

HBREQ0#

E7

HBNR#

A5

HBPRI#

D5

HDBSY#

C6

HCPUSLP#

G8

HRS0#

A4

HRS1#

C5

HRS2#

B4

R38

2.2K_0402_5% @ 1

2

T1 PAD

R57

56_0402_5%

@

1 2

DMI

DDR

MUXING

CFG/RSVD

PM

CLK

NC

U5B

ALVISO_BGA1257

DMIRXN0

AA31

DMIRXN1

AB35

DMIRXP0

Y31

DMIRXP1

AA35

DMITXN0

AA33

DMITXN1

AB37

DMITXP0

Y33

DMITXP1

AA37

SM_CK0

AM33

SM_CK1

AL1

SM_CK2

AE11

SM_CK3

AJ34

SM_CK4

AF6

SM_CK5

AC10

SM_CK0#

AN33

SM_CK1#

AK1

SM_CK2#

AE10

SM_CK3#

AJ33

SM_CK4#

AF5

SM_CK5#

AD10

SM_CKE0

AP21

SM_CKE1

AM21

SM_CKE2

AH21

SM_CKE3

AK21

SM_CS0#

AN16

SM_CS1#

AM14

SM_CS2#

AH15

SM_CS3#

AG16

SM_OCDCOMP0

AF22

SM_OCDCOMP1

AF16

SM_ODT0

AP14

SM_ODT1

AL15

SM_ODT2

AM11

SM_ODT3

AN10

SMRCOMPN

AK10

SMRCOMPP

AK11

SMVREF0

AF37

SMVREF1

AD1

SMXSLEWIN

AE27

SMXSLEWOUT

AE28

SMYSLEWIN

AF9

SMYSLEWOUT

AF10

CFG0 G16

CFG1

H13

CFG2

G14

CFG3

F16

CFG4

F15

CFG5

G15

CFG6

E16

CFG7

D17

CFG8

J16

CFG9

D15

CFG10

E15

CFG11

D14

CFG12

E14

CFG13

H12

CFG14

C14

CFG15 H15

CFG16 J15

CFG17 H14

CFG18 G22

CFG19 G23

CFG20 D23

RSVD21 G25

RSVD22 G24

RSVD23 J17

RSVD24 A31

RSVD25 A30

RSVD26 D26

RSVD27 D25

BM_BUSY# J23

EXT_TS0# J21

EXT_TS1# H22

THRMTRIP# F5

PWROK

AD30

RSTIN#

AE29

DREF_CLKN

A24

DREF_CLKP

A23

DREF_SSCLKN

C37

DREF_SSCLKP

D37

NC1

AP37

NC2

AN37

NC3

AP36

NC4

AP2

NC5

AP1

NC6

AN1

NC7

B1

NC8

A2

NC9

B37

NC10

A36

NC11

A37

DMITXN2

AC33

DMITXN3

AD37

DMIRXN3

AD35

DMIRXN2

AC31

DMITXP2

AB33

DMITXP3

AC37

DMIRXP2

AB31

DMIRXP3

AC35

R397

221_0603_1%

1

2

R376

200_0402_1%

1

2

R484 80.6_0402_1%

1 2

R37 1K_0402_5%

@

1 2

R36 1K_0402_5%

@

1 2

R41

54.9_0402_1%

1

2

T26

PAD @

T27 PAD

@

R370 2.2K_0402_5%

1 2

R374 2.2K_0402_5%

@

1 2

C419

0.1U_0402_16V4Z

1

2

R365

10K_0402_5%

1

2

R477

40.2_0402_1%

@

1

2

R388

100_0402_1%

1

2

T25

PAD @

R489

80.6_0402_1%

1

2

R66

54.9_0402_1%

1

2

R394 2.2K_0402_5%

@

1 2

R384 10K_0402_5%

@

1

2

C385

0.1U_0402_16V4Z

1

2

R77

24.9_0402_1%

1

2

R476

40.2_0402_1%

@

1

2

R44

24.9_0402_1%

1

2

R369 2.2K_0402_5%

1 2

R375 2.2K_0402_5%

@

1 2

R368 2.2K_0402_5%

1 2

R73

100_0603_1%

1

2

R430 2.2K_0402_5%

@

1 2

R418

0_0402_5%

1 2

R492 100_0402_1%

1 2

R372

100_0402_1%

1

2

R366

10K_0402_5%

1

2

R67

221_0603_1%

1

2

C428

0.1U_0402_16V4Z

1

2

C379

0.1U_0402_16V7K 1

2

C362

0.1U_0402_16V4Z

1

2](https://image.slidesharecdn.com/acer80a-231231163455-e3ad905d/85/ACER-80A-pdf-8-320.jpg)

![w

w

w

.

R

a

h

a

s

i

a

L

a

p

t

o

p

.

c

o

m

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

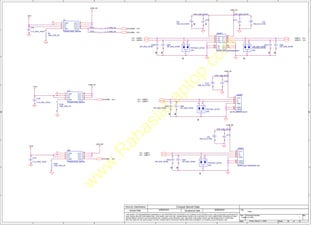

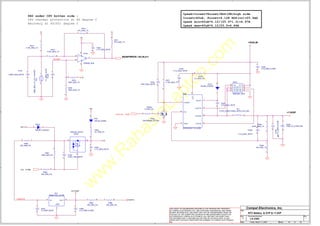

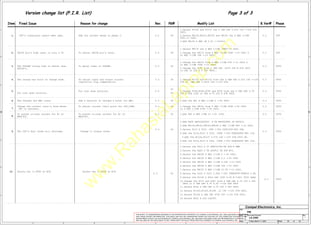

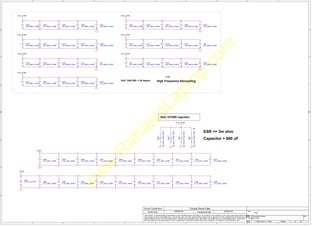

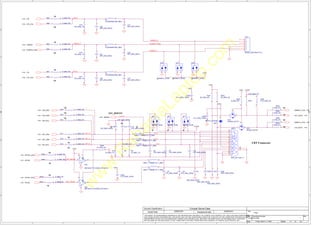

DDR_A_BS#2

DDR_A_DM0

DDR_A_DM6

DDR_A_DM4

DDR_A_DM3

DDR_A_DM1

DDR_A_DM7

DDR_A_DM5

DDR_A_DM2

DDR_A_BS#0

DDR_A_BS#1

TP_MA_RCVENIN#

TP_MA_RCVENOUT#

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_CAS#

DDR_A_WE#

DDR_A_RAS#

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA5

DDR_A_MA4

DDR_A_MA7

DDR_A_MA6

DDR_A_MA10

DDR_A_MA9

DDR_A_MA8

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_D5

DDR_A_D0

DDR_A_D10

DDR_A_D3

DDR_A_D1

DDR_A_D4

DDR_A_D11

DDR_A_D2

DDR_A_D8

DDR_A_D9

DDR_A_D6

DDR_A_D7

DDR_A_D17

DDR_A_D22

DDR_A_D15

DDR_A_D16

DDR_A_D13

DDR_A_D20

DDR_A_D12

DDR_A_D23

DDR_A_D19

DDR_A_D18

DDR_A_D14

DDR_A_D21

DDR_A_D25

DDR_A_D29

DDR_A_D24

DDR_A_D35

DDR_A_D30

DDR_A_D32

DDR_A_D34

DDR_A_D27

DDR_A_D33

DDR_A_D28

DDR_A_D26

DDR_A_D37

DDR_A_D40

DDR_A_D46

DDR_A_D44

DDR_A_D39

DDR_A_D36

DDR_A_D47

DDR_A_D31

DDR_A_D42

DDR_A_D43

DDR_A_D38

DDR_A_D41

DDR_A_D45

DDR_A_D53

DDR_A_D48

DDR_A_D59

DDR_A_D56

DDR_A_D58

DDR_A_D51

DDR_A_D52

DDR_A_D57

DDR_A_D50

DDR_A_D49

DDR_A_D63

DDR_A_D55

DDR_A_D54

DDR_A_D61

DDR_A_D60

DDR_A_D62

DDR_B_BS#0

DDR_B_BS#1

DDR_B_RAS#

DDR_B_WE#

DDR_B_CAS#

TP_MB_RCVENIN#

TP_MB_RCVENOUT#

DDR_B_MA0

DDR_B_MA1

DDR_B_MA7

DDR_B_MA2

DDR_B_MA3

DDR_B_MA5

DDR_B_MA8

DDR_B_MA9

DDR_B_MA12

DDR_B_MA4

DDR_B_MA6

DDR_B_MA13

DDR_B_MA11

DDR_B_MA10

DDR_B_BS#2

DDR_A_BS#0

<13>

DDR_A_BS#1

<13>

DDR_A_DM[0..7]

<13>

DDR_A_MA[0..13]

<13>

DDR_A_CAS#

<13>

DDR_A_RAS#

<13>

DDR_B_WE#

<14>

DDR_B_CAS#

<14>

DDR_B_RAS#

<14>

DDR_B_MA[0..13]

<14>

DDR_B_BS#0

<14>

DDR_B_BS#1

<14>

DDR_A_D[0..63] <13>

DDR_A_DQS[0..7]

<13>

DDR_A_WE#

<13>

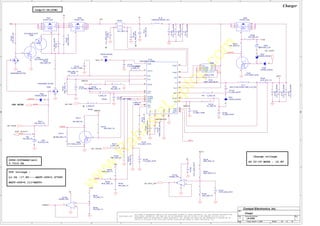

Title

Size Document Number Rev

Date: Sheet of

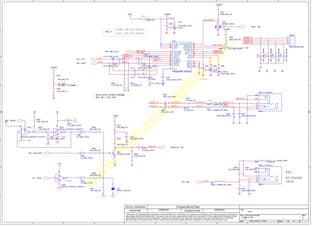

Security Classification Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date Deciphered Date

LA-2362 1

<Title>

Custom

9 52

Friday, March 11, 2005

2005/03/01 2006/03/01

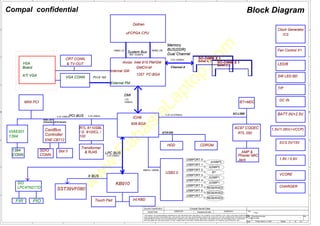

This Symbol as same

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

T34 PAD

DDR

SYSTEM

MEMORY

B

U5D

ALVISO_BGA1257

SBDQ0

AE31

SBDQ1

AE32

SBDQ2

AG32

SBDQ3

AG36

SBDQ4

AE34

SBDQ5 AE33

SBDQ6 AF31

SBDQ7 AF30

SBDQ8 AH33

SBDQ9 AH32

SBDQ10 AK31

SBDQ11 AG30

SBDQ12 AG34

SBDQ13 AG33

SBDQ14 AH31

SBDQ15 AJ31

SBDQ16 AK30

SBDQ17 AJ30

SBDQ18 AH29

SBDQ19 AH28

SBDQ20 AK29

SBDQ21 AH30

SBDQ22 AH27

SBDQ23 AG28

SBDQ24 AF24

SBDQ25 AG23

SBDQ26 AJ22

SBDQ27 AK22

SBDQ28 AH24

SBDQ29 AH23

SBDQ30 AG22

SBDQ31 AJ21

SBDQ32 AG10

SBDQ33

AG9

SBDQ34

AG8

SBDQ35

AH8

SBDQ36

AH11

SBDQ37

AH10

SBDQ38

AJ9

SBDQ39

AK9

SBDQ40

AJ7

SBDQ41

AK6

SBDQ42

AJ4

SBDQ43

AH5

SBDQ44

AK8

SBDQ45

AJ8

SBDQ46

AJ5

SB_BS0#

AJ15

SB_BS1#

AG17

SB_BS2#

AG21

SBDQ47

AK4

SBDQ48

AG5

SBDQ49

AG4

SBDQ50

AD8

SBDQ51

AD9

SBDQ52

AH4

SBDQ53

AG6

SBDQ54

AE8

SBDQ55

AD7

SBDQ56

AC5

SBDQ57

AB8

SBDQ58

AB6

SBDQ59

AA8

SBDQ60

AC8

SBDQ61

AC7

SBDQ62

AA4

SBDQ63

AA5

SB_CAS#

AH14

SB_RAS#

AK14

SB_RCVENIN#

AF15

SB_RCVENOUT#

AF14

SB_WE#

AH16

SB_MA0

AH17

SB_MA1

AK17

SB_MA2

AH18

SB_MA3

AJ18

SB_MA4

AK18

SB_MA5

AJ19

SB_MA6

AK19

SB_MA7

AH19

SB_MA8

AJ20

SB_MA9

AH20

SB_MA10

AJ16

SB_MA11

AG18

SB_MA12

AG20

SB_MA13

AG15

SB_DQS0#

AF35

SB_DQS1#

AK33

SB_DQS2#

AK28

SB_DQS3#

AJ23

SB_DQS4#

AL10

SB_DQS5#

AH7

SB_DQS6#

AF7

SB_DQS7#

AB5

SB_DQS0

AF34

SB_DQS1

AK32

SB_DQS2

AJ28

SB_DQS3

AK23

SB_DQS4

AM10

SB_DQS5

AH6

SB_DQS6

AF8

SB_DQS7

AB4

SB_DM0

AF32

SB_DM1

AK34

SB_DM2

AK27

SB_DM3

AK24

SB_DM4

AJ10

SB_DM5

AK5

SB_DM6

AE7

SB_DM7

AB7

DDR

MEMORY

SYSTEM

A

U5C

ALVISO_BGA1257

SADQ0

AG35

SADQ1

AH35

SADQ2

AL35

SADQ3

AL37

SADQ4

AH36

SADQ5 AJ35

SADQ6 AK37

SADQ7 AL34

SADQ8 AM36

SADQ9 AN35

SADQ10 AP32

SADQ11 AM31

SADQ12 AM34

SADQ13 AM35

SADQ14 AL32

SADQ15 AM32

SADQ16 AN31

SADQ17 AP31

SADQ18 AN28

SADQ19 AP28

SADQ20 AL30

SADQ21 AM30

SADQ22 AM28

SADQ23 AL28

SADQ24 AP27

SADQ25 AM27

SADQ26 AM23

SADQ27 AM22

SADQ28 AL23

SADQ29 AM24

SADQ30 AN22

SADQ31 AP22

SADQ32 AM9

SADQ33

AL9

SADQ34

AL6

SADQ35

AP7

SADQ36

AP11

SADQ37

AP10

SADQ38

AL7

SADQ39

AM7

SADQ40

AN5

SADQ41

AN6

SADQ42

AN3

SADQ43

AP3

SADQ44

AP6

SADQ45

AM6

SADQ46

AL4

SADQ47

AM3

SADQ48

AK2

SADQ49

AK3

SADQ50

AG2

SADQ51

AG1

SADQ52

AL3

SADQ53

AM2

SADQ54

AH3

SADQ55

AG3

SADQ56

AF3

SADQ57

AE3

SADQ58

AD6

SADQ59

AC4

SADQ60

AF2

SADQ61

AF1

SADQ62

AD4

SADQ63

AD5

SA_BS0#

AK15

SA_BS1#

AK16

SA_BS2#

AL21

SA_DM0

AJ37

SA_DM1

AP35

SA_DM2

AL29

SA_DM3

AP24

SA_DM4

AP9

SA_DM5

AP4

SA_DM6

AJ2

SA_DM7

AD3

SA_DQS0

AK36

SA_DQS1

AP33

SA_DQS2

AN29

SA_DQS3

AP23

SA_DQS4

AM8

SA_DQS5

AM4

SA_DQS6

AJ1

SA_DQS7

AE5

SA_DQS0#

AK35

SA_DQS1#

AP34

SA_DQS2#

AN30

SA_DQS3#

AN23

SA_DQS4#

AN8

SA_DQS5#

AM5

SA_DQS6#

AH1

SA_DQS7#

AE4

SA_MA0

AL17

SA_MA1

AP17

SA_MA2

AP18

SA_MA3

AM17

SA_MA4

AN18

SA_MA5

AM18

SA_MA6

AL19

SA_MA7

AP20

SA_MA8

AM19

SA_MA9

AL20

SA_MA10

AM16

SA_MA11

AN20

SA_MA12

AM20

SA_MA13

AM15

SA_CAS#

AN15

SA_RAS#

AP16

SA_RCVENIN#

AF29

SA_RCVENOUT#

AF28

SA_WE#

AP15

T38 PAD

T35 PAD

T36 PAD T33 PAD

T37 PAD](https://image.slidesharecdn.com/acer80a-231231163455-e3ad905d/85/ACER-80A-pdf-9-320.jpg)

![w

w

w

.

R

a

h

a

s

i

a

L

a

p

t

o

p

.

c

o

m

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

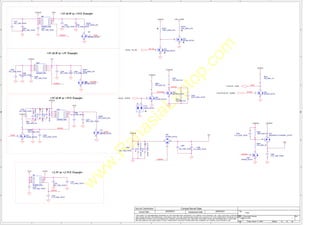

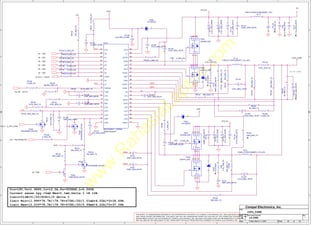

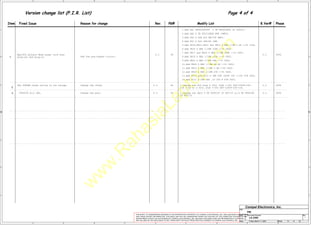

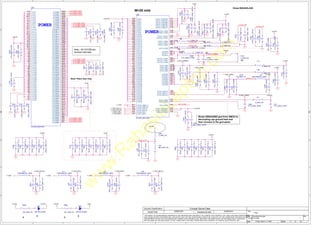

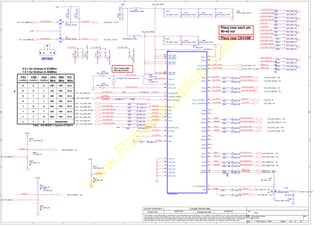

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN7

PEG_RXN6

PEG_RXN8

PEG_RXN9

PEG_RXN11

PEG_RXN10

PEG_RXN14

PEG_RXN15

PEG_RXN13

PEG_RXN12

PEG_RXP1

PEG_RXP3

PEG_RXP2

PEG_RXP6

PEG_RXP7

PEG_RXP5

PEG_RXP4

PEG_RXP11

PEG_RXP9

PEG_RXP8

PEG_RXP12

PEG_RXP13

PEG_RXP15

PEG_RXP14

PEG_RXP10

PEG_TXN0

PEG_TXN1

PEG_TXN3

PEG_TXN2

PEG_TXN6

PEG_TXN7

PEG_TXN5

PEG_TXN4

PEG_TXN11

PEG_TXN9

PEG_TXN8

PEG_TXN12

PEG_TXN13

PEG_TXN15

PEG_TXN14

PEG_TXN10

PEG_TXP0

PEG_TXP1

PEG_TXP3

PEG_TXP2

PEG_TXP6

PEG_TXP7

PEG_TXP5

PEG_TXP4

PEG_TXP11

PEG_TXP9

PEG_TXP8

PEG_TXP12

PEG_TXP13

PEG_TXP15

PEG_TXP14

PEG_TXP10

PEG_RXN[0..15]

PEG_TXN[0..15]

PEG_TXP[0..15]

PEG_RXP[0..15]

PEG_RXP0

PEGCOMP

LVDS_A0-

LVDS_A1-

LVDS_A2-

LVDS_A1+

LVDS_A2+

LVDS_A0+

LVDS_B1-

LVDS_B2-

LVDS_B0+

LVDS_B1+

LVDS_B2+

LVDS_B0-

LVDS_BC+

LVDS_BC-

LVDS_AC+

LVDS_AC-

CLK_DDC2

DAT_DDC2

LCD_CLK

LCD_DAT

LCD_CLK

LCD_DAT

BIA

BK_EN

LCTLA_CLK

LCTLB_DAT

LCTLA_CLK

LCTLB_DAT

EN_LCDVDD

CLK_DDC2

DAT_DDC2

BIA

<16,32>

Y/G

<17>

COMP/B

<17>

C/R

<17>

CLK_MCH_3GPLL#

<18>

CLK_MCH_3GPLL

<18>

CLK_DDC2

<17>

VSYNC

<17>

HSYNC

<17>

DAT_DDC2

<17>

CRT_BLU

<17>

CRT_GRN

<17>

CRT_RED

<17>

BK_EN

<16>

LVDS_AC-

<16>

LVDS_AC+

<16>

LVDS_BC-

<16>

LVDS_BC+

<16>

LVDS_A0-

<16>

LVDS_A1-

<16>

LVDS_A2-

<16>

LVDS_A0+

<16>

LVDS_A1+

<16>

LVDS_A2+

<16>

LVDS_B0-

<16>

LVDS_B1-

<16>

LVDS_B2-

<16>

LVDS_B0+

<16>

LVDS_B1+

<16>

LVDS_B2+

<16>

EN_LCDVDD

<16>

LCD_CLK

<16>

LCD_DAT

<16>

PEG_RXN[0..15] <16>

PEG_RXP[0..15] <16>

PEG_TXN[0..15] <16>

PEG_TXP[0..15] <16>

+1.5VS_PCIE

+2.5VS

+2.5VS

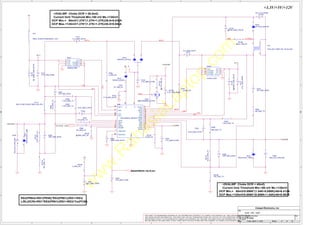

Title

Size Document Number Rev

Date: Sheet of

Security Classification Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date Deciphered Date

LA-2362 1

<Title>

Custom

10 52

Friday, March 11, 2005

2005/03/01 2006/03/01

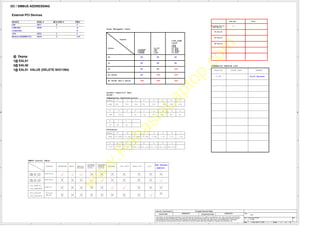

This Symbol as same

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

R29 3K_0402_5%

@

1 2

R364 2.2K_0402_5%

1 2

R362 2.2K_0402_5%

1 2

R363 2.2K_0402_5%

1 2

R30

3K_0402_5%

@

1 2

R34

150_0402_1%

1@

1

2

R3781.5K_0402_1%

1

2

MISC

TV

VGA

LVDS

PCI

-

EXPRESS

GRAPHICS

U5G

ALVISO_BGA1257

SDVOCTRL_DATA

H24

SDVOCTRL_CLK

H25

GCLKN

AB29

GCLKP

AC29

TVDAC_A

A15

TVDAC_B

C16

TVDAC_C

A17

TV_REFSET

J18

TV_IRTNA

B15

TV_IRTNB

B16

TV_IRTNC

B17

GREEN#

B20

HSYNC

G21

DDCCLK

E24

DDCDATA

E23

BLUE

E21

BLUE#

D21

GREEN

C20

RED

A19

RED#

B19

VSYNC

H21

REFSET

J20

LDDC_CLK

F23

LBKLT_CTL

E25

LBKLT_EN

F25

LCTLA_CLK

C23

LCTLB_DATA

C22

LDDC_DATA

F22

LVDD_EN

F26

LIBG

C33

LVBG

C31

LVREFH

F28

LVREFL

F27

LACLKN

B30

LACLKP

B29

LBCLKN

C25

LBCLKP

C24

LADATAN0

B34

LADATAN1

B33

LADATAN2

B32

LADATAP0

A34

LADATAP1

A33

LADATAP2

B31

LBDATAN0

C29

LBDATAN1

D28

LBDATAN2

C27

LBDATAP2

C26

EXP_COMPI

D36

EXP_ICOMPO

D34

EXP_RXN0/SDVO_TVCLKIN#

E30

EXP_RXN1/SDVO_INT#

F34

EXP_RXN2/SDVO_FLDSTALL#

G30

EXP_RXN3

H34

EXP_RXN4

J30

EXP_RXN5

K34

EXP_RXN6

L30

EXP_RXN7

M34

EXP_RXN8

N30

EXP_RXN9

P34

EXP_RXN10

R30

EXP_RXN11 T34

EXP_RXN12 U30

EXP_RXN13 V34

EXP_RXN14 W30

EXP_RXN15 Y34

EXP_RXP0/SDVO_TVCLKIN D30

EXP_RXP1/SDVO_INT E34

EXP_RXP2/SDVO_FLDSTALL F30

EXP_RXP3 G34

EXP_RXP4 H30

EXP_RXP5 J34

EXP_RXP6 K30

EXP_RXP7 L34

EXP_RXP8 M30

EXP_RXP9 N34

EXP_RXP10 P30

EXP_RXP11 R34

EXP_RXP12 T30

EXP_RXP13 U34

EXP_RXP14 V30

EXP_RXP15 W34

EXP_TXN0/SDVOB_RED# E32

EXP_TXN1/SDVOB_GREEN# F36

EXP_TXN2/SDVOB_BLUE# G32

EXP_TXN3/SDVOB_CLKN H36

EXP_TXN4/SDVOC_RED# J32

EXP_TXN5/SDVOC_GREEN#

K36

EXP_TXN6/SDVOC_BLUE#

L32

EXP_TXN7/SDVOC_CLKN

M36

EXP_TXN8

N32

EXP_TXN9

P36

EXP_TXN10

R32

EXP_TXN11

T36

EXP_TXN12

U32

EXP_TXN13

V36

EXP_TXN14

W32

EXP_TXN15

Y36

EXP_TXP0/SDVOB_RED

D32

EXP_TXP1/SDVOB_GREEN

E36

EXP_TXP2/SDVOB_BLUE

F32

EXP_TXP3/SDVOB_CLKP

G36

EXP_TXP4/SDVOC_RED

H32

EXP_TXP5/SDVOC_GREEN

J36

EXP_TXP6/SDVOC_BLUE

K32

EXP_TXP7/SDVOC_CLKP

L36

EXP_TXP8

M32

EXP_TXP9

N36

EXP_TXP10

P32

EXP_TXP11

R36

EXP_TXP12

T32

EXP_TXP13

U36

EXP_TXP14

V32

EXP_TXP15

W36

LBDATAP0

C28

LBDATAP1

D27

R429

255_0402_1%

1 2

R33

150_0402_1%

1@

1

2

R396 100K_0402_1%

1 2

R385 2.2K_0402_5%

1 2

R428

4.99K_0603_1%

1

2

R360 2.2K_0402_5%

1 2

R392

0_0402_5%

1@

1 2

R361 2.2K_0402_5%

1 2

R32

150_0402_1%

1@

1

2

R404100K_0402_1%

1 2

R40

24.9_0603_1%

1 2](https://image.slidesharecdn.com/acer80a-231231163455-e3ad905d/85/ACER-80A-pdf-10-320.jpg)

![w

w

w

.

R

a

h

a

s

i

a

L

a

p

t

o

p

.

c

o

m

A

A

B

B

C

C

D

D

E

E

F

F

G

G

H

H

1 1

2 2

3 3

4 4

DDR_A_BS#1

DDR_A_MA9

DDR_A_MA12

DDR_A_MA11

DDR_A_MA6

DDR_A_MA3

DDR_A_MA0

DDR_A_MA10

DDR_A_MA1

DDR_A_MA2

DDR_A_MA5

DDR_A_CAS#

DDR_A_RAS#

DDR_A_BS#0

DDR_A_WE#

DDR_A_MA8

DDR_A_MA7

DDR_A_MA4

DDR_A_D[0..63]

DDR_A_DM[0..7]

DDR_A_MA[0..13]

DDR_A_DQS[0..7]

DDR_A_D24

DDR_A_D19

DDR_A_D1

DDR_A_D2

DDR_A_D5

DDR_A_D3

DDR_A_DM0

DDR_A_DQS0

DDR_A_D0

DDR_A_D13

DDR_A_D7

DDR_A_D8

DDR_A_D6

DDR_A_D9

DDR_A_DM1

DDR_A_D12

DDR_A_DQS1

DDR_A_D11

DDR_A_D14

DDR_A_D20

DDR_A_D21

DDR_A_D17

DDR_A_D15

DDR_A_D10

DDR_A_D16

DDR_A_D28

DDR_A_D23

DDR_A_D22

DDR_A_DM2

DDR_A_D18

DDR_A_DQS2

DDR_CKE1

DDR_SCS#1

DDR_SCS#0

DDR_CKE0

CK_SCLK

DDR_CKE1 DDR_CKE0

DDR_SCS#0 DDR_SCS#1

DDR_A_MA5

DDR_A_MA3

DDR_A_MA7

DDR_A_MA1

DDR_A_MA12

DDR_A_MA9

DDR_A_MA10

DDR_DQS0

DDR_DQS2

DDR_DQS1

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_A_WE#

DDR_A_BS#0

DDR_D6

DDR_D4

DDR_D2

DDR_D0

DDR_D10

DDR_D8

DDR_D12

DDR_D14

DDR_D22

DDR_D18

DDR_D20

DDR_D24

DDR_D26

DDR_D16

DDR_D28

DDR_D30

DDR_D39

DDR_D35

DDR_D41

DDR_D33

DDR_D36

DDR_D45

DDR_A_MA0

DDR_A_MA2

DDR_A_MA6

DDR_A_MA4

DDR_A_MA8

DDR_A_MA11

DDR_DM6

DDR_DM3

DDR_DM0

DDR_DM1

DDR_DM7

DDR_DM2

DDR_DM4

DDR_DM5

DDR_A_CAS#

DDR_A_RAS#

DDR_A_BS#1

DDR_D11

DDR_D9

DDR_D23

DDR_D21

DDR_D27

DDR_D29

DDR_D25

DDR_D34

DDR_D32

DDR_D37

DDR_D47

DDR_D43

DDR_D40

DDR_D51

DDR_D44

DDR_D49

DDR_D48

DDR_D62

DDR_D61

DDR_D57

DDR_D42

DDR_D46

DDR_DQS6

DDR_D19

DDR_D56

DDR_D50

DDR_D17

DDR_D38

DDR_D31

DDR_D55

CK_SDATA

DDR_D5

DDR_D54

DDR_D7

DDR_D15

DDR_D1

DDR_D60

DDR_DQS7

DDR_D53

DDR_D3

DDR_D13

DDR_D52

DDR_A_DQS3

DDR_A_D29

DDR_A_DM3

DDR_A_D25

DDR_A_D31

DDR_A_D26

DDR_A_D30

DDR_A_D27

DDR_A_D36

DDR_A_D34

DDR_A_DQS4

DDR_A_D38

DDR_A_D35

DDR_A_D32

DDR_A_D33

DDR_A_D37

DDR_A_D39

DDR_A_DM4

DDR_A_MA13

DDR_D63

DDR_D59

DDR_A_MA13

DDR_D4

DDR_D1

DDR_D5

DDR_D2

DDR_A_D60

DDR_A_DQS7

DDR_A_D59

DDR_A_D62

DDR_A_D56

DDR_A_D61

DDR_A_D51

DDR_A_D50

DDR_A_D57

DDR_A_DQS6

DDR_A_D55

DDR_A_DQS5

DDR_A_D45

DDR_A_D44

DDR_A_D43

DDR_A_D48

DDR_A_D42

DDR_A_D47

DDR_A_D53

DDR_A_D49

DDR_A_D46

DDR_A_D52

DDR_A_D41

DDR_A_D40

DDR_A_D54

DDR_A_DM5

DDR_A_DM7

DDR_A_DM6

DDR_A_D63

DDR_A_D58

DDR_DM0

DDR_D3

DDR_DQS0

DDR_D0

DDR_D7

DDR_D6

DDR_D13

DDR_D11

DDR_D10

DDR_D8

DDR_D9

DDR_DM1

DDR_D12

DDR_DQS1

DDR_D14

DDR_D15

DDR_D20

DDR_D21

DDR_D16

DDR_D17

DDR_DQS2

DDR_D18

DDR_DM2

DDR_D22

DDR_D23

DDR_D19

DDR_D28

DDR_D24

DDR_D29

DDR_DQS3

DDR_D25

DDR_DM3

DDR_D31

DDR_D26

DDR_D30

DDR_D27

DDR_D36

DDR_D37

DDR_D33

DDR_D32

DDR_D34

DDR_D35

DDR_D38

DDR_D39

DDR_DQS4

DDR_DM4

DDR_D44

DDR_D41

DDR_D40

DDR_D45

DDR_DQS5

DDR_D43

DDR_D42

DDR_D46

DDR_D47

DDR_DM5

DDR_D53

DDR_D48

DDR_D52

DDR_D49

DDR_D55

DDR_D54

DDR_D50

DDR_D51

DDR_DM6

DDR_DQS6

DDR_D58

DDR_D63

DDR_D61

DDR_D57

DDR_D56

DDR_DM7

DDR_D59

DDR_D62

DDR_D60

DDR_DQS7

DDR_A_D4

DDR_D[0..63]

DDR_DM[0..7]

DDR_DQS[0..7]

DDR_D58

DDR_A_D[0..63]

<9>

DDR_A_DM[0..7]

<9>

DDR_A_DQS[0..7]

<9>

DDR_D[0..63] <14>

DDR_DM[0..7] <14>

DDR_DQS[0..7] <14>

DDR_A_MA[0..13]

<9>

DDR_CLK0

<8>

DDR_CLK0#

<8>

DDR_CKE1

<8>

DDR_SCS#0

<8>

DDR_A_BS#0

<9>

DDR_A_WE#

<9>

CK_SDATA

<14,18>

CK_SCLK

<14,18>

DDR_CLK1 <8>

DDR_CLK1# <8>

DDR_SCS#1 <8>

DDR_A_CAS# <9>

DDR_A_RAS# <9>

DDR_A_BS#1 <9>

DDR_CKE0 <8>

+1.25VS

+2.5V

+3VS

+SDREF

+SDREF_DIMM

+2.5V

Title

Size Document Number Rev

Date: Sheet of

Security Classification Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date Deciphered Date

LA-2362 1

<Title>

B

13 52

Friday, March 11, 2005

2005/03/01 2006/03/01

R679 10_0402_5%

1 2

R668 10_0402_5%

1 2

R252 10_0402_5%

1 2

R263 10_0402_5%

1 2

R234 10_0402_5%

1 2

R247 10_0402_5%

1 2

R240 10_0402_5%

1 2

R678 56_0402_5%

1 2

R647 10_0402_5%

1 2

R655 10_0402_5%

1 2

R270 10_0402_5%

1 2

R664 10_0402_5%

1 2

R666 10_0402_5%

1 2

R264 10_0402_5%

1 2

R269 10_0402_5%

1 2

R649 10_0402_5%

1 2

R249 10_0402_5%

1 2

R670 10_0402_5%

1 2

R659 10_0402_5%

1 2

R665 10_0402_5%

1 2

R268 10_0402_5%

1 2

R661 10_0402_5%

1 2

JDIMM2

TYCO_1612560-1

VREF

1

VSS

3

DQ0

5

DQ1

7

VDD

9

DQS0

11

DQ2

13

VSS

15

DQ3

17

DQ8

19

VDD

21

DQ9

23

DQS1

25

VSS

27

DQ10

29

DQ11

31

VDD

33

CK0

35

CK0#

37

VSS

39

DQ16

41

DQ17

43

VDD

45

DQS2

47

DQ18

49

VSS

51

DQ19

53

DQ24

55

VDD

57

DQ25

59

DQS3

61

VSS

63

DQ26

65

DQ27

67

VDD

69

CB0

71

CB1

73

VSS

75

DQS8

77

CB2

79

VDD

81

CB3

83

DU

85

VSS

87

CK2

89

CK2#

91

VDD

93

CKE1

95

DU

97

A12

99

A9

101

VSS

103

A7

105

A5

107

A3

109

A1

111

VDD

113

A10/AP

115

BA0

117

WE#

119

S0#

121

DU/A13

123

VSS

125

DQ32

127

DQ33

129

VDD

131

DQS4

133

DQ34

135

VSS

137

DQ35

139

DQ40

141

VDD

143

VREF 2

VSS 4

DQ4

6

DQ5

8

VDD

10

DM0

12

DQ6

14

VSS

16

DQ7

18

DQ12

20

VDD

22

DQ13

24

DM1

26

VSS

28

DQ14

30

DQ15

32

VDD 34

VDD 36

VSS 38

VSS 40

DQ20 42

DQ21 44

VDD 46

DM2 48

DQ22 50

VSS 52

DQ23 54

DQ28 56

VDD 58

DQ29 60

DM3 62

VSS 64

DQ30 66

DQ31 68

VDD 70

CB4 72

CB5 74

VSS 76

DM8 78

CB6 80

VDD 82

CB7 84

DU/RESET#

86

VSS

88

VSS

90

VDD

92

VDD

94

CKE0

96

DU

98

A11

100

A8

102

VSS

104

A6

106

A4

108

A2

110

A0

112

VDD

114

BA1

116

RAS#

118

CAS#

120

S1#

122

DU

124

VSS

126

DQ36

128

DQ37

130

VDD

132

DM4

134

DQ38

136

VSS

138

DQ39

140

DQ44

142

VDD

144

DQ41

145

DQS5

147

VSS

149

DQ42

151

DQ43

153

VDD

155

VDD

157

VSS

159

VSS

161

DQ48

163

DQ49

165

VDD

167

DQS6

169

DQ50

171

VSS

173

DQ51

175

DQ56

177

VDD

179

DQ57

181

DQS7

183

VSS

185

DQ58

187

DQ59

189

VDD

191

SDA

193

SCL

195

VDD_SPD

197

VDD_ID

199

DQ45

146

DM5

148

VSS

150

DQ46

152

DQ47

154

VDD

156

CK1#

158

CK1

160

VSS

162

DQ52

164

DQ53

166

VDD

168

DM6

170

DQ54

172

VSS

174

DQ55

176

DQ60

178

VDD

180

DQ61

182

DM7

184

VSS

186

DQ62

188

DQ63

190

VDD

192

SA0

194

SA1

196

SA2 198

DU 200

R277 56_0402_5%

1 2

C237

0.1U_0402_16V4Z

1

2

R265 10_0402_5%

1 2

R256 10_0402_5%

1 2

R288 56_0402_5%

1 2

R691 10_0402_5%

1 2

R674 56_0402_5%

1 2

R235 10_0402_5%

1 2

R251 10_0402_5%

1 2

R652 10_0402_5%

1 2

R683 10_0402_5%

1 2

R693 10_0402_5%

1 2

R676 56_0402_5%

1 2

R287 56_0402_5%

1 2

R236 10_0402_5%

1 2

R266 10_0402_5%

1 2

R677 56_0402_5%

1 2

R250 10_0402_5%

1 2

R684 10_0402_5%

1 2

R646 10_0402_5%

1 2

R245 10_0402_5%

1 2

R271 10_0402_5%

1 2

R257 10_0402_5%

1 2

R282 56_0402_5%

1 2

R648 10_0402_5%

1 2

R283 56_0402_5%

1 2

R237 10_0402_5%

1 2

R660 10_0402_5%

1 2

R242 10_0402_5%

1 2

R286 56_0402_5%

1 2

R260 10_0402_5%

1 2

R656 10_0402_5%

1 2

R657 10_0402_5%

1 2

R241 10_0402_5%

1 2

R685 10_0402_5%

1 2

R294 56_0402_5%

1 2

R688 10_0402_5%

1 2

R280 56_0402_5%

1 2

R681 10_0402_5%

1 2

R253 10_0402_5%

1 2

R650 10_0402_5%

1 2

R672 56_0402_5%

1 2

R244 10_0402_5%

1 2

R238 10_0402_5%

1 2

R673 56_0402_5%

1 2

R279 56_0402_5%

1 2

R682 10_0402_5%

1 2

R690 10_0402_5%

1 2

R267 10_0402_5%

1 2

R243 10_0402_5%

1 2

R274 10_0402_5%

1 2

R692 10_0402_5%

1 2

R254 10_0402_5%

1 2

R651 10_0402_5%

1 2

R675 56_0402_5%

1 2

R680 10_0402_5%

1 2

R275 56_0402_5%

1 2

R248 10_0402_5%

1 2

R246 10_0402_5%

1 2

R255 10_0402_5%

1 2

R273 10_0402_5%

1 2

R663 10_0402_5%

1 2

R276 56_0402_5%

1 2

R653 10_0402_5%

1 2

R278 56_0402_5%

1 2

R233 10_0402_5%

1 2

R296 56_0402_5%

1 2

R295 56_0402_5%

1 2

R239 10_0402_5%

1 2

R281 56_0402_5%

1 2

R261 10_0402_5%

1 2

R272 10_0402_5%

1 2

R654 10_0402_5%

1 2

R658 10_0402_5%

1 2

R662 10_0402_5%

1 2

R687 10_0402_5%

1 2

R686 10_0402_5%

1 2

R689 10_0402_5%

1 2

R669 10_0402_5%

1 2

R262 10_0402_5%

1 2

R227

0_0402_5%

1

2

R293 56_0402_5%

1 2

R667 10_0402_5%

1 2](https://image.slidesharecdn.com/acer80a-231231163455-e3ad905d/85/ACER-80A-pdf-13-320.jpg)

![w

w

w

.

R

a

h

a

s

i

a

L

a

p

t

o

p

.

c

o

m

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

CK_SCLK

DDR_SCS#2

DDR_CKE3

DDR_SCS#3

DDR_CKE2

DDR_B_MA5

DDR_B_MA3

DDR_B_MA7

DDR_B_MA0

DDR_B_MA2

DDR_B_MA1

DDR_B_MA12

DDR_B_MA9

DDR_B_MA6

DDR_B_MA4

DDR_B_MA10

DDR_B_MA8

DDR_B_MA11

CK_SDATA

DDR_B_CAS#

DDR_B_WE#

DDR_B_RAS#

DDR_B_BS#0

DDR_B_BS#1

DDR_B_MA[0..13]

DDR_B_BS#1

DDR_B_MA9

DDR_B_MA12

DDR_B_MA11

DDR_B_MA0

DDR_B_MA10

DDR_B_MA1

DDR_B_MA2

DDR_B_MA5

DDR_B_CAS#

DDR_B_RAS#

DDR_B_BS#0

DDR_B_WE#

DDR_B_MA7

DDR_B_MA4

DDR_B_MA8

DDR_B_MA3

DDR_B_MA6

DDR_SCS#2

DDR_SCS#3

DDR_CKE2

DDR_CKE3

DDR_B_MA13

DDR_B_MA13

DDR_D[0..63]

DDR_DM[0..7]

DDR_DQS[0..7]

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

DDR_D6

DDR_D4

DDR_D2

DDR_D0

DDR_D10

DDR_D8

DDR_D12

DDR_D14

DDR_D22

DDR_D18

DDR_D20

DDR_D24

DDR_D26

DDR_D16

DDR_D28

DDR_D30

DDR_D39

DDR_D35

DDR_D41

DDR_D33

DDR_D42

DDR_D46

DDR_D36

DDR_D45

DDR_D54

DDR_D53

DDR_D57

DDR_D58

DDR_D50

DDR_D60

DDR_D52

DDR_D59

DDR_DM3

DDR_DM0

DDR_DM1

DDR_DM6

DDR_DM7

DDR_DM2

DDR_DM4

DDR_DM5

DDR_D11

DDR_D5

DDR_D7

DDR_D1

DDR_D3

DDR_D9

DDR_D23

DDR_D19

DDR_D15

DDR_D13

DDR_D21

DDR_D27

DDR_D29

DDR_D17

DDR_D31

DDR_D25

DDR_D34

DDR_D32

DDR_D37

DDR_D47

DDR_D38

DDR_D43

DDR_D40

DDR_D44

DDR_D51

DDR_D55

DDR_D63

DDR_D49

DDR_D48

DDR_D62

DDR_D61

DDR_D56

DDR_D4

DDR_D1

DDR_D5

DDR_D2

DDR_DM0

DDR_D3

DDR_DQS0

DDR_D0

DDR_D7

DDR_D6

DDR_D13

DDR_D11

DDR_D10

DDR_D8

DDR_D9

DDR_DM1

DDR_D12

DDR_DQS1

DDR_D14

DDR_D15

DDR_D20

DDR_D21

DDR_D16

DDR_D17

DDR_DQS2

DDR_D18

DDR_DM2

DDR_D22

DDR_D23

DDR_D19

DDR_D28

DDR_D24

DDR_D29

DDR_DQS3

DDR_D25

DDR_DM3

DDR_D31

DDR_D26

DDR_D30

DDR_D27

DDR_D36

DDR_D37

DDR_D33

DDR_D32

DDR_D34

DDR_D35

DDR_D38

DDR_D39

DDR_DQS4

DDR_DM4

DDR_D44

DDR_D41

DDR_D40

DDR_D45

DDR_DQS5

DDR_D43

DDR_D42

DDR_D46

DDR_D47

DDR_DM5

DDR_D53

DDR_D48

DDR_D52

DDR_D49

DDR_D55

DDR_D54

DDR_D50

DDR_D51

DDR_DM6

DDR_DQS6

DDR_D58

DDR_D63

DDR_D61

DDR_D57

DDR_D56

DDR_DM7

DDR_D59

DDR_D62

DDR_D60

DDR_DQS7

DDR_D[0..63] <13>

DDR_DM[0..7] <13>

DDR_DQS[0..7] <13>

DDR_B_MA[0..13]

<9>

DDR_CLK3

<8>

DDR_CLK3#

<8>

DDR_CKE3

<8>

DDR_SCS#2

<8>

DDR_B_BS#0

<9>

DDR_B_WE#

<9>

CK_SDATA

<13,18>

CK_SCLK

<13,18>

DDR_CLK4# <8>

DDR_CLK4 <8>

DDR_SCS#3 <8>

DDR_CKE2 <8>

DDR_B_BS#1 <9>

DDR_B_RAS# <9>

DDR_B_CAS# <9>

+1.25VS

+2.5V

+3VS

+2.5V

+SDREF_DIMM

+1.25VS

+3VS

Title

Size Document Number Rev

Date: Sheet of

Security Classification Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date Deciphered Date

LA-2362 1

<Title>

B

14 52

Friday, March 11, 2005

2005/03/01 2006/03/01

R591 56_0402_5%

1 2

R573 56_0402_5%

1 2

R206 56_0402_5%

1 2

R216 56_0402_5%

1 2

R582 56_0402_5%

1 2

R211 56_0402_5%

1 2

R571 56_0402_5%

1 2

R170 56_0402_5%

1 2

R186 56_0402_5%

1 2

R611 56_0402_5%

1 2

R205 56_0402_5%

1 2

R208 56_0402_5%

1 2

R580 56_0402_5%

1 2

R577 56_0402_5%

1 2

R184 56_0402_5%

1 2

R572 56_0402_5%

1 2

R593 56_0402_5%

1 2

R180 56_0402_5%

1 2

R606 56_0402_5%

1 2

R178 56_0402_5%

1 2

R213 56_0402_5%

1 2

R615 56_0402_5%

1 2

R576 56_0402_5%

1 2

R570 56_0402_5%

1 2

R587 56_0402_5%

1 2

R599 56_0402_5%

1 2

R201 56_0402_5%

1 2

R167 56_0402_5%

1 2

R565 56_0402_5%

1 2

R189 56_0402_5%

1 2

R602 56_0402_5%

1 2

R601 56_0402_5%

1 2

R609 56_0402_5%

1 2

R600 56_0402_5%

1 2

R586 56_0402_5%

1 2

R575 56_0402_5%

1 2

R612 56_0402_5%

1 2

R181 56_0402_5%

1 2

R212 56_0402_5%

1 2

R173 56_0402_5%

1 2

C188

0.1U_0402_16V4Z

1

2

R566 56_0402_5%

1 2

R168 56_0402_5%

1 2

R198 56_0402_5%

1 2

R182 56_0402_5%

1 2

R597 56_0402_5%

1 2

R603 56_0402_5%

1 2

R568 56_0402_5%

1 2

R574 56_0402_5%

1 2

R193 56_0402_5%

1 2

R195 56_0402_5%

1 2

R177 56_0402_5%

1 2

R605 56_0402_5%

1 2

R608 56_0402_5%

1 2

R191 56_0402_5%

1 2

R190 56_0402_5%

1 2

R175 56_0402_5%

1 2

R187 56_0402_5%

1 2

R578 56_0402_5%

1 2

R200 56_0402_5%

1 2

R610 56_0402_5%

1 2

R203 56_0402_5%

1 2

R595 56_0402_5%

1 2

R583 56_0402_5%

1 2

R592 56_0402_5%

1 2

R581 56_0402_5%

1 2

R204 56_0402_5%

1 2

R563 56_0402_5%

1 2

R171 56_0402_5%

1 2

R176 56_0402_5%

1 2

R562 56_0402_5%

1 2

R166 56_0402_5%

1 2

R209 56_0402_5%

1 2

R585 56_0402_5%

1 2

R614 56_0402_5%

1 2

R185 56_0402_5%

1 2

R199 56_0402_5%

1 2

R594 56_0402_5%

1 2

R179 56_0402_5%

1 2

JDIMM1

KLINK_5763-2-111

VREF

1

VSS

3

DQ0

5

DQ1

7

VDD

9

DQS0

11

DQ2

13

VSS

15

DQ3

17

DQ8

19

VDD

21

DQ9

23

DQS1

25

VSS

27

DQ10

29

DQ11

31

VDD

33

CK0

35

CK0#

37

VSS

39

DQ16

41

DQ17

43

VDD

45

DQS2

47

DQ18

49

VSS

51

DQ19

53

DQ24

55

VDD

57

DQ25

59

DQS3

61

VSS

63

DQ26

65

DQ27

67

VDD

69

CB0

71

CB1

73

VSS

75

DQS8

77

CB2

79

VDD

81

CB3

83

DU

85

VSS

87

CK2

89

CK2#

91

VDD

93

CKE1

95

DU/A13

97

A12

99

A9

101

VSS

103

A7

105

A5

107

A3

109

A1

111

VDD

113

A10/AP

115

BA0

117

WE#

119

S0#

121

DU

123

VSS

125

DQ32

127

DQ33

129

VDD

131

DQS4

133

DQ34

135

VSS

137

DQ35

139

DQ40

141

VDD

143

VREF 2

VSS 4

DQ4 6

DQ5 8

VDD 10

DM0 12

DQ6 14

VSS 16

DQ7 18

DQ12

20

VDD

22

DQ13

24

DM1

26

VSS

28

DQ14

30

DQ15

32

VDD

34

VDD

36

VSS

38

VSS

40

DQ20

42

DQ21 44

VDD 46

DM2 48

DQ22 50

VSS 52

DQ23 54

DQ28 56

VDD 58

DQ29 60

DM3 62

VSS 64

DQ30 66

DQ31 68

VDD 70

CB4 72

CB5 74

VSS 76

DM8 78

CB6 80

VDD 82

CB7 84

DU/RESET# 86

VSS 88

VSS 90

VDD 92

VDD 94

CKE0 96

DU/BA2 98

A11

100

A8

102

VSS

104

A6

106

A4

108

A2

110

A0

112

VDD

114

BA1

116

RAS#

118

CAS#

120

S1#

122

DU

124

VSS

126

DQ36

128

DQ37

130

VDD

132

DM4

134

DQ38

136

VSS

138

DQ39

140

DQ44

142

VDD

144

DQ41

145

DQS5

147

VSS

149

DQ42

151

DQ43

153

VDD

155

VDD

157

VSS

159

VSS

161

DQ48

163

DQ49

165

VDD

167

DQS6

169

DQ50

171

VSS

173

DQ51

175

DQ56

177

VDD

179

DQ57

181

DQS7

183

VSS

185

DQ58

187

DQ59

189

VDD

191

SDA

193

SCL

195

VDD_SPD

197

VDD_ID

199

DQ45

146

DM5

148

VSS

150

DQ46

152

DQ47

154

VDD

156

CK1#

158

CK1

160

VSS

162

DQ52

164

DQ53

166

VDD

168

DM6

170

DQ54

172

VSS

174

DQ55

176

DQ60

178

VDD

180

DQ61

182

DM7

184

VSS

186

DQ62

188

DQ63

190

VDD

192

SA0

194

SA1

196

SA2

198

DU

200

R613 56_0402_5%

1 2

R192 56_0402_5%

1 2

R207 56_0402_5%

1 2

R188 56_0402_5%

1 2

R567 56_0402_5%

1 2

R607 56_0402_5%

1 2

R196 56_0402_5%

1 2

R194 56_0402_5%

1 2

R172 56_0402_5%

1 2

R564 56_0402_5%

1 2

R165 56_0402_5%

1 2

R596 56_0402_5%

1 2

R197 56_0402_5%

1 2

R569 56_0402_5%

1 2

R604 56_0402_5%

1 2

R169 56_0402_5%

1 2

R210 56_0402_5%

1 2

R174 56_0402_5%

1 2

R183 56_0402_5%

1 2

R215 56_0402_5%

1 2

R598 56_0402_5%

1 2

R584 56_0402_5%

1 2

R214 56_0402_5%

1 2

R579 56_0402_5%

1 2

R202 56_0402_5%

1 2](https://image.slidesharecdn.com/acer80a-231231163455-e3ad905d/85/ACER-80A-pdf-14-320.jpg)

![w

w

w

.

R

a

h

a

s

i

a

L

a

p

t

o

p

.

c

o

m

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

B+P B+I

B+P

VGA_GRN

VGA_RED

VGA_BLU

VSYNC_VGA

CLK_PCIE_VGA#

HSYNCVGA

PEG_RXP0

PEG_RXN0

PEG_A_TXN_4

PEG_TXN4

PEG_A_TXP_3

PEG_A_TXP_4

PEG_A_TXN_3

PEG_TXN3

PEG_TXP4

PEG_TXN5

PEG_TXP5

PEG_TXP3

PEG_A_TXN_6

PEG_A_TXP_7

PEG_A_TXP_6

PEG_A_TXN_7

PEG_TXP7

PEG_TXN7

PEG_TXN6

PEG_TXP6

PEG_TXP14

PEG_A_TXP_11

PEG_A_TXN_11

PEG_TXN14

PEG_A_TXP_14

PEG_A_TXP_13

PEG_A_TXN_14

PEG_TXP11

PEG_TXN11

PEG_TXP10

PEG_TXP12

PEG_TXN10

PEG_TXN12

PEG_A_TXP_0

PEG_A_TXN_0

PEG_A_TXN_2

PEG_A_TXP_2

PEG_TXN2

PEG_TXN0

PEG_TXP2

PEG_TXP0

PEG_TXP15

PEG_TXN15 PEG_A_TXN_15

PEG_A_TXP_15

PEG_TXN1

PEG_TXP1

PEG_A_TXN_1

PEG_A_TXP_1

PEG_A_TXP_5

PEG_A_TXN_5

PEG_A_TXN_8

PEG_TXN8

PEG_A_TXP_8

PEG_TXP8

PEG_A_TXN_9

PEG_TXP9 PEG_A_TXP_9

PEG_TXN9

PEG_A_TXP_10

PEG_A_TXN_10

PEG_A_TXP_12

PEG_A_TXN_12

PEG_RXN6

PEG_RXP6

PEG_RXN9

PEG_RXP9

PEG_RXP8

PEG_RXN8

PEG_RXP7

PEG_RXN7

PEG_RXP14

PEG_RXN14

PEG_RXP1

PEG_RXN1

PEG_RXN2

PEG_RXP2

PEG_RXP13

PEG_RXN13

PEG_RXN3

PEG_RXP3

PEG_RXP12

PEG_RXN12

PEG_RXP11

PEG_RXN11

PEG_RXN4

PEG_RXP4

PEG_RXN5

PEG_RXP5

PEG_RXN10

PEG_RXP10

PEG_RXP11

PEG_RXN14

PEG_RXN15

PEG_RXP15

PEG_RXP0

PEG_RXP13

PEG_RXP4

PEG_RXN[0..15]

PEG_RXN5

PEG_RXN0

PEG_RXP6

PEG_RXP5

PEG_RXP2

PEG_RXP3

PEG_RXN3

PEG_RXP1

PEG_RXN12

PEG_RXN9

PEG_RXN13

PEG_RXN4

PEG_RXP15

PEG_RXN6

PEG_RXP8

PEG_RXN8

PEG_RXP9

PEG_RXN11

PEG_RXN1

PEG_RXN7

PEG_RXN2

PEG_RXP14

PEG_RXP7

PEG_RXN10

PEG_RXP10

PEG_RXP12

PEG_RXP[0..15]

PEG_RXN15

PEG_TXN5

PEG_TXN13

PEG_TXN10

PEG_TXN4

PEG_TXN9

PEG_TXP0

PEG_TXP6

PEG_TXP11

PEG_TXP5

PEG_TXP[0..15]

PEG_TXN2

PEG_TXP8

PEG_TXN1

PEG_TXP3

PEG_TXN12

PEG_TXP4

PEG_TXN14

PEG_TXP13

PEG_TXP2

PEG_TXP1

PEG_TXN13

PEG_TXN8

PEG_TXN15

PEG_TXP14

PEG_TXP15

PEG_TXP9

PEG_TXN3

PEG_A_TXN_13

PEG_TXN0

PEG_TXN11

PEG_TXN[0..15]

PEG_TXP12

PEG_TXP10

PEG_TXN7

PEG_TXN6

PEG_TXP7

PEG_TXP13

INVPWR_B+++

DISPLAYOFF#

LCDP_CLK

LCDP_DAT

LCDP_CLK

LCDP_DAT

CLK_PCIE_VGA

SUSP

RUNPWROK

PLTRST_VGA#

THERMATRIP_VGA#

SMBDAT_VGA

SMBCLK_VGA

SMB_EC_CK2

SMB_EC_DA2

LVDS_B0+

LVDS_B2-

LVDS_B0-

LVDS_B2+

LVDS_BC+

LVDS_BC-

LVDS_A2+

LVDS_A2-

LVDS_A0-

LVDS_AC+

LVDS_AC-

LVDS_A1-

LVDS_A1+

LVDS_A0+

LVDS_B1-

LVDS_B1+

PWM

DISPLAYOFF#

PWM

BK_EN

<10>

BKOFF#

<32>

BIA

<10,32>

INVT_PWM

<32>

RUNPWROK

PLTRST_VGA# <19,21>

THERMATRIP_VGA# <32>

SUSP <37,43,44>

CLK_PCIE_VGA# <18>

CLK_PCIE_VGA <18>

DAC_BRIG <32>

BKOFF# <32>

INVT_PWM <32>

PEG_TXP[0..15] <10>

PEG_RXN[0..15] <10> PEG_TXN[0..15]

<10>

PEG_RXP[0..15] <10>

LCD_CLK

<10>

LCD_DAT

<10>

EN_LCDVDD

<10>

DAC_BRIG <32>

LVDS_A0+

<10>

LVDS_A0-

<10>

LVDS_A1+

<10>

LVDS_A1-

<10>

LVDS_A2-

<10>

LVDS_A2+

<10>

LVDS_AC-

<10>

LVDS_AC+

<10>

LVDS_B0-

<10>

LVDS_B0+

<10>

LVDS_B2-

<10>

LVDS_B2+

<10>

LVDS_B1-

<10>

LVDS_B1+

<10>

LVDS_BC-

<10>

LVDS_BC+

<10>

SUSP#

<24,32,33,37,42>

SMB_EC_CK2

<32,34>

SMB_EC_DA2

<32,34>

SMBDAT_VGA

<17>

C/R_VGA

<17>

COMP/B_VGA

<17>

Y/G_VGA

<17>

VSYNC_VGA

<17>

HSYNC_VGA

<17>

VGA_BLU

<17>

VGA_GRN

<17>

VGA_RED

<17>

SMBCLK_VGA

<17>

+LCDVDD

+12VALW +LCDVDD +3VS

INVPWR_B+

+5VS

+3VS

+12VALW

+LCDVDD

INVPWR_B+

+5VALW

+2.5VS

+3VS

+5VS

+3VS

+5VS

+3VS

+2.5V

+3VS

B+ B+I

B+I

Title

Size Document Number Rev

Date: Sheet of

Security Classification Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date Deciphered Date

LA-2362 1

<Title>

Custom

16 52

Friday, March 11, 2005

2005/03/01 2006/03/01

Inverter

LCD EEPROM

Modify for 1.8vs move to VGA BD

FBM-201209-121LMA40T

C309

0.047U_0402_16V4Z

1

2

C54 0.1U_0402_16V4Z

2@ 1 2

C88 0.1U_0402_16V4Z

2@ 1 2

C66 0.1U_0402_16V4Z

2@ 1 2

C83 0.1U_0402_16V4Z

2@ 1 2

C51 0.1U_0402_16V4Z

2@ 1 2

JVGA1

FOX_QTS0140A-3021

2@

1 1

3 3

5 5

7 7

9 9

11 11

13 13

15 15

17 17

19 19

21 21

23 23

25 25

27 27

29 29

31 31

33 33

35 35

37 37

39 39

41 41

43 43

45 45

47 47

49 49

51 51

53 53

55 55

57 57

59 59

61 61

63 63

65 65

67 67

69 69

71 71

73 73

75 75

77 77

79 79

81 81

83 83

85 85

87 87

89 89

91 91

93 93

95 95

97 97

99 99

101 101

103 103

105 105

107 107

109 109

111 111

113 113

115 115

117 117

119 119

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

32

32

34

34

36

36

38

38

40

40

42

42

44

44

46

46

48

48

50

50

52

52

54

54

56

56

58

58

60

60

62

62

64

64

66

66

68

68

70

70

72

72

74

74

76

76

78

78

80

80

82

82

84

84

86

86

88

88

90

90

92

92

94

94

96

96

98

98

100

100

102

102

104

104

106

106

108

108

110

110

112

112

114

114

116

116

118

118

120

120

121 121

122

122

123 123

124

124

125 125

127 127

129 129

131 131

133 133

135 135

137 137

139 139

126

126

128

128

130

130

132

132

134

134

136

136

138

138

140

140

C48 0.1U_0402_16V4Z

2@ 1 2

C39 0.1U_0402_16V4Z

2@ 1 2

C76 0.1U_0402_16V4Z

2@ 1 2

R355

100K_0402_5%

1@

G

D

S

Q25

2N7002_SOT23

1@

2

1 3

C61 0.1U_0402_16V4Z

2@ 1 2

C310

0.047U_0402_16V4Z

1

2

G

D

S

Q22

2N7002_SOT23

1@

2

1

3

C82 0.1U_0402_16V4Z

2@ 1 2

C56 0.1U_0402_16V4Z

2@ 1 2

C311

0.047U_0402_16V4Z

1

2

C307

0.1U_0603_50V4Z

2@

1

2

C314

0.1U_0603_50V4Z

2@

1

2

C318

0.1U_0402_16V4Z

1@

1

2

C27

0.1U_0603_50V4Z C23

0.1U_0603_50V4Z

1@

C323

0.1U_0402_16V4Z

1@

R722

KC FBM-L11-201209-221LMAT_0805

1@

1 2

R4

0_0402_5%

1@

1 2

JLVDS1

ACES_88328-4000

1@

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

GND 41

GND

42