Compiler Driven Simulation vs Event Driven Simulation

•

0 likes•700 views

Report

Share

Report

Share

Download to read offline

Recommended

FPGA Implementation of CORDIC Algorithm Architecture

FPGA Implementation of CORDIC Algorithm ArchitectureInternational Journal of Engineering Inventions www.ijeijournal.com

More Related Content

What's hot

FPGA Implementation of CORDIC Algorithm Architecture

FPGA Implementation of CORDIC Algorithm ArchitectureInternational Journal of Engineering Inventions www.ijeijournal.com

What's hot (20)

FPGA Implementation of CORDIC Algorithm Architecture

FPGA Implementation of CORDIC Algorithm Architecture

Performance Study of RS (255, 239) and RS (255.233) Used Respectively in DVB-...

Performance Study of RS (255, 239) and RS (255.233) Used Respectively in DVB-...

A10 microprocessor & microcontrollers ( eee, ece & ecm )

A10 microprocessor & microcontrollers ( eee, ece & ecm )

Evolution of Structure of Some Binary Group-Based N-Bit Compartor, N-To-2N De...

Evolution of Structure of Some Binary Group-Based N-Bit Compartor, N-To-2N De...

More from SRI TECHNOLOGICAL SOLUTIONS

More from SRI TECHNOLOGICAL SOLUTIONS (20)

Request for-new-pan-card-or-and-changes-or-correction-in-pan-data-form

Request for-new-pan-card-or-and-changes-or-correction-in-pan-data-form

Compiler Driven Simulation vs Event Driven Simulation

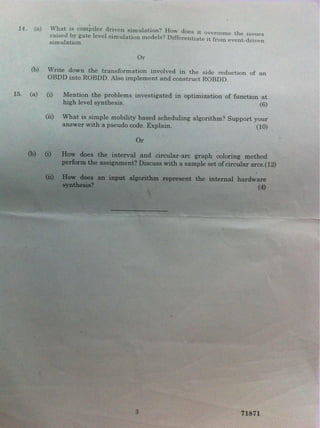

- 1. 14.. (a) What; is compiler driven simulation? How does it overcome the issues raised by gate level simulation models? Differentiate it from everit-drrven simulation. Or . (b) Vrite down the transformation involved in the side reduction of an OBDD into ROBDD. Also implement and construct ROBDD. 15. (a) (i) Mention the problems investigated in optimization of function at high level synthesis. (6) (ii) What is simple mobility based scheduling algorithm? Support your answer with a pseudo code. Explain. (10) Or (h) (i) How does the interval and circular-arc graph coloring method perform the assignment? Discuss with a sample set of circular arcs.(12) (ii) How does an input algorithm represent the internal hardware synthesis? (4) 3 71871