ARSE 1

- 1. ARSE – The Akya Reconfigurable Scheduled Engine

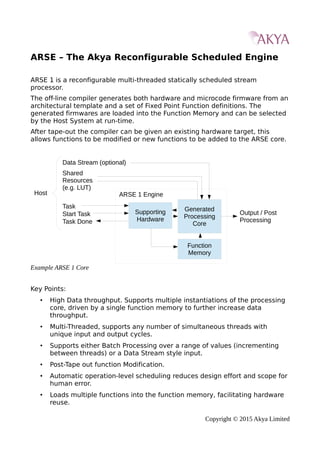

ARSE 1 is a reconfigurable multi-threaded statically scheduled stream

processor.

The off-line compiler generates both hardware and microcode firmware from an

architectural template and a set of Fixed Point Function definitions. The

generated firmwares are loaded into the Function Memory and can be selected

by the Host System at run-time.

After tape-out the compiler can be given an existing hardware target, this

allows functions to be modified or new functions to be added to the ARSE core.

Example ARSE 1 Core

Key Points:

• High Data throughput. Supports multiple instantiations of the processing

core, driven by a single function memory to further increase data

throughput.

• Multi-Threaded, supports any number of simultaneous threads with

unique input and output cycles.

• Supports either Batch Processing over a range of values (incrementing

between threads) or a Data Stream style input.

• Post-Tape out function Modification.

• Automatic operation-level scheduling reduces design effort and scope for

human error.

• Loads multiple functions into the function memory, facilitating hardware

reuse.

Copyright © 2015 Akya Limited

Generated

Processing

Core

Supporting

Hardware

Function

Memory

Output / Post

Processing

Shared

Resources

(e.g. LUT)

Task

Start Task

Task Done

ARSE 1 EngineHost

Data Stream (optional)