⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 2, 2do Parcial (2021PAO2) C6

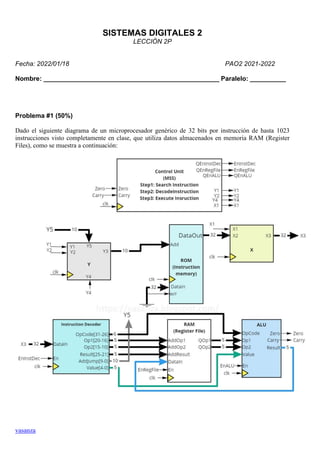

- 1. vasanza SISTEMAS DIGITALES 2 LECCIÓN 2P Fecha: 2022/01/18 PAO2 2021-2022 Nombre: _________________________________________________ Paralelo: __________ Problema #1 (50%) Dado el siguiente diagrama de un microprocesador genérico de 32 bits por instrucción de hasta 1023 instrucciones visto completamente en clase, que utiliza datos almacenados en memoria RAM (Register Files), como se muestra a continuación:

- 2. vasanza El set de instrucciones es la siguiente (OpCode): Las operaciones que puede realizar la ALU son las siguientes: Referencia: https://byterazor.federationhq.de/ Se ide: • Indicar el funcionamiento que realizan los bloques X & Y. Indicar los nombres de cada una de sus señales, así como una descripción detallada del propósito de cada una de ellas (20%). • Colocar las instrucciones en binario que debería tener la memoria ROM, para que el microprocesador sume todos los números de su matrícula de ESPOL (30%).

- 3. vasanza Respuesta: A continuación, se presenta el resumen de las instrucciones y su respectivo Opcode: Instruction Opcode ALU Operation shl 0b000001 Shift_left(RAM(AddOP1)) => RAM(AddResult) shr 0b000010 Shift_right(RAM(AddOP1)) => RAM(AddResult) sto 0b000011 RAM(AddOP1) => RAM(AddResult) li 0b000110 Value => RAM(AddResult) add 0b000111 RAM(AddOP1) + RAM(AddOP2) => RAM(AddResult) sub 0b001000 RAM(AddOP1) – RAM(AddOP2) => RAM(AddResult) addc 0b001001 RAM(AddOP1) + RAM(AddOP2) + 1 => RAM(AddResult) subc 0b001010 RAM(AddOP1) – RAM(AddOP2) - 1 => RAM(AddResult) opand 0b001011 RAM(AddOP1) and RAM(AddOP2) => RAM(AddResult) opor 0b001100 RAM(AddOP1) or RAM(AddOP2) => RAM(AddResult) opxor 0b001101 RAM(AddOP1) xor RAM(AddOP2) => RAM(AddResult) opnot 0b001110 not(RAM(AddOP1)) => RAM(AddResult) jpz 0b001111 if (Zero == 1) then ROM(AddJump) jp 0b010000 ROM(AddJump)

- 4. vasanza Las instrucciones para una cedula de 10 (0-1-2-3-4-5-6-7-8-9) dígitos es la siguiente: ROM (Instruction Memory) Pseudocodigo Instruction Addres OpCode Op1 Op2 Result Address/Value var[1]=0; li 0x000 0b000110 0b00000 0b00000 0b00001 0b0000000000 var[2]=1; 0x001 0b000110 0b00000 0b00000 0b00010 0b0000000001 var[3]=2; 0x002 0b000110 0b00000 0b00000 0b00011 0b0000000010 var[4]=3; 0x003 0b000110 0b00000 0b00000 0b00100 0b0000000011 var[5]=4; 0x004 0b000110 0b00000 0b00000 0b00101 0b0000000100 var[6]=5; 0x005 0b000110 0b00000 0b00000 0b00110 0b0000000101 var[7]=6; 0x006 0b000110 0b00000 0b00000 0b00111 0b0000000110 var[8]=7; 0x007 0b000110 0b00000 0b00000 0b01000 0b0000000111 var[9]=8; 0x008 0b000110 0b00000 0b00000 0b01001 0b0000001000 var[10]=9; 0x009 0b000110 0b00000 0b00000 0b01010 0b0000001001 inc=1; 0x00A 0b000110 0b00000 0b00000 0b01011 0b0000000001 sum=0; 0x00B 0b000110 0b00000 0b00000 0b01100 0b0000000000 i=9; 0x00C 0b000110 0b00000 0b00000 0b01101 0b0000001001 sum=sum+var[i]; add 0X00D 0b000111 0b01100 0b01101 0b01100 0b0000000000 i=i-inc; sub 0X00E 0b001000 0b01101 0b01011 0b01101 0b0000000000 if i==0 jump jpz 0X00F 0b001111 0b00000 0b00000 0b00000 0b0000010001 goto jp 0X010 0b010000 0b00000 0b00000 0b00000 0b0000001101 end - 0X011- 0x3FF 0b010000 0b00000 0b00000 0b00000 0b0000000000 Problema #2: (10%) ¿Cuáles de las siguientes afirmaciones referentes a las memorias de Instrucciones de un microprocesador son ciertas? a) Modificable en tiempo de ejecución b) Modificable en tiempo de compilación c) La única forma de acceder a los datos almacenados es usando punteros d) Se puede especificar las direcciones de almacenamiento Problema #3: (10%) ¿Cuáles de las siguientes afirmaciones referentes a las memorias EEPROM son ciertas? a) No presenta volatilidad de datos al apagar el microcontrolador b) Es modificable en tiempo de compilación c) No posee ciclos de lectura y escritura limitados d) Para usar los datos almacenados, primero se requiere copiarlos en memoria SRAM e) Direcciones de memoria no usadas están cargadas con 0x00 por default Problema #4: (10%) ¿Cuáles de las siguientes afirmaciones referentes a las memorias de datos (Register File) son ciertas? a) Memoria preferiblemente usada para almacenar grandes textos y datos no modificables b) Memoria preferiblemente usada para almacenar datos de configuración no volátiles c) Direcciones de memoria no usadas están cargadas con 0xFF por default d) Volatilidad de datos al apagar el microcontrolador e) Modificable en tiempo de ejecución

- 5. vasanza Problema #5: (20%) Shen et Al., escribió el paper titulado “An FPGA-based Distributed Computing System with Power and Thermal Management Capabilities” en donde desarrolla una plataforma computacional distribuida compuesta de múltiples FPGAs conectadas via Ethernet y cada FPGA está configurada como un sistema multi-core. Los núcleos en el mismo FPGA se comunican a través de la memoria compartida, mientras que diferentes FPGA se comunican a través de enlaces Ethernet, como se muestra en la siguiente gráfica: Fig. Arquitectura del sistema distribuido Las FPGAs están en las tarjetas de desarrollo Altera Nios II Embedded Evaluation Kit (NEEK), la edición de Altera NEEK Cyclone III tiene un Cyclone III EP3C25F324 FPGA con 25,000 elementos lógicos y 594 Kbits Memoria incorporada, 32 MB DDR SDRAM, 1 MB SRAM, 16 MB Flash Intel P30 / P33, pantalla táctil de 800 X 480, Ethernet 10/100 Mbps, y conector PS2 y RS-232. Desarrollar el diagrama de bloques basado en el NIOSii processor que considere debió utilizar Shen et Al. en cada una de las FPGA, basado en las siguientes especificaciones: • El JTAG UART proporciona la interfaz de puerto de depuración. • Se incluye un temporizador de alta resolución para medir el tiempo de ejecución del programa. • La E / S paralela (PIO) proporciona control y monitoreo al reloj. • Una o varias memorias compartidas están conectadas a cada subsistema Nios II. Estas memorias compartidas se configuran como Mailbox de hardware para las comunicaciones entre los procesadores en el mismo FPGA. • Entre todos los subsistemas Nios II en el mismo FPGA, hay uno que tiene un módulo de interfaz Ethernet. • El módulo de interfaz Ethernet consta de un controlador Direct Memory Access (DMA), una memoria de descriptor y el MAC de Ethernet. • El subsistema Nios II que tiene la interfaz Ethernet que actúa como una puerta de enlace para las comunicaciones entre FPGA en el sistema informático distribuido. • Todos los periféricos están conectados al procesador Nios II a través de la interfaz mapeada en memoria de Avalon. • La interfaz de transmisión de Avalon se utiliza para conectar el DMA al controlador Ethernet. Referencia: Shen, H., & Qiu, Q. (2011, July). An FPGA-based distributed computing system with power and thermal management capabilities. In 2011 Proceedings of 20th International Conference on Computer Communications and Networks (ICCCN) (pp. 1-6). IEEE.

- 6. vasanza Se pide: a) Proponer la realización del sistema descrito, pero ahora con un el microprocesador genérico de la pregunta 1 (10%). Respuesta: b) Indicar cuál de las siguientes gráficas corresponde al Diseño SoPC en las FPGAs propuesto por los autores (10%): A B