IBM CAPI:概要 (An overview of IBM CAPI)

- 3. Overview

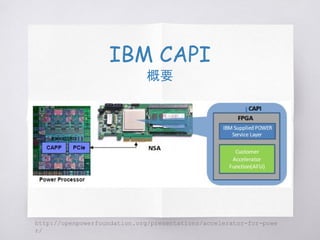

- 4. http://www.nallatech.com/wp-content/uploads/IBM_CAPI_Users_Guide_1-2.pdf 一見すると、 CPUとFPGAだがFPGAの中に ある PSL と POWER8の中にある CAPP が重要 IBM CAPIとは Coherent Accelerator Processor Interface

- 5. The Coherent Accelerator Processor Interface (CAPI) is a general term for the infrastructure of attaching a coherent accelerator to an IBM POWER® system. The main application is executed on the host processor with computation-heavy functions executing on the accelerator. The accelerator is a full peer to the host processor, with direct communication with the application. The accelerator uses an unmodified effective address with full access to the real address space. It uses the processor’s page tables directly with page faults handled by system software. Coherent Accelerator Processor Interface

- 6. http://www.nallatech.com/wp-content/uploads/IBM_CAPI_Users_Guide_1-2.pdf POWER8(CPU)は、 MMUで 仮想アドレス => 物理アドレス にしてメモリにアクセス POWER8とAcceleratorのメモリ共有 Acceleratorは、 PSL/PCIe/CAPPで 仮想アドレス => 物理アドレス にしてメモリにアクセス

- 7. http://openpowerfoundation.org/wp-content/uploads/2015/03/Finamore-Nick_OP FS2015_Altera_031215_final.pdf Host Memory & Device Memory Altera SDK for OpenCL

- 8. http://openpowerfoundation.org/wp-content/uploads/2015/03/Finamore-Nick_OP FS2015_Altera_031215_final.pdf Coherent Memory Xeon - QPI − FPGA CCI-extended

- 10. Hardware

- 11. AFU POWER8とFPGAの関係 CAPP PCIe FPGA PHB : PCIe Host Bridge CAPP : Coherently Attached Processor Proxy PSL : Power Service Layer AFU : Accelerator Function Unit PHB CPU POWER8 PSL

- 12. AFU PSL : POWER Service Layer CAPP PCIe FPGA PSLは、IBMが開発 CAPI対応FPGAボードベンダから提 供される (IBMから供給) PHB CPU POWER8 PSL

- 13. PSL : POWER Service Layer The PSL provides the translation and interrupt services that the AFU needs. This is what the kernel interacts with. For example, if the AFU needs to read a particular effective address, it sends that address to the PSL, the PSL then translates it, fetches the data from memory and returns it to the AFU. If the PSL has a translation miss, it interrupts the kernel and the kernel services the fault. The context to which this fault is serviced is based on who owns that acceleration function. https://git.kernel.org/cgit/linux/kernel/git/torvalds/linux.git/pl ain/Documentation/powerpc/cxl.txt

- 14. AFU AFU : Accelerator Function Unit CAPP PCIe FPGA AFUは、ユーザが開発 HDL(Verilog HDL/VHDL)でなく、 HLSなどを使ってC/C++でも可能 PHB CPU POWER8 PSL

- 15. Software

- 16. AFU libcx PCIe FPGA Applicationは、 libcxl (ユーザ空間) API => Linux CXLデバイスドライバ経由で FPGAのAFUにアクセスする FPGA(AFU)独自の デバイスドライバは不要 PSL CXL Application POWER8 libcxl

- 17. Coherent Accelerator Interface https://github.com/ibm-capi/libcxl CXL : linux device driver https://git.kernel.org/cgit/linux/kernel/git/ torvalds/linux.git/plain/Documentation/powe rpc/cxl.txt

- 18. libcxl API open : デバイスのオープン ioctl : CXL_IOCTL_START_WORK CXL_IOCTL_GET_PROCESS_ELEMENT mmap : mmio空間へのアクセス read : AFUからのイベントを読み込む

- 19. AFU Application PCIe FPGA Applicationは、 libcxl (ユーザ空間) API => Linux CXLデバイスドライバ経由で FPGAのAFUにアクセスする FPGA(AFU)独自の デバイスドライバは不要 PSL CXL Application POWER8 libcxl

- 20. Applicationのテンプレートコード // AFUの確認 struct cxl_afu_h *afu_h = cxl_afu_next(NULL); // AFUを獲得 afu_h = cxl_afu_open_h(afu_h,CXL_VIEW_DEDICATED); // AFUの起動 cxl_afu_attach(afu_h, (uint64_t) wed); // 必要ならMMIOをマップ cxl_mmio_map(afu_h, CXL_MMIO_BIG_ENDIAN); // ここで何かをやる cxl_mmio_unmap(afu_h); // MMIOをアンマップ cxl_afu_free(afu_h); // AFUを開放