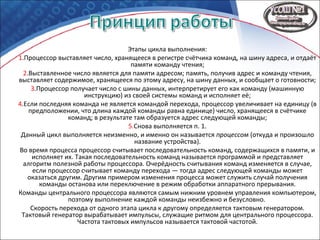

Документ описывает центральный процессор (ЦП), его архитектуру, функциональные устройства и циклы обработки данных. Он также рассматривает эволюцию процессоров от их создания до современных многоядерных архитектур и описывает тенденции их роста производительности. В заключение упоминаются будущее технологий, такие как квантовые и молекулярные компьютеры, которые могут изменить подход к вычислениям.