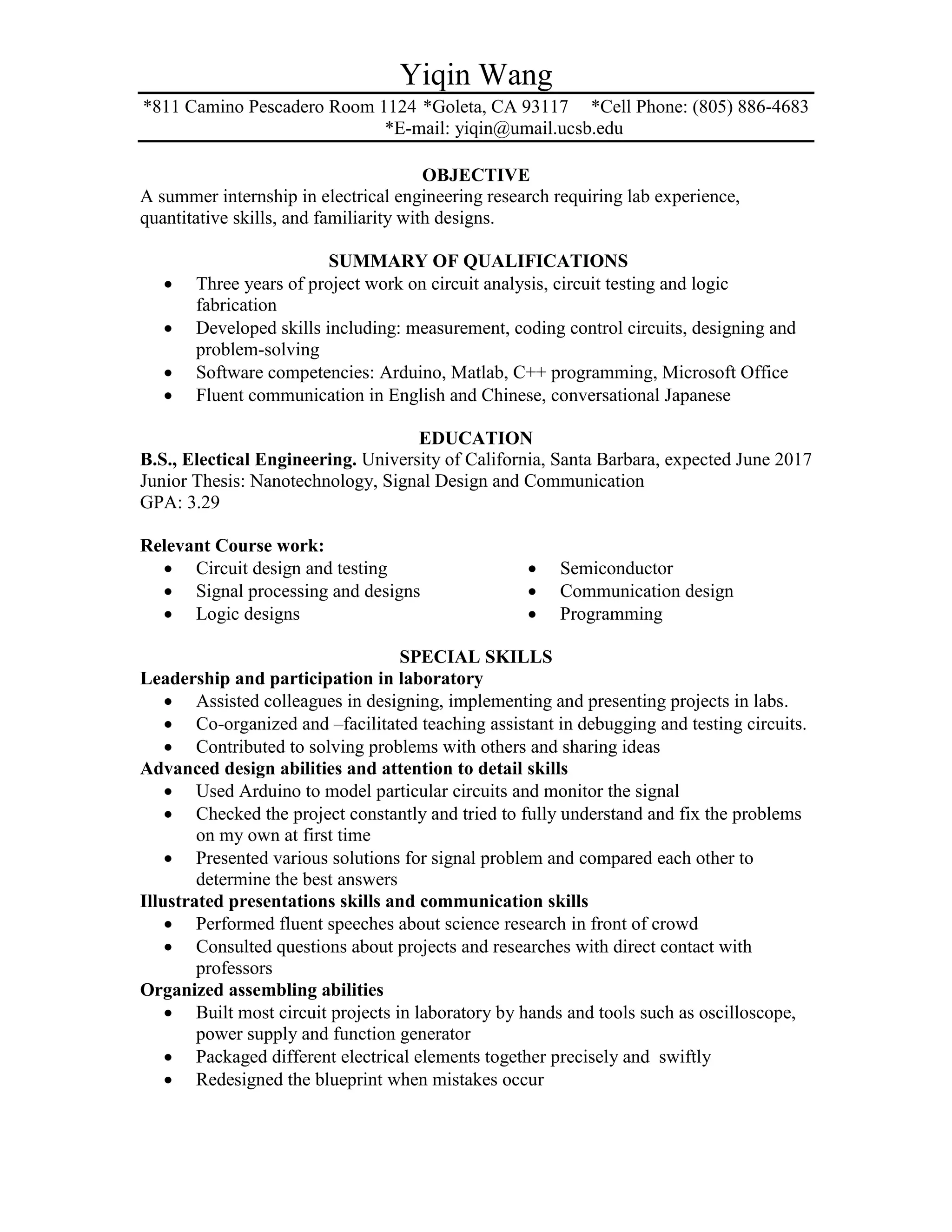

This resume is for Yiqin Wang, a student seeking a summer internship in electrical engineering. Wang has three years of experience with circuit analysis, testing, and logic fabrication projects. She is proficient in Arduino, Matlab, C++, and Microsoft Office. Wang is pursuing a B.S. in Electrical Engineering from UC Santa Barbara with a 3.29 GPA and a focus on nanotechnology, signal design, and communication. She has skills in circuit design, programming, leadership, and presentation.