Embed presentation

Download to read offline

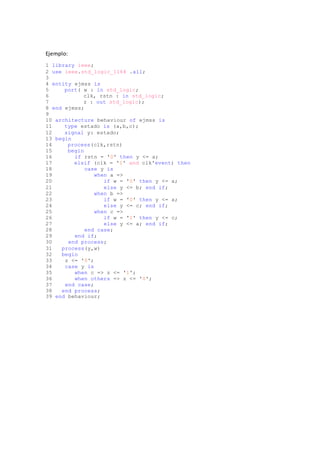

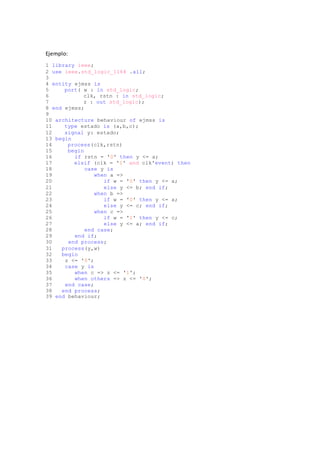

This document describes a VHDL code for a simple finite state machine with 3 states (a, b, c) that is triggered by a clock signal and reset. The state transitions depend on the current state and the value of an input signal w. An output signal z is assigned the value 1 when the state is c, and 0 for all other states.