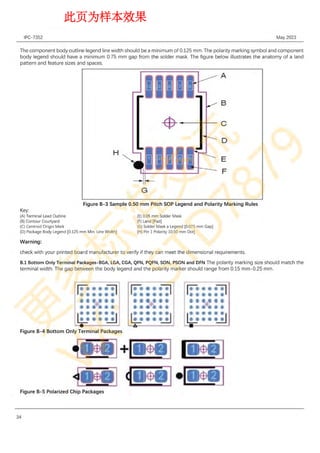

The document IPC-7352 serves as a guideline for land pattern design within the electronics industry, outlining essential standards developed by IPC. It aims to enhance product quality, facilitate manufacturer-purchaser interactions, and encourage voluntary adherence to these standards. Additionally, it highlights IPC's commitment to continuous improvement and invites community participation in standard development.