flip flops.pptx

•Download as PPTX, PDF•

0 likes•15 views

Flip-flop working on computers

Report

Share

Report

Share

Recommended

More Related Content

Similar to flip flops.pptx

Similar to flip flops.pptx (20)

Recently uploaded

Recently uploaded (20)

Tata AIG General Insurance Company - Insurer Innovation Award 2024

Tata AIG General Insurance Company - Insurer Innovation Award 2024

08448380779 Call Girls In Friends Colony Women Seeking Men

08448380779 Call Girls In Friends Colony Women Seeking Men

TrustArc Webinar - Stay Ahead of US State Data Privacy Law Developments

TrustArc Webinar - Stay Ahead of US State Data Privacy Law Developments

Boost Fertility New Invention Ups Success Rates.pdf

Boost Fertility New Invention Ups Success Rates.pdf

The Codex of Business Writing Software for Real-World Solutions 2.pptx

The Codex of Business Writing Software for Real-World Solutions 2.pptx

From Event to Action: Accelerate Your Decision Making with Real-Time Automation

From Event to Action: Accelerate Your Decision Making with Real-Time Automation

Automating Google Workspace (GWS) & more with Apps Script

Automating Google Workspace (GWS) & more with Apps Script

Strategies for Unlocking Knowledge Management in Microsoft 365 in the Copilot...

Strategies for Unlocking Knowledge Management in Microsoft 365 in the Copilot...

2024: Domino Containers - The Next Step. News from the Domino Container commu...

2024: Domino Containers - The Next Step. News from the Domino Container commu...

Boost PC performance: How more available memory can improve productivity

Boost PC performance: How more available memory can improve productivity

Raspberry Pi 5: Challenges and Solutions in Bringing up an OpenGL/Vulkan Driv...

Raspberry Pi 5: Challenges and Solutions in Bringing up an OpenGL/Vulkan Driv...

Apidays Singapore 2024 - Building Digital Trust in a Digital Economy by Veron...

Apidays Singapore 2024 - Building Digital Trust in a Digital Economy by Veron...

Axa Assurance Maroc - Insurer Innovation Award 2024

Axa Assurance Maroc - Insurer Innovation Award 2024

flip flops.pptx

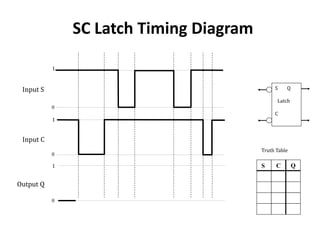

- 1. SC Latch Timing Diagram S C Q Truth Table S Q Latch C 1 0 1 0 1 0 Input S Input C Output Q

- 2. JK Flipflop Operation J CLK K S Q C Vcc Vcc Q PRE CLR J K CLK Q 0 0 X X X ? 0 1 X X X 1 1 0 X X X 0 1 1 X X — Q 1 1 X X Q 1 1 0 0 Q 1 1 0 1 0 1 1 1 0 1 1 1 1 1 Q

- 3. JK Flipflop Timing Diagram J CLK K S Q C Vcc Vcc Q 1 0 1 0 1 0 Time Input J Input K Output Q 1 0 Input CLK

- 6. D Flip Flop

- 7. Latch & Flip Flop Summary Latches Flip-Flops Asynchronous inputs are level sensitive (active-high or active-low) Synchronous Control inputs and an edge-triggering CLK (rising or falling edge triggered) SC Latch (AKA RS Latch): SET and CLEAR inputs. Could think of those as direct and inverting inputs. Has an unstable input combination. SC Flip-Flop: SET and CLEAR queries at CLK edge. Has an unstable input combination. Rare. (No corresponding latch. Can’t toggle without a CLK.) JK Flip-Flop: Like SC-FF, but unstable input replaced by toggle mode. D Latch: Make D-FF level sensitive. This has “transparent” and “hold” modes. D Flip-Flop: Remove toggle and “inverting” inputs of JK-FF. Output copies input at CLK trigger.

- 8. Clock Signal Details tw T 1 sec ↳ f = 3 Hz

- 9. Making an Edge ‘Detector’ CLK CLK* CLK CLK* CLK CLK

- 10. Building a SC Flip Flop Edge Detector S CLK C SET CLEAR Q Q CLK*

- 11. Building a JK Flip Flop J CLK CLK* K Edge Detector SET CLEAR Q Q

- 12. Adding Preset & Clear J CLK CLK* K Edge Detector Set Q Q Clear PRESET CLEAR