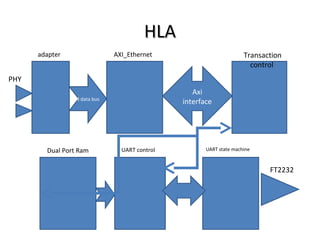

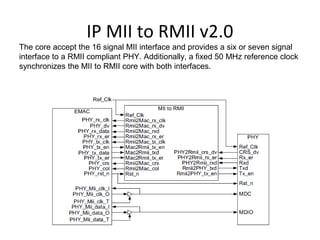

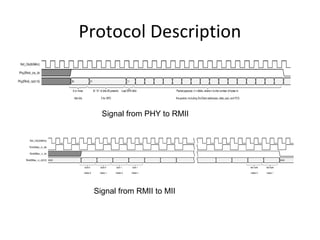

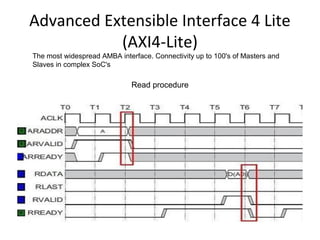

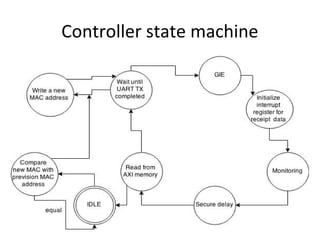

This document describes an Ethernet sniffer project implemented on an FPGA board without software. The sniffer is able to monitor its own subnet and output messages containing the destination and source MAC addresses, length, and data when it detects an Ethernet broadcast message from another device. It uses a dual port RAM, AXI interface, and state machines to transfer data between the PHY, MII to RMII core, Ethernet MAC, and UART for output.