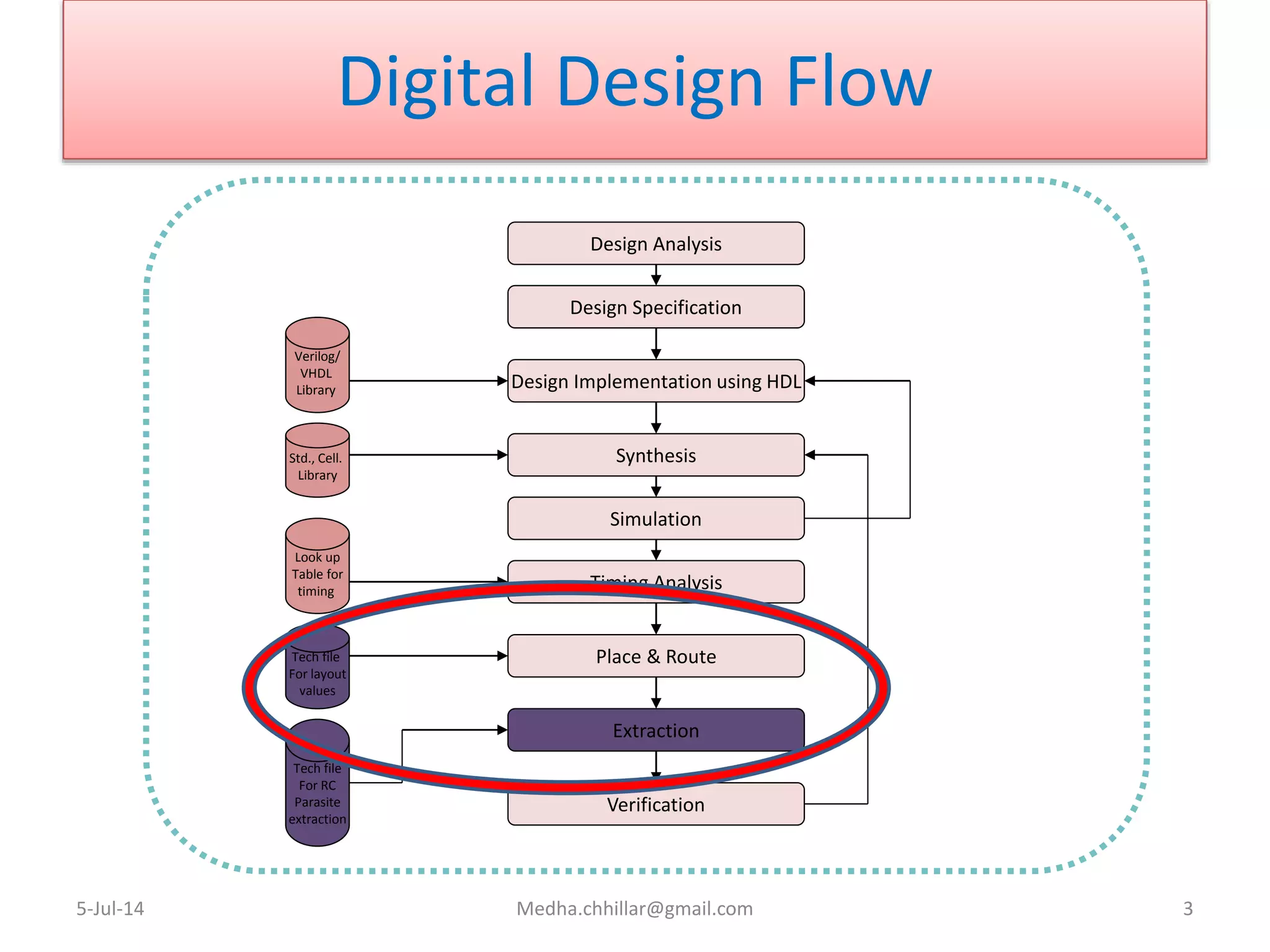

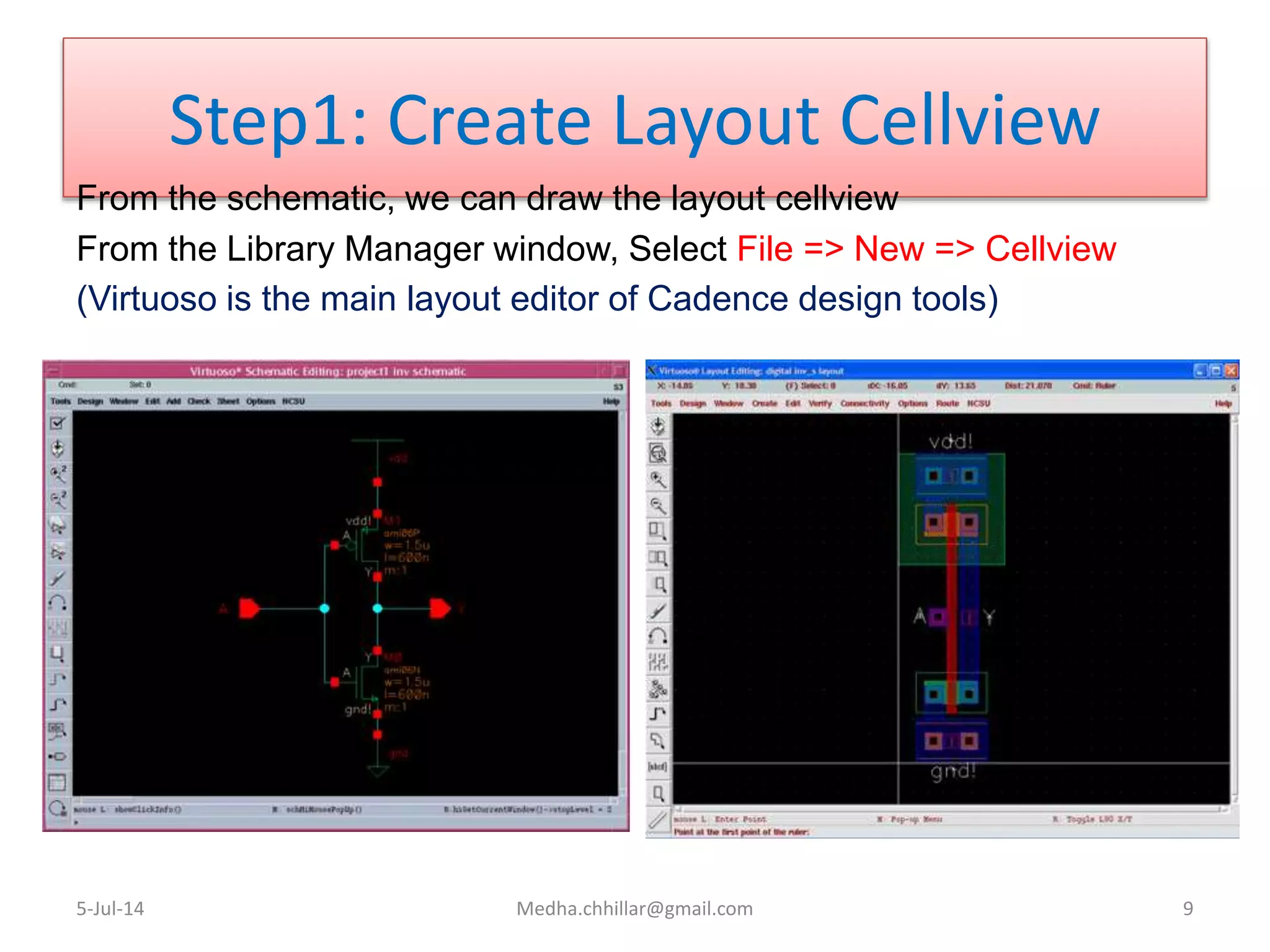

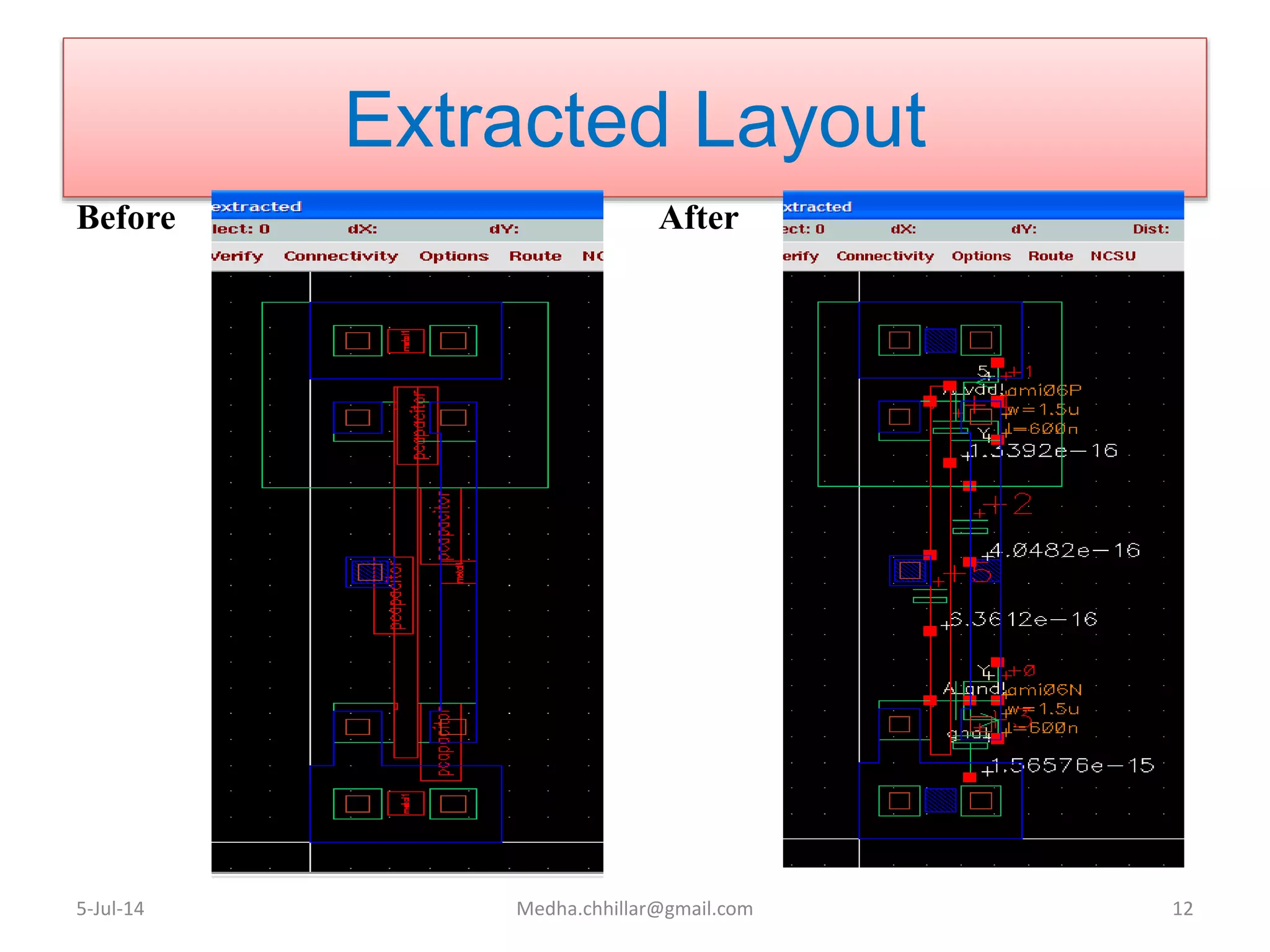

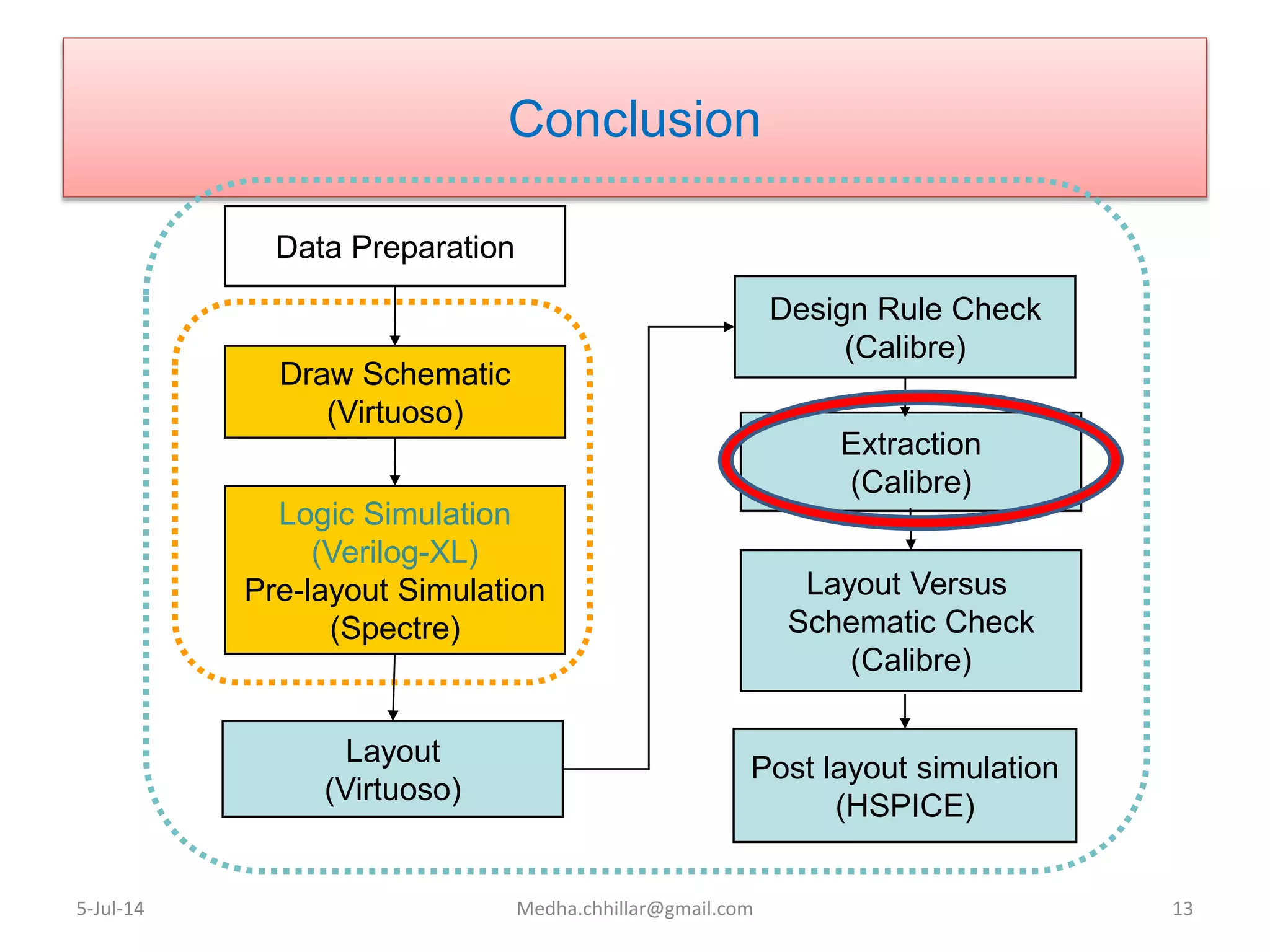

This document discusses layout extraction which involves identifying parasitic capacitances and resistances introduced during chip layout. It outlines the digital design flow involving synthesis, simulation, place and route, and extraction. The basics of standard cell layout are described along with commonly used extraction tools like FastCap and Star-RCXT. The key steps of layout extraction are creating a layout cellview, design rule checking, layout parameter extraction, and comparing the layout to the schematic.