More Related Content

PPTX

PPTX

PPTX

PPTX

PPTX

PPTX

PPTX

PPTX

What's hot

PPTX

PSpiceを活用したハーフブリッジ回路シミュレーションの事例 PDF

PPTX

PPTX

PPTX

PPTX

バリスタの簡易等価回路モデリングとシミュレーション PDF

Monte Carlo Methods (Chapter 17 in Deep learning by Ian Goodfellow) PPTX

LTspiceを活用した12AX7の基本特性のシミュレーション PPTX

LTspiceを活用した12AX7の基本特性のシミュレーション PDF

パートナーと共創する さくらのクラウドのサービス展開 PDF

Sliced Wasserstein Distance for Learning Gaussian Mixture Models PPTX

PPTX

PDF

Ống ruột gà lõi thép inox - Nippon Seam (Japan) DOCX

More from Tsuyoshi Horigome

PPTX

FedExで書類を送付する場合の設定について(オンライン受付にて登録する場合について) PPTX

SPICE PARK JUN2024 ( 6,826 SPICE Models ) PPTX

SPICE PARK JUL2024 ( 6,866 SPICE Models ) PPTX

Update 40 models( Solar Cell ) in SPICE PARK(JUL2024) PDF

Marketing and Sales Relationship Diagram PDF

Safety Lock Circuits (LTspice + Explanation) PDF

TI TPS544x25 (TPS544B25/C25) - Block Diagram PPTX

STHV64SW(STマイクロエレクトロニクス)のデータシートの要約について(Suitable for ultrasound imaging applic... PPTX

Setting KPI of Estimation Department Division PPTX

H8500-based Scintillation Detection System (Block Diagram) by Bee Technologies PPTX

SPICEモデルとは? (SPICEモデルの種類と用途別の選定方法についての要約) PPTX

回路ブロック図の事例(PMBus 対応、周波数同期機能搭載、4.5V ~ 18V、20A 同期整流 SWIFT™ 降圧コンバータ) PPTX

高周波回路のノイズ抑制について回路設計、基板設計、基板製造における対策方法について PDF

Wio LTE JP Version v1.3b- 4G, Cat.1, Espruino Compatible\202001935, PCBA;Wio ... PPTX

sub-GHz帯域(315MHzや920MHz)で使用する際のポイントについてのご説明 PPT

Package Design Design Kit 20100009 PWM IC by Bee Technologies PPTX

KGIとKPIについて(営業の目標設定とKPIの商談プロセス) About KGI and KPI PDF

High-frequency high-voltage transformer outline drawing PPTX

Update 33 models(General Diode ) in SPICE PARK(JUN2024) DOCX

Basic Flow Chart Shapes(Reference Memo)for word version Recently uploaded

PDF

krsk_aws_re-growth_aws_devops_agent_20251211 PPTX

君をむしばむこの力で_最終発表-1-Monthon2025最終発表用資料-.pptx PDF

ソフトとハードの二刀流で実現する先進安全・自動運転のアルゴリズム開発【DENSO Tech Night 第二夜】 ー高精度な画像解析 / AI推論モデル ... PDF

音楽アーティスト探索体験に特化した音楽ディスカバリーWebサービス「DigLoop」|Created byヨハク技研 PDF

ソフトウェアエンジニアがクルマのコアを創る!? モビリティの価値を最大化するソフトウェア開発の最前線【DENSO Tech Night 第一夜】 PDF

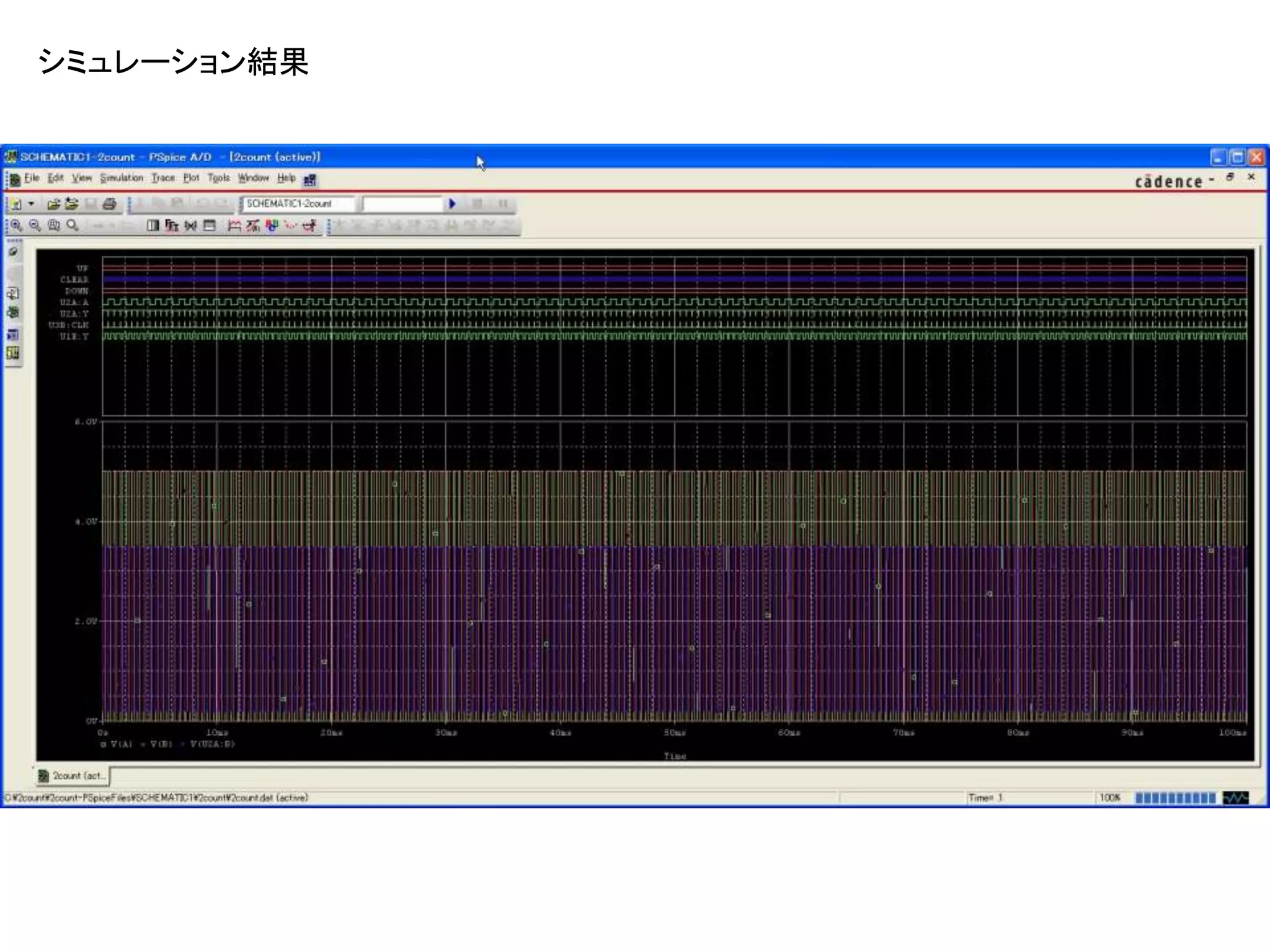

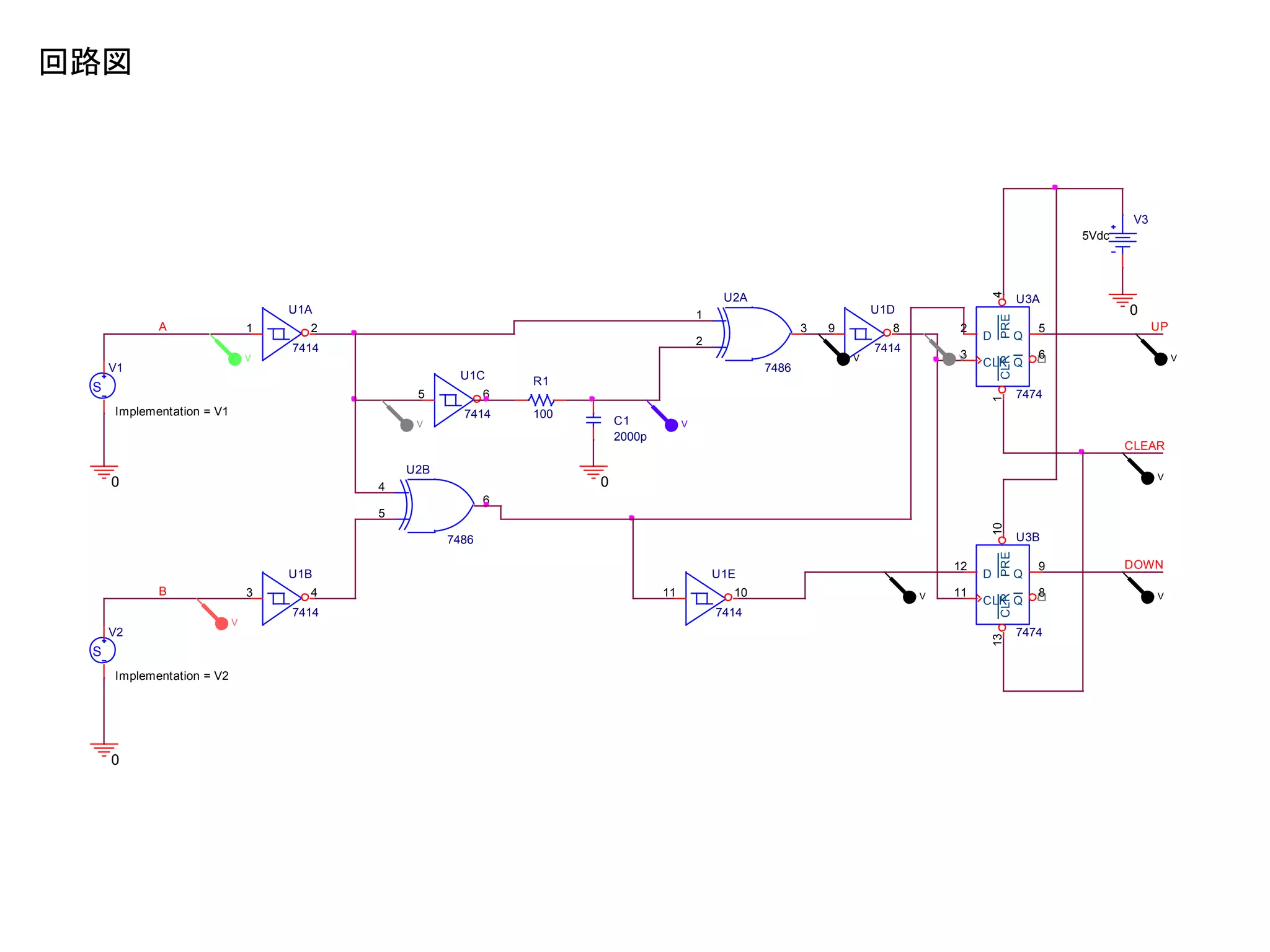

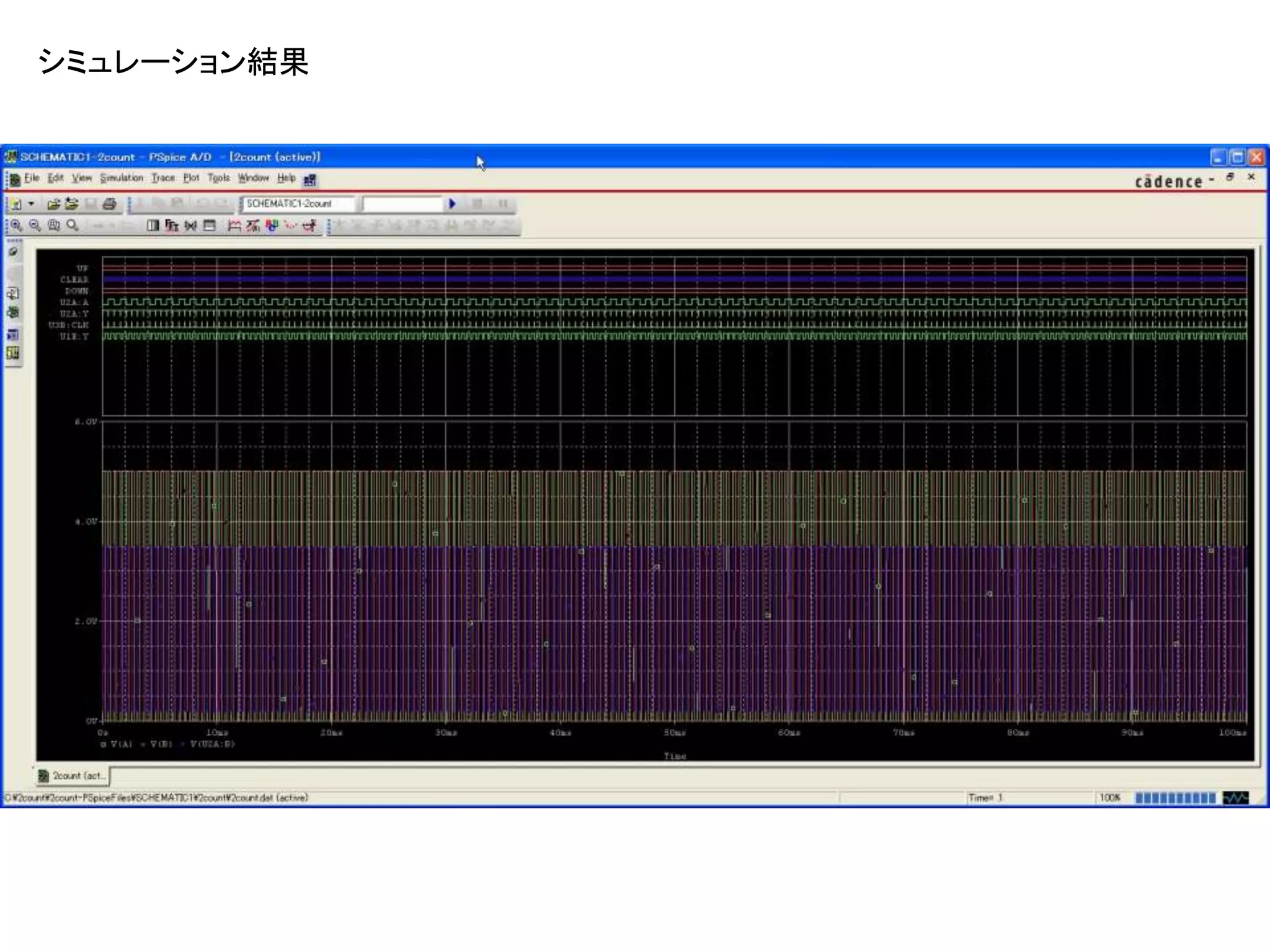

2025/12/12 AutoDevNinjaピッチ資料 - 大人な男のAuto Dev環境 2カウントシミュレーション

- 1.

- 2.

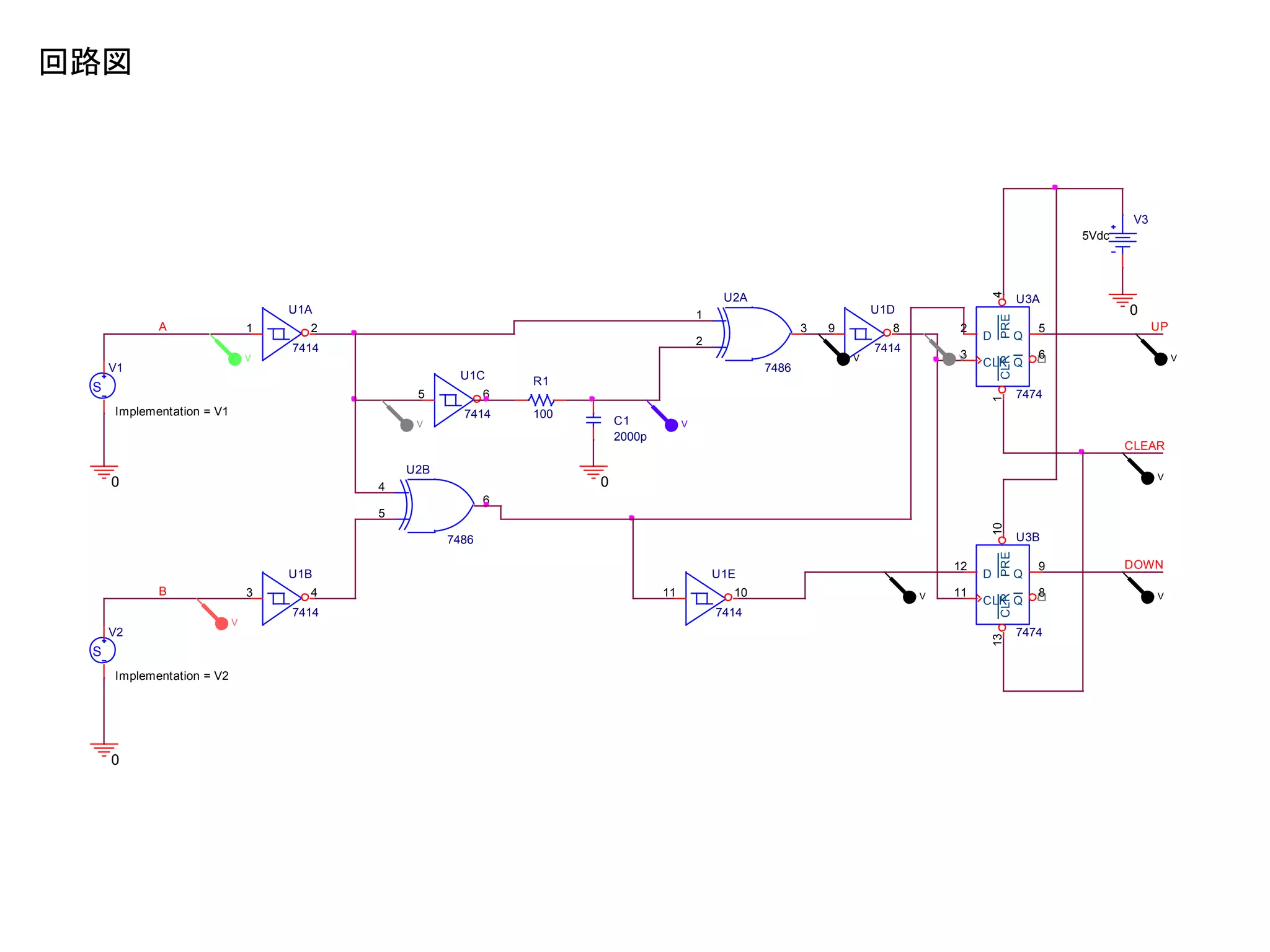

U1A

7414

1 2

U1B

7414

3 4

U1C

7414

56

U1D

7414

9 8

U1E

7414

11 10

U2A

7486

1

2

3

U2B

7486

4

5

6

U3A

7474

CLK

3

CLR

1

D

2

PRE

4

Q

5

Q

6

U3B

7474

CLK

11

CLR

13

D

12

PRE

10

Q

9

Q

8

R1

100

C1

2000p

0

UP

DOWN

CLEAR

A

B

S

V1

Implementation = V1

S

V2

Implementation = V2

0

0

V3

5Vdc

0

V

V

V

V

VV

VV

V

V

回路図

- 3.