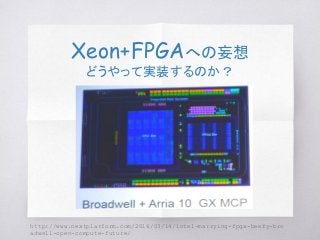

「Xeon+FPGA への妄想」 どうやって実装するのか? ("Delusion to (Xeon + FPGA)" : How to implement?)

- 3. この資料について IDF16の公開資料 ・Enabling Dynamic Usage Models for FPGA with the Accelerator Abstraction Layer Software Technology ・Strategies and Tools to Optimize Modern Workloads を読み込むための参考資料としてご利用ください

- 4. IvyBridge Xeon (E5-26xx v2) + Stratix V FPGA http://www.pactroninc.com/qpi/ Pectron Romley IvyBridge QPI SDP

- 5. Broadwell Xeon (E5-26xx v4) + Arria 10 FPGA http://www.pactroninc.com/qpi/ Pectron Grantley HSX/BSX QPI SDP

- 6. https://cpufpga.wordpress.com/2016/04/15/xeonfpga-tutorial-on-cohere nt-fpga-programming/ Using OpenCL for FPGAs and Preview of Xeon+FPGA architecture

- 7. https://cpufpga.files.wordpress.com/2016/04/harp_isca_2016_final.pdf 2. Hardware Research Prototype – An Overview 10:30 PM – 11:30 PM, Speaker – David Sheffield IvyTown Xeon + FPGA: The HARP Program ● HARP (Xeon + FPGA) Prototype Architecture ● Research overview and insights from HARP ● Future HARP plans

- 8. IvyTown Xeon (E5-26xx v2) + Stratix V Inteの資料から http://reconfigurablecomputing4themasses.net/files/2.2%20PK.pdf

- 11. https://cpufpga.files.wordpress.com/2016/04/harp_isca_2016_final.pdf Altera SDK for OpenCLA++ Compiler for HLS?

- 12. Broadwell + Arrira 10 のことは出てこないので、 Google君に聞いてみた

- 13. Bluespec:MIT & Intelの事例(LEAP) http://blogs.yahoo.co.jp/verification_engineer/66046446.html 2012/2/1(水) 午後 5:10 Bluespec User Meeting 2012にて、Bluespecからのプレゼンテー ションにあったIntelの事例は、LEAP: A Virtual Platform Architecture for FPGAsかもしれません。 途中略 このLEAPは、今ではオープンソースで公開されていま す。なんと、太っ腹。 途中略 自分の過去ログに教えてもらった

- 15. Page not found The page you were trying to access doesn't exist or has been removed. Back ィャ ─ ・゚・(m´□`m)・゚・ ─ ァ!!

- 16. なら、Google君に LEAP MIT Intel FPGA で聞いてみた

- 17. LEAP-FPGA Platform https://github.com/LEAP-FPGA/leap-documentation/wiki Papers: https://github.com/LEAP-FPGA/leap-documentation/wiki/Papers Sources: LEAP-Core : https://github.com/LEAP-Core LEAP-Workloads : https://github.com/LEAP-Workloads GitHubにあったよ

- 19. LEAP Platform Intel https://github.com/LEAP-Core/leap-platforms-intel Xeon+FPGA SDR上に 実装したモジュールのコードを発見! ワク♪((o(⌒∇⌒)o))ワク♪

- 20. 次の3つの環境で実装しているみたい ・ASE(VCS : Synopsys HDL Simulator) ・SDP (Intel Software Development Platform) ・BDX(Intel QuickAssist CCI-P FPGA BDX Xeon+FPGA)

- 21. https://cpufpga.files.wordpress.com/2016/04/harp_isca_2016_final.pdf ASE = Intel AFU simulation environment AFU : Accelerator Function Unit

- 22. post-synthesis-qa-sdp/README the Intel QuickAssist FPGA in Canoe Pass(Intel S2600CP two-socket motherboards) SDP. post-synthesis-qa-sdp/ome2_ivt.qsf set_global_assignment -name FAMILY " Stratix V" set_global_assignment -name DEVICE 5SGXEA7N1F45C1 post-synthesis-qa-bdx/README the Intel QuickAssist FPGA in Broadwell post-synthesis-qa-bdx/bdw_502_pr_afu.qsf set_global_assignment -name FAMILY " Arria 10" set_global_assignment -name DEVICE 10AX115U3F45E2SGE3 Arria 10 GX 1150/1932pin やっと、見つかったよ https://github.com/LEAP-Core/leap-platforms-intel/blob/master/modules/leap/build- support/build-pipelines/stages/altera/post-synthesis-qa-bdx/README

- 24. 次は何を実装するかだ

- 25. Accelerating Datacenter Workloads FPL 2016 PK Gupta, GM of Xeon+FPGA Products Datacenter Group から http://www.fpl2016.org/slides/Gupta/20--/0Accelerating/20Datacenter/ 20Workloads.pdf

- 26. FPGAにはメモリが無いっす!

- 27. End User Programming Interface メモリは無くなったが、HSSIは付いている

- 28. Xeon + FPGA in the Cloud IP Libraryがある