Recommended

PDF

PWNの超入門 大和セキュリティ神戸 2018-03-25

PDF

PDF

PDF

PPTX

PDF

PDF

PDF

PDF

Install FD.IO VPP On Intel(r) Architecture & Test with Trex*

PDF

ARM CPUにおけるSIMDを用いた高速計算入門

PDF

PDF

PDF

SpectreとMeltdown:最近のCPUの深い話

PDF

CUDAのアセンブリ言語基礎のまとめ PTXとSASSの概説

PDF

Yoctoで綺麗なkernel configを作る

PPTX

PostgreSQLクエリ実行の基礎知識 ~Explainを読み解こう~

PDF

PDF

The Linux Block Layer - Built for Fast Storage

PDF

Intro to SVE 富岳のA64FXを触ってみた

PDF

PDF

組み込み関数(intrinsic)によるSIMD入門

PPT

PDF

PDF

PDF

PPTX

LUT-Network ~本物のリアルタイムコンピューティングを目指して~

PPTX

リアルタイムOSの必要性とTOPPERS/SSPの紹介

PDF

PDF

PDF

More Related Content

PDF

PWNの超入門 大和セキュリティ神戸 2018-03-25

PDF

PDF

PDF

PPTX

PDF

PDF

PDF

What's hot

PDF

Install FD.IO VPP On Intel(r) Architecture & Test with Trex*

PDF

ARM CPUにおけるSIMDを用いた高速計算入門

PDF

PDF

PDF

SpectreとMeltdown:最近のCPUの深い話

PDF

CUDAのアセンブリ言語基礎のまとめ PTXとSASSの概説

PDF

Yoctoで綺麗なkernel configを作る

PPTX

PostgreSQLクエリ実行の基礎知識 ~Explainを読み解こう~

PDF

PDF

The Linux Block Layer - Built for Fast Storage

PDF

Intro to SVE 富岳のA64FXを触ってみた

PDF

PDF

組み込み関数(intrinsic)によるSIMD入門

PPT

PDF

PDF

PDF

PPTX

LUT-Network ~本物のリアルタイムコンピューティングを目指して~

PPTX

リアルタイムOSの必要性とTOPPERS/SSPの紹介

PDF

Viewers also liked

PDF

PDF

PDF

Basic of virtual memory of Linux

PDF

Linuxのプロセススケジューラ(Reading the Linux process scheduler)

ODP

PDF

Pacemaker + PostgreSQL レプリケーション構成(PG-REX)のフェイルオーバー高速化

PDF

Linux女子会 - お仕事メリハリ術♪(プロセススケジューラ編)

PDF

PPTX

PDF

X86 hardware for packet processing

KEY

PDF

PPT

PPT

PDF

PDF

PDF

Free Serverというナウでヤングなサービス

PDF

PDF

PDF

Similar to 0章 Linuxカーネルを読む前に最低限知っておくべきこと

PDF

PDF

PDF

PDF

PDF

PDF

PDF

[Basic 7] OS の基本 / 割り込み / システム コール / メモリ管理

PDF

PEZY-SC programming overview

PDF

2011.09.18 v7から始めるunix まとめ

PPTX

x86-64/Linuxに独自メモリ空間を勝手増設

PDF

PDF

PPT

PPT

PDF

PDF

2011.06.11 v7から始めるunix まとめ

PPTX

x86-64/Linuxに独自メモリ空間を勝手増設

PPT

PDF

PDF

0章 Linuxカーネルを読む前に最低限知っておくべきこと 1. 2. 3. Just for Fun

(Just for Fun: The Story of an Accidental Revolutionary より )

純粋な好奇心と楽しさを大切に

はじめに

4. 概要 – 最低限知っておくと

ハッピーになれること

1. カーネル理解の方法

色んな人がカーネルの理解をしようと挑戦している。

色んな方法、とっかかりがある。

2. コンピュータアーキテクチャの概要

各概念やキーワードの位置づけが分かる。

知識を体系的に整理できる。

徐々に覚えていくもの。

3.CPU のこと

レジスタは、メモリ管理・プロセス切り替え等で頻出。

特に x86(i386) や ARM における構造を知っておくと良い。

4. マザーボードの構成

PC の全体像を捉えるのにちょうど良い。

5. 6. カーネル参考文献

< 参考書 >

~基本的に古い情報だが、基本は学べる~

・詳解 LINUX カーネル 第 3 版 (O'REILLY

・ Linux カーネル 2.6 解読室 (Softbank Creative

・ Linux カーネル解析入門 ( 工学社

・ Modern Operating Systems 3e International

(Pearson,Andrew S.Tanenbaum)

~初期化部分を知りたいなら~

・新装改訂版 Linux のブートプロセスを見る

(KADOKAWA/ アスキー・メディアワークス )

< 参考 Web>

・ Linux Cross Reference[http://lxr.free-electrons.com]

最新カーネルのソースコードをブラウザで読める。

7. 8. 1. カーネル理解の方法 (1) - 心構え

1. 【ソース解析】 linux カーネルソースを読む 先人の苦労

- NAVER まとめ

http://matome.naver.jp/odai/2134411943144485801

2.Yakst - Linux カーネルハッカーになる 4 つの方法

https://yakst.com/ja/posts/156

3.Linux カーネルの読み方 - Naoya Ito

http://image.gihyo.co.jp/assets/files/event/2008/24svr/report/2-24svr-

TechMTG-ito.pdf

4. はじめてのカーネルソース

- 第 1 回 どうしたら読めるようになるのか: ITpro

http://itpro.nikkeibp.co.jp/article/COLUMN/20071024/285378/

9. 1. カーネル理解の方法 (2) - 方法

1. システムコールから読む

2. ブートから読む ( 非推奨 )

3. 本で概要を掴んでから読む

4. テストプログラムをトレース

5. カーネルモジュールを作成

6. カーネルビルド

7. 勉強会に参加

…etc

私は本で概要を掴んでからソースを読んでいます。状況に応じて方法を変えましょう。

10. 1. カーネル理解の方法 (3) - ソースコードを読むコツ

● 読む対象を絞る

テーマを決める

● 全体を把握する

ソースツリー

● 概要を掴んでおく

● データ構造を把握

●

ソースを読みやすくしてくれるツールの利用

GNU GLOBAL,Linux Cross Reference etc...

11. 2. コンピュータアーキテクチャ (1) - 概要

コンピュータ ( 主にハード ) における

基本設計・設計思想などの基本設計概念

● 命令セットアーキテクチャ

RISC 、 CISC 、 VLIW 、 EPIC アーキテクチャ

●

マイクロアーキテクチャ

演算アーキテクチャ、 CPU 制御アーキテクチャ、 CPU 高速化アーキテクチャ

CPU バスアーキテクチャ、マルチプロセッサアーキテクチャ、

マルチスレッドアーキテクチャ

●

システムアーキテクチャ

制御アーキテクチャ、バスアーキテクチャ、メモリアーキテクチャ、

ネットワークアーキテクチャ、オペレーティングシステムアーキテクチャ、

分散処理アーキテクチャ

それぞれの詳細を知っていればカーネルの理解は深く早くなる。

私は、殆ど理解していない。

12. 2. コンピュータアーキテクチャ (2) -

マイクロアーキテクチャ

● マルチプロセッサアーキテクチャ

・ SMP(Symmetric Multiprocessing)

対称型マルチプロセッシング

多くのマルチプロセッサはこの方式

・ NUMA(Non-Uniform Memory Access)

● マルチプロセッサにおいての説明は、

基本的に SMP 前提の説明となっている。

● 今のところ CPU は基本的に SMP だという事を覚えて

おけば、特に意識する必要は無い。

13. 3.CPU のこと (1) - CPU アーキテクチャ

● alpha

●

arm,aarch64,arm26

●

cris

● frv

● h8300

● i386,x86

●

x86_64

●

ia64,itanium64

● m32r

● m68k,m68knommu

● mips

● parisc

● ppc,ppc64

● s390

● sh,sh64

● sparc,sparc64

● um

● v850

● powerpc , power

● avr32 ...etc

コンピュータにおいて、これだけのコンピュータアーキテクチャの組み合わせがある。

14. 3.CPU のこと (2) - x86 のレジスタ

● レジスタ

CPU 内部にある高速なメモリ。メインメモリとは違い、用途

が限られているものが殆ど。

論理回路において、フリップフロップなどにより状態を保持

する装置。

・汎用レジスタ

・セグメントレジスタ

・命令ポインタ

・フラグレジスタ

・制御レジスタ

・メモリ管理レジスタ

・モデル固有レジスタ

・その他レジスタ

デバッグレジスタ、 x87FPU レジスタ、

MMX テクノロジレジスタ、 XMM レジスタ etc...

15. 3.CPU のこと (3) - x86 - 汎用レジスタ

8bit 16bit 32bit 名前 特徴・説明

AH,AL AX EAX Accumulator 汎用レジスタ

BH,BL BX EBX Base メモリアドレスを指定する場合に使用

CH,CL CX ECX Counter

転送や繰り返しの回数を数えるカウンタと

して使用

DL,DL DX EDX Data 汎用レジスタ

SI ESI Source Index

ストリングス命令で移動元のアドレスとし

て使用

DI EDI Destination Index

ストリングス命令で移動先のアドレスとし

て使用

SP ESP Stack Pointer スタックのトップアドレス

BP EBP Base Pointer スタックのベースアドレス

16. 3.CPU のこと (4) - x86 - セグメントレジスタ (1)

● セグメントレジスタ

セグメント ( 領域 ) を指定する為の 16bit のレジスタ

cs,ds,ss,es,fs,gs

● セグメント

可変長のまとまったメモリ空間のこと。

情報の属性などによって分類されたグループのこと。

セグメントに分割して管理する方式をセグメント方式という。

※セグメント方式 - Wikipedia

https://ja.wikipedia.org/wiki/%E3%82%BB%E3%82%B0%E3%83%A1%E3%83%B3%E3%83%88%E6%96%B9%E5%BC%8F

17. 3.CPU のこと (5) - x86 - セグメントレジスタ (2)

16bit 名前 特徴・説明

cs Code Segment

実行コード領域のセグメント

下位 2bit を RPL(Requestor Privilege Level)/ リクエス

タ特権レベルという。

Linux カーネルでは、 CPL(Current Privilege Level)/ 現

行特権レベルとして扱っている。

0 :カーネル 3 :ユーザ

ds Data Segment

データ領域のセグメント。グローバルな静的デ

ータが置かれる。

ss Stack Segment

スタック領域のセグメント。

現在実行中のプログラムのスタック。

es Extra Segment それ以外のセグメント。汎用セグメント。

fs E に続く。汎用セグメント。

gs F に続く。汎用セグメント。

18. 3.CPU のこと (6) - x86 - 命令ポインタ

● 命令ポインタ IP,EIP

次に実行する命令を指し示すポインタ。

( 現在のコードセグメント内 )

・基本的には順番に進められるが、

jmp,call,ret などの命令で色々な場所に移動する。

・ EIP レジスタに直接アクセスすることはできないが、

jmp,call,ret などで、暗黙的に制御することが可能。

16bit 32bit 名前 特徴・説明

IP EIP Instruction

Pointer

次に実行する命令を指し示すポインタ。

現在のコードセグメント内のオフセット

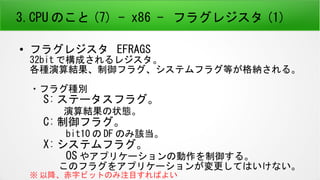

19. 3.CPU のこと (7) - x86 - フラグレジスタ (1)

● フラグレジスタ EFRAGS

32bit で構成されるレジスタ。

各種演算結果、制御フラグ、システムフラグ等が格納される。

・フラグ種別

S: ステータスフラグ。

演算結果の状態。

C: 制御フラグ。

bit10 の DF のみ該当。

X: システムフラグ。

OS やアプリケーションの動作を制御する。

このフラグをアプリケーションが変更してはいけない。

※ 以降、赤字ビットのみ注目すればよい

20. 3.CPU のこと (8) - x86 - フラグレジスタ (2)

bit 種別 flag 名前 説明 関連命令

0 S CF Carry Flag キャリーフラ

グ

MSB で carry( 桁上がり ) か borrow( 桁下が

り ) が生じたときに 1 がセットされる。符号

なし演算の overflow の発生

stc,clc,

cmc

1 1 予約

2 S PF Parity Flag パリティフラ

グ

演算結果の最下位バイトで、値が 1 のビットが

偶数個なら 1 がセットされる

3 0 予約

4 S AF Auxiliary

Carry Flag

補助キャリ

ーフラグ

ビット 3 で carry か borrow が生じた時に 1 がセ

ットされる。 BCD 演算で使用。

5 0 予約

6 S ZF Zero Flag ゼロフラグ 演算結果が 0 のとき 1 がセットされる

7 S SF Sign Flag 符号フラグ 演算結果の MSB がそのままセットされる

8 X TF Trap Flag Debug 用フラグ

1:Single Step Mode が有効 ,0: 無効

9 X IF Interrupt

Enable Flag

割り込み許

可フラグ

1: 割り込み許可 0: 割り込み禁止 sti,cli

21. 3.CPU のこと (9) - x86 - フラグレジスタ (3)

bit 種別 flag 名前 説明 関連命令

10 C DF Direction Flag 方向フラグ ストリング命令を、

1: 上位 ( マイナス ) に向かって処理

0: 下位 ( プラス ) に向かって処理

std,cld

11 S OF Overflow Flag オーバーフ

ローフラグ

計算結果が overflow もしくは underflow した

時に 1 がセットされる

12

X IOPL

I/O Privilege

Level

I/O 特権レ

ベル

現在実行しているプログラム

の I/O 特権レベル13

14 X NT Nested Task

Flag

ビット 3 で carry か borrow が生じた時に 1 が

セットされる。 BCD 演算で使用。

15 0 予約

16 X RF Resume Flag

17 X VM Virtual-8086

Mode

仮想 8086 モ

ード

18 X AC Alignment

Check

アラインメ

ントチェッ

ク

1: アラインメントチェック有効

CPL=3 のときアラインメントチェック例外を

発生させる事が出来る

22. 3.CPU のこと (10) - x86 - フラグレジスタ (4)

bit 種別 flag 名前 説明 関連命令

19 X VIF Virtual

Interrupt Flag

20 X VIP Virtual

Interrupt

Pending

21 X ID Identification

Flag

識別フラグ このビットを変更出来れば、 CPUID 命令を

実行できる

22~

31

予約

23. 3.CPU のこと (11) - x86 - 制御レジスタ (1)

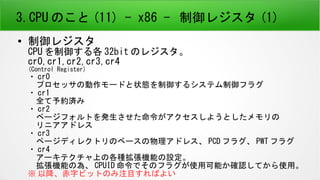

● 制御レジスタ

CPU を制御する各 32bit のレジスタ。

cr0,cr1,cr2,cr3,cr4

(Control Register)

・ cr0

プロセッサの動作モードと状態を制御するシステム制御フラグ

・ cr1

全て予約済み

・ cr2

ページフォルトを発生させた命令がアクセスしようとしたメモリの

リニアアドレス

・ cr3

ページディレクトリのベースの物理アドレス、 PCD フラグ、 PWT フラグ

・ cr4

アーキテクチャ上の各種拡張機能の設定。

拡張機能の為、 CPUID 命令でそのフラグが使用可能か確認してから使用。

※ 以降、赤字ビットのみ注目すればよい

24. 3.CPU のこと (12) - x86 – 制御レジスタ (2) – cr0 (1)

bit flag 名前 説明

0 PE Protect Enable 1: 保護モード 0: 実アドレスモード

1 MP Monitor Coprocesser WAIT( または FWAIT) 命令と TS フラグ (cr0 の bit3) との相互作用を制御する

MP=1 & TS=1 ⇒ WAIT 命令はデバイス使用不可能例外を生成

MP=0 ⇒ WAIT 命令は TS フラグの設定を無視

2 EM Emulation 1: プロセッサは内部または外部の FPU を持っていない

0:FPU を持っている

EM=1 の時に浮動小数点命令を実行すると、デバイス使用不可能例外が発生

3 TS Task Switch FPU が新しいタスクによって実際にアクセスされるまで、タスク切り替え時の FPU コ

ンテキストの保存を遅延させることができる

TS=1 ⇒ 浮動小数点命令の実行前に、デバイス使用不可能例外が発生

TS=1 & MP=1 ⇒ 浮動小数点命令または WAIT/FWAIT 命令の実行前に、

デバイス使用不可能例外が発生

4 ET Extension Type 拡張タイプ。最近の CPU では 1 で予約されている。

5 NE Numerical Error 1:FPU エラーをレポートする為の標準メカニズム Enable

0:PC スタイルの FPU エラーレポートメカニズム Enable

25. 3.CPU のこと (13) - x86 – 制御レジスタ (3) – cr0 (2)

bit flag 名前 説明

6~15 予約

16 WP Write Protect 1: 特権レベルプロシージャのユーザレベル読み取り専用ページへの書込み禁止

0: 許可

Unix 系 OS で使用され、コピーオンライト方式による新しいプロセス生成の際のフ

ォークを簡単にする。

17 予約

18 AM Alignment Mask AM=1 & EFLAGS:AC=1 ⇒ アラインメントチェック有効

CPL=3 のときアラインメントチェック例外を

発生させる事が出来る

19~28 予約

29 NW Not Write Through NW=0 & CD=0 ⇒ キャッシュをヒットする書込みに対してライトバックまたはライト

スルーが有効になり、無効かサイクルが有効になる

30 CD Cash Disable CD=0 & NW=0 ⇒ プロセッサの内部 ( および外部 ) キャッシュにある物理メ

モリ全体のメモリ一のキャッシングを有効

31 PG Paging 1: ページング有効

0: 無効。全てのリニアアドレスを物理アドレスとして扱う。

※cr0:PE=0 ⇒ PG フラグは無効

26. 3.CPU のこと (14) - x86 – 制御レジスタ (4) – cr3

bit flag 名前 説明

0~2 予約

3 PWT Page Write Through 現在のページディレクトリのライトスルー / ライトバックキャッシュポリシーを制御

1: ライトスルーキャッシング有効

0: ライトバックキャッシング有効

内部キャッシュ ( 存在するなら L1,L2 の両方 ) だけに影響を与える。

cr0:PG=0 or cr0:CD=1 ⇒ PWT フラグは無効

4 PCD Page level Cache

Disable

現在のページディレクトリのキャッシングを制御

1: ページディレクトリのキャッシングが抑制される

0: ページディレクトリをキャッシュできる

内部キャッシュ ( 存在するなら L1,L2 の両方 ) だけに影響を与える。

Cr0:PG=0 or cr0:CD=1 ⇒ PCD フラグは無効

5~11 予約

12~31 Page Directory Base ページング機能を ON にする前に、ページディレクトリテーブルのアドレスの

上位 20bit をセット

27. 3.CPU のこと (15) - x86 – 制御レジスタ (5) – cr4

bit flag 名前 説明

0 VME 仮想 8086 モード拡張

1 PVI 保護モード仮想割り込み

2 TSD タイムスタンプディスエーブル

3 DE デバッグ拡張

4 PSE Paging Size Extensions 1:4MB ページ 0:4KB ページ

5 PAE Physical Address

Extensions

1:36bit 物理アドレスを参照するページングメカニズムが有効

0:32bit 物理アドレス

6 MCE マシンチェックイネーブル

7 PGE ページグローバルイネーブル

8 PCE 性能モニタリングカウンタ

イネーブル

9 OSFXSR

10 OSXMME

XCPT

11~31 予約

28. 3.CPU のこと (16) - x86 – メモリ管理レジスタ (1)

●

グローバルディスクリプタテーブルレジスタ gdtr

メインメモリ上のグローバルディスクリプタテーブル (GDT) のアドレス、大きさ。

48bit(6byte) 。

lgdt アセンブリ命令で値をセットする。

●

ローカルディスクリプタテーブルレジスタ ldtr

現在使用しているローカルディスクリプタテーブル (LDT) のアドレス、大きさ。

48bit(6byte)

lldt アセンブリ命令で値をセットする。

bit 内容

47~16 GDT のベースアドレス

15~0 GDT のリミット

bit 内容

47~16 LDT のベースアドレス

15~0 LDT のリミット

29. 3.CPU のこと (17) - x86 – メモリ管理レジスタ (2)

●

割り込みディスクリプタテーブルレジスタ idtr

割り込みディスクリプタテーブル (IDT) のアドレス、大きさ。

48bit(6byte) 。

lidt アセンブリ命令で値をセットする。

●

タスクレジスタ tr

現行タスクの TSS の 32bit のアドレス、大きさ。

48bit(6byte)

ltr アセンブリ命令で値をセットする。

bit 内容

47~16 IDT のベースアドレス

15~0 IDT のリミット

bit 内容

47~16 TSS のベースアドレス

15~0 TSS のリミット

30. 3.CPU のこと (18) - x86 – モデル固有レジスタ

●

モデル固有レジスタ (MSR:Model Specific Register)

アドレス番号でアクセスできる 64bit レジスタ。

読み込み

ECX レジスタにアドレスを設定して rdmsr 命令を実行すると、

結果が EDX と EAX レジスタに読み込まれる。

書き込み

ECX レジスタにアドレスを設定して、 EDX と EAX レジスタにデータを設定し、

wrmsr 命令を実行すると、 MSR に書き込まれる。

アドレス 用途

0xC0000080 拡張イネーブルレジスタ (EFER)

0xC0000081 システムターゲット・アドレスレジスタ (STAR)

0xC0000082 ロング STAR(LSTAR)

0xC0000083 互換 STAR(CSTAR)

31. 3.CPU のこと (19) - x86 - その他レジスタ

●

デバッグレジスタ dr0~dr7

プロセッサのデバッグ動作の監視機能を制御

●

x87FPU レジスタ

浮動小数点データレジスタ (80bit)×8 個、

コントロールレジスタ (16bit) 、ステータスレジスタ (16bit) 、

タグレジスタ (16bit) 、オペコードレジスタ (11bit) 、

FPU 命令ポインタレジスタ (48bit) 、

FPU オペランド ( データ ) ポインタレジスタ (48bit)

●

MMX テクノロジレジスタ

64bit の SIMD(Single Instruction,Multiple Data) 演算をサポートするレジスタ。

64bit レジスタ ×8 個。

●

XMM レジスタ

128bit の SIMD 演算をサポートするレジスタ。

128bit レジスタ ×8 個、 MXCSR レジスタ (32bit)

32. 3.CPU のこと (20) - x86 - 動作モード (1)

IA-32 モード

リアルモード

プロテクトモード

仮想 8086 モード

IA-32e モード

64bit モード

互換モード

PC 起動直後

33. 3.CPU のこと (21) - x86 – 動作モード (2)IA-32 モード

●

リアルモード

・ 8086(16bitCPU) 用に書かれたプログラムを実行させる為のモード。

・完全な上位互換。

・ PC/AT 互換機は、電源投入後やリセット後はリアルモードで動作。

・メモリ空間は、 20bit で (16bit ではない ) 表現できる 0x00000~0xFFFFF=1MB

8086 はアドレスバスが A0~A19 の 20 本ある。

・ 8086 は、アクセス違反を保護する機能が存在しない。

・レジスタは 16bit なのに 20bit のメモリ空間を利用できるカラクリ

アドレス変換器は、セグメントベースを 16 倍してオフセットを足す事で 20bit リニアアドレスを算出。

リニアアドレス=セグメントベース :0x2222 × 0x10+ オフセット :0x1111

=セグメントベース :0x2222 << 4 + オフセット :0x1111

= 0010 0010 0010 0010 << 4 + 0001 0001 0001 0001

= 0010 0010 0010 0010 0000 + 0001 0001 0001 0001

= 0010 0011 0011 0011 0001 (20bit 幅 )

= 0x23331

・ 80286 以降の CPU では、特別な操作をすると上位のハイメモリ領域 (~0x10FFEF)

までもアクセス可能。しかしそれに対応したプログラムが必要。

・ブートローダは最初はリアルモードで動き、途中でプロテクトモードに切り替える。

・ファームウェアアップデートが MS-DOS でしか動かなかったり、まだ活躍の場あり。

※PC/AT 互換機 :https://ja.wikipedia.org/wiki/PC/AT%E4%BA%92%E6%8F%9B%E6%A9%9F

34. 3.CPU のこと (22) - x86 – 動作モード (3)IA-32 モード

●

プロテクトモード

・メモリ管理、タスク管理、保護機能など、 80386(32bitCPU) で拡張された機能を

利用する為のモード。

・メモリ空間は、 32bit で表現できる 0x00000000~0xFFFFFFFF=4GB

80386 はアドレスバス 32 本。

・アドレス変換、割り込み処理手順などリアルモードと全く異なる。

・メモリ、 I/O デバイスへのアクセス保護機能が常に働く。

アクセス違反で割り込み発生。

・ページング機能、アドレス変換機能

⇒仮想的に連続したメモリ空間や他のプログラムから独立したメモリ空間を提供

・ページング機能を応用すると、仮想記憶の実現も可能。

●

仮想 8086 モード

・プロテクトモードのメモリ管理や保護機能を働かせたまま、 8086 用プログラムが実行で

きる互換環境を提供。

・アクセス違反で割り込み発生。

・ハードウェア割り込みや BIOS サービスを利用するソフトウェア割り込みは、 OS がエミュ

レートして結果を 8086 プログラムに返す。

35. 3.CPU のこと (23) - x86 – 動作モード (4)IA-32e モード

●

64bit モード

・プロテクトモードのアドレスサイズを 64bit に拡張。 64bit 空間全ては使えない。

・レジスタ幅 64bit

・ R8~R15 レジスタ追加

・物理アドレスは下位 40bit(1TB) 。 EM64T/x86_64 の規格上の上限は 52bit(1PB) 。

・仮想アドレスは下位 48bit(256TB) 。

上位 16bit は符号拡張 0x00007FFFFFFFFFFF→0xFFFF80000000000 。

規格上の上限は 48bit 。

●

互換モード

・ 64bit モードの中で動くプロテクトモード。

・ 32bit 環境での物理アドレス拡張 PAE もサポート。

36. 3.CPU のこと (24) - x86 – 動作モード (5) 遷移手続き

●

リアルモード → プロテクトモード

● プロテクトモード → リアルモード

● IA-32 モード → IA-32e モード

● IA-32e モード → IA-32 モード

動作モード間の遷移には、手続き / お作法がある。

37. 3.CPU のこと (25) - x86 – 動作モード (6) 遷移手続き

●

リアルモード → プロテクトモード

CR0 レジスタの PE フラグ =1 にする前に色々準備する。

1. GDT の作成

2. gdtr レジスタの設定

3. IDT の作成

4. idtr レジスタの設定

5. A20 マスクの解除

6. CPU への割り込みを禁止

7. CR0 制御レジスタの PE フラグ =1

8. パイプラインの内容をフラッシュ

9. セグメントレジスタの設定

38. 3.CPU のこと (26) - x86 – 動作モード (7) 遷移手続き

●

プロテクトモード → リアルモード

CR0 レジスタの PE フラグ =0 にする前に色々準備する。

1. セグメントレジスタの設定

2. CR0 レジスタの PE フラグ =0

3. パイプラインの内容をフラッシュ

4. セグメントレジスタの再設定

5. A20 マスクの有効化

39. 3.CPU のこと (27) - x86 – 動作モード (8) 遷移手続き

●

IA-32 モード → IA-32e モード

IA-32e のページングは PAE のさらなる拡張の為、事前に PAE を有効化。

CR0 レジスタの PG フラグ =0 にするのは、ページテーブルを変更する為。

( このとき仮想アドレス=物理アドレスにしておく )

1. CR0 レジスタの PG フラグ =0

2. PAE 有効化

3. ページングテーブルをロード

4. IA32_EFER.LME=1 にして、 IA-32e モードを有効化

5. CR0 レジスタの PG フラグ =1

6. 64bit コードセグメントにジャンプ

コードセグメントの内容によって、 64bit モード / 互換モードを判定。

L D 動作モード アドレスサイズ

0 0 互換モード 16bit

0 1 互換モード 32bit

1 0 64bit モード 64bit

1 1 予約 -

40. 3.CPU のこと (28) - x86 – 動作モード (9) 遷移手続き

●

IA-32e モード → IA-32 モード

1. CR0 レジスタの PG フラグ =0

2. ページングテーブルをロード

3. IA32_EFER.LME=0 にして、 IA-32e モードを無効化

4. CR0 レジスタの PG フラグ =1

5. 32bit コードセグメントにジャンプ

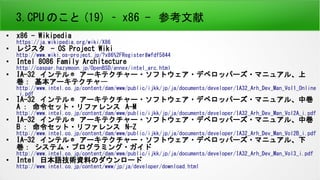

41. 3.CPU のこと (29) – x86 - 参考文献

●

x86 - Wikipedia

https://ja.wikipedia.org/wiki/X86

●

レジスタ - OS Project Wiki

http://www.wiki.os-project.jp/?x86%2FRegister#wfdf5844

●

Intel 8086 Family Architecture

http://caspar.hazymoon.jp/OpenBSD/annex/intel_arc.html

●

IA-32 インテル ® アーキテクチャー・ソフトウェア・デベロッパーズ・マニュアル、上

巻: 基本アーキテクチャー

http://www.intel.co.jp/content/dam/www/public/ijkk/jp/ja/documents/developer/IA32_Arh_Dev_Man_Vol1_Online

_i.pdf

●

IA-32 インテル ® アーキテクチャー・ソフトウェア・デベロッパーズ・マニュアル、中巻

A : 命令セット・リファレンス A-M

http://www.intel.co.jp/content/dam/www/public/ijkk/jp/ja/documents/developer/IA32_Arh_Dev_Man_Vol2A_i.pdf

●

IA-32 インテル ® アーキテクチャー・ソフトウェア・デベロッパーズ・マニュアル、中巻

B : 命令セット・リファレンス N-Z

http://www.intel.co.jp/content/dam/www/public/ijkk/jp/ja/documents/developer/IA32_Arh_Dev_Man_Vol2B_i.pdf

●

IA-32 インテル ® アーキテクチャー・ソフトウェア・デベロッパーズ・マニュアル、下

巻: システム・プログラミング・ガイド

http://www.intel.co.jp/content/dam/www/public/ijkk/jp/ja/documents/developer/IA32_Arh_Dev_Man_Vol3_i.pdf

●

Intel 日本語技術資料のダウンロード

http://www.intel.co.jp/content/www/jp/ja/developer/download.html

42. 4. マザーボードの構成 (1) - 構成部品

・チップセット

・ CPU ソケット

・メモリソケット

・バッテリー

・ ATX 電源コネクタ

・スピーカー

・ IDE コネクタ /SATA コネクタ

・ PCI スロット

・ PCI Express スロット

・イーサネット端子

・ IEEE 1394 ポート

・ IDE( パラレル、シリアル )

・オーディオ端子

・ USB ポート

※ レガシーデバイス

PS/2 コネクタ、シリアルポート、パラレルポート

ISA スロット、 AGP スロット

43. 44. 4. マザーボードの構成 (3) - チップセット (1)

● チップセット

ある機能を実現するのに、複数の集積回路 (IC )を組み合わ

せて機能を実現する構成の場合、それら一連の関連のある複

数の集積回路のこと

CPU 周辺 IC と複数の汎用 IC の組合せを LSI 化したもの。

・ 2 チップ構成が主流

ノースブリッジ、サウスブリッジ

( 開発サイクルや発熱・歩留りを考慮

45. 4. マザーボードの構成 (4) - チップセット (2)

・ノースブリッジ

・ CPU インターフェイス

・メモリインターフェイス

・グラフィックインターフェイス (AGP,PCI-Express)

( ・ GPU)

※以前はメモリコントローラも内蔵していたが、

CPU にメモリコントローラを内蔵する傾向に

・サウスブリッジ

・ PCI

・ IDE

・ Ethernet

etc...

46. 4. マザーボードの構成 (4) - チップセット (3)

・ワンチップセット

ノースブリッジとサウスブリッジを一つにまとめたチップセット。

SoC(System on a Chip)

・統合チップセット

ノースブリッジにグラフィックス機能を統合したチップセット。

グラフィックス統合チップセット / オンボードグラフィックス。

47.

![カーネル参考文献

< 参考書 >

~基本的に古い情報だが、基本は学べる~

・詳解 LINUX カーネル 第 3 版 (O'REILLY

・ Linux カーネル 2.6 解読室 (Softbank Creative

・ Linux カーネル解析入門 ( 工学社

・ Modern Operating Systems 3e International

(Pearson,Andrew S.Tanenbaum)

~初期化部分を知りたいなら~

・新装改訂版 Linux のブートプロセスを見る

(KADOKAWA/ アスキー・メディアワークス )

< 参考 Web>

・ Linux Cross Reference[http://lxr.free-electrons.com]

最新カーネルのソースコードをブラウザで読める。](https://image.slidesharecdn.com/0linux-160107185730/85/0-Linux-6-320.jpg)