Mc cap 7

- 1. 7. FAMILIA DE PROCESOARE “ARM”

7.1. ARM – caracteristici generale

Primul procesor ARM a fost dezvoltat de Acorn Computers Limited, Cambridge, England, 1983 – 1985:

Acorn RISC Machine.

A devenit ulterior acronimul de la Advanced RISC Machine.

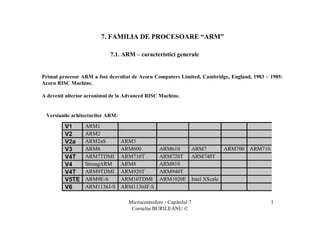

Versiunile arhitecturilor ARM:

V1

V2

V2a

V3

V4T

V4

V4T

V5TE

V6

ARM1

ARM2

ARM2aS

ARM6

ARM7TDMI

StrongARM

ARM9TDMI

ARM9E-S

ARM1136J-S

ARM3

ARM600

ARM710T

ARM8

ARM920T

ARM10TDMI

ARM1136JF-S

ARM610

ARM7

ARM700 ARM710

ARM720T ARM740T

ARM810

ARM940T

ARM1020E Intel XScale

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

1

- 2. Compara ie cu predecesoarele RISC Berkeley RISC I i II i Stanford MIPS:

ş

ş

Asem n ri:

Acces în memorie cu instruc iuni LOAD – STORE

•

Instruc iuni cu format fix pe 32 de bi i

•

Prelucrarea datelor f r acumulator dedicat

•

Pu ine moduri de adresare

•

ă ă

ă ă

Deosebiri :

Setul de lucru de registre nu este de 32 de registre i nu exist ferestre de registre

•

Instruc iunile nu dureaz toate o singur stare

•

Nu se folose te tehnica întârzierii salturilor pentru a preveni blocarea Unit ii de control

•

ă

ş

ă

ă

ă

ş

De fapt, ARM este o combina ie CISC – RISC. Setul de instruc iuni are caracteristici CISC

mai mult decât RISC

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

2

- 3. 7.2. ARM – modurile de lucru

usr

Utilizator

Modul normal de execu ie a programelor

Moduri privilegiate:

sys

Ruleaz procese ale sistemului de operare

ă

Sistem

Moduri care trateaz excep ii:

ă

R spuns rapid la întreruperi

fiq

transfer rapid de date

R spuns normal la întreruperi

irq

r spuns normal la cereri de întreruperi

Supervizor

svc

mod protejat pentru sistemul de operare

Abort

abt

implementeaz mecanismul de protec ie în

memoria virtual

Nedefinit

und

emulare soft a coprocesoarelor hardware

ă

ă

ă

ă

ă

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

3

- 4. 7.3. ARM – Setul de registre

Cele mai multe registre sunt nededicate (multifunc ionale).

Sunt registre pe 32 de bi i .

Un procesor ARM are în total 37 de registre fizice distincte:

- 31 de „registre generale” incluzând num r torul de program;

ă ă

- 6 registre de stare.

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

4

- 5. Modurile de lucru

Moduri privilegiate

Moduri care trateaz excep ii

ă

Utilizator

Sistem

Supervizor

Abort

Nedefinit

Întreruperi

Într. rapide

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

PC

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

PC

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13_svc

R14_svc

PC

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13_abt

R14_abt

PC

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13_und

R14_und

PC

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13_irq

R14_irq

PC

R0

R1

R2

R3

R4

R5

R6

R7

R8_fiq

R9_fiq

R10_fiq

R11_fiq

R12_fiq

R13_fiq

R14_fiq

PC

CPSR

CPSR

CPSR

SPSR_irq

CPSR

SPSR_fiq

CPSR

CPSR

CPSR

SPSR_svc SPSR_abt SPSR_und

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

5

- 6. R0 – R7

sunt registre fizice.

(8)

R8 – R14 sunt registre logice – în sensul ca pot fi translatate în registre fizice diferite, astfel:

R8 – R12 pot fi translatate în câte 2 registre fizice;

R13 i R14 pot fi translatate în câte 6 registre fizice.

(10)

(12)

ş

R15

este registru fizic.

(1)

----(31)

CPSR

este registru fizic.

(1)

SPSR

este registru logic ce poate fi translatat în 5 registre fizice.

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

(5)

----(6)

6

- 7. R13:

indicator de stiv nededicat: SP

R14:

„registru de leg tur ”: LR ;

con ine adresa de reîntoarcere din subprograme

ă

ă

ă

MOV

sau

BX

PC, LR

LR

R15 este num r torul de program PC:

• poate fi registru general de date

• când e citit d adresa instruc iunii curente plus 8B

• ultimii 2 bi i sunt zero

• când se scrie în acest registru rezultatul e un salt la adresa înscris în R15;

ultimii 2 bi i trebuie s fie zero

ă ă

ă

ă

ă

CPSR este „registrul de stare al programului curent”. În modurile care trateaz excep ii,

acest registru este trecut în SPSR – “registrul de stare al programului salvat”.

ă

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

7

- 9. Setul de lucru con ine (indiferent de modul de lucru):

- 15 registre generale: R0 – R14;

- 1 num r tor de program: R15 ≡ PC;

ă ă

- 1 sau 2 registre de stare: CPSR i SPSR_mod.

ş

unde mod semnific unul dintre

modurile care trateaz excep ii.

ă

ă

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

9

- 10. 7.4. ARM – Memoria i porturile

ş

Adresare liniar :

AF ≡ adr32

ă

Memoria are 4 GB, sau 2Gw sau 1Gdw; informa iile sunt aliniate

← AF curent + 8 + offset

toare ← AF instr. curent + 4

ă

ă

ă

Adresele instruc iunilor:

• Salturi:

AFsalt

AF instr. urm

• Secven ial:

Se folosesc atât „micul indian” cât i „marele indian”. Nu exist instruc iuni specifice pentru

trecerea de la o conven ie la alta. Exist un terminal de intrare pentru a configura conven ia

care se potrive te cu memoria folosit

ă

ş

ă

ă

ş

Porturile sunt organizate ca loca ii de memorie („memory – mapped I/O”)

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

10

- 11. Moduri de adresare

Adresa pentru accesul în memorie (LOAD / STORE) are 2 p r i:

ă

• registru baz : oricare registru general R0 – R15

în cazul R15 (PC) avem, de fapt, o adresare relativ

ă

ă

• offset (AE):

• imediat: o constant (întreg f r semn) care se adun sau se scade la registrul baz

• registru: un registru general R0 – R14 care se adun sau scade la registrul baz

• registru deplasat: un registru general R0 – R14 care este deplasat cu un num r de celule

indicat printr-o valoare imediat , iar rezultatul se adun sau scade la registrul baz

ă

ă

ă

ă ă

ă

ă

ă

ă

ă

ă

Indiferent de tipul de offset, exist trei moduri de a combina cele 2 entit i:

ă

ă

• offset: cele 2 entit i se adun sau se scad:

AF ← (r) ± AE

ă

ă

• pre-indexare: cele 2 entit i se adun sau se scad; apoi registru baz este actualizat cu

noua adres , ceea ce permite indexarea automat într-un ir:

AF ← (r) ± AE

(r) ← (r) ± AE

ă

ă

ş

ă

ă

ă

• post-indexare: se folose te doar registrul baz pentru adresare; apoi registru baz este

actualizat cu cele 2 entit i se adun sau se scad, ceea ce permite indexarea automat într-un ir:

AF ← (r)

(r) ← (r) ± AE

ă

ş

ă

ă

ş

ă

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

11

ă

- 12. 7.5. ARM – Setul de instruc iuni

7.5.1. Condi ionarea execu iei instruc iunilor

Aproape toate instruc iunile ARM sunt, de fapt, decizii simple: sunt testate fanioanele N, Z, C, V

din CPSR i dac este îndeplinit condi ia, instruc iunile se desf oar normal

ă

şă

ă

ă

ş

Instruc iunile con in în format un câmp de 4 bi i [31:28] care codific condi ia testat

ă

Mnemonic

Semnifica ie

Fanion testat

EQ

NE

CS/HS

CC/LO

MI

PL

VS

VC

HI

LS

GE

LT

GT

LE

AL

NV

Egal

Non-egal

Mai mare sau egal, numere f r semn

Mai mic, numere f r semn

Negativ (minus)

Pozitiv sau zero (plus)

Dep ire

Non-dep ire

Mai mare, numere f r semn

Mai mic sau egal, numere f r semn

Mai mare sau egal, numere cu semn

Mai mic, numere cu semn

Mai mare, numere cu semn

Mai mic sau egal, numere cu semn

Necondi ionat

Rezervat pentru instr. suplimentare

ă

(Z) ← 1

(Z) ← 0

(C) ← 1

(C) ← 0

(N) ← 1

(N) ← 0

(V) ← 1

(V) ← 0

(C) ← 1 & (Z) ← 0

(C) ← 0 ∀ (Z) ← 1

(N) ← 1 & (V) ← 1

(N) ← 1 & (V) ← 0

(N) ← 0 & (V) ← 0

(N) ← 0 & (V) ← 1

-

ă ă

ă ă

şă

şă

ă ă

ă ă

Format

[31:28]

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

12

- 13. 7.5.2. Salturi

Salturi propriu-zise în ecartul a 32 MB

Pot fi realizate i prin înscrierea unei valori în R15 ≡ PC

ş

Apelul de subprograme cu instruc iuni similare („Branch with Link”) tot în ecartul a 32 MB

Adresa de revenire va fi în R14 ≡ LR

„Branch and Exchange”:

(PC) ← (r)

if (PC)0 ≡ 1 se trece în setul de instruc iuni Thumb

Înc rcarea a 4 octe i direct în R15 ≡ PC echivaleaz cu un salt lung în toat memoria de 4 GB

Dac în prealabil (LR) ← (PC) se genereaz un apel de subprogram în toat memoria de 4 GB

ă

ă

ă

ă

ă

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

13

ă

- 14. Salturi condi ionate:

necondi ionat

Întotdeauna

Egal

Non-egal

Plus

Minus

Salt dac transport e 0

Mai mic (f r semn)

Salt dac transport e 1

Mai mare sau egal (f r semn)

Salt dac dep ire e 0

Salt dac dep ire e 1

Mai mare (cu semn)

Mai mare sau egal (cu semn)

Mai mic (cu semn)

Mai mic sau egal (cu semn)

Mai mare (f r semn)

Mai mic (f r semn)

ă

ă ă

ă

ă ă

ă

şă

ă

şă

ă ă

ă ă

B

BAL

BEQ

BNE

BPL

BMI

BCC

BLO

BCS

BHS

BVC

BVS

BGT

BGE

BLT

BLE

BHI

BLS

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

14

- 15. Exemple:

B

eticheta

; salt la eticheta

BCC eticheta

; salt condi ionat de (C) ← 0

BEQ eticheta

; salt condi ionat de (Z) ← 1

MOV PC,#0

; (R15) ← 0

BL

; apel de procedur

ă

proc

MOV PC,LR

; (R15) ← (R14)

;return

MOV LR,PC

; (R14) ← (R15)

;gata pentru return

LDR PC,=proc

; (R15) ← adr(proc)

;încarc o adres pe 32 bi i în

;num r torul de program

ă

ă

ă ă

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

15

- 16. 7.5.3. Prelucr ri de date

ă

To i operanzii sunt pe 32 bi i

Rezultatul este pe 32 bi i i va fi un registru

ş

Nu exist acumulator; registrele pentru operanzi i rezultat sunt separate

ş

ă

AND

EOR

SUB

RSB

ADD

ADC

SBC

RSC

TST

TEQ

CMP

CMN

ORR

MOV

BIC

MVN

(d) ← (s) & operand

(d) ← (s) ⊕ operand

(d) ← (s) - operand

(d) ← operand - (s)

(d) ← (s) + operand

(d) ← (s) + operand + (C)

(d) ← (s) – operand – NOT(C)

(d) ← operand - (s) – NOT(C)

(s) & operand

(s) ⊕ operand

(s) - operand

(s) + operand

(d) ← (s) ∀ operand

(d) ← (s)

(d) ← (s) & NOToperand

(d) ← NOT(s)

în care:

• (d) i (s) sunt registre generale

• operand este o valoare imediat sau un registru general care poate fi i deplasat

ş

ş

ă

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

16

- 17. Deplas ri:

ă

LSL

deplasare logic stânga

LSR

deplasare logic dreapta

ASL

deplasare aritmetic stânga

ASR

deplasare aritmetic dreapta

ROR

rota ie dreapta

RRX

rota ie dreapta o pozi ie folosind C

ă

ă

ă

ă

Setarea fanioanelor se face op ional (cu excep ia compara iilor) se face indicând în asamblor

un „S” la mnemonic ; de exemplu ADDS

ă

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

17

- 18. 7.5.4. Înmul iri

Dou clase de înmul iri:

• 32 ← 32 * 32

• 64 ← 32 * 32

ă

operanzii sunt în 2 registre generale, rezultatul este trunchiat la 32 bi i i stocat în alt registru

operanzii sunt în 2 registre generale, se adun con inutul uni al treilea registru, rezultatul este

trunchiat la 32 bi i i stocat în al patrulea registru „înmul ire cu acumulare”)

ş

ă

Înmul ire „normal ”:

• MUL

• MLA

ă

ş

ă ă

ă

ş

ă

ş

ş

ă ă

• UMLAL

ş

• SMLAL

ş

ă

• UMULL

operanzii sunt în 2 registre generale i rezultatul, pe 64 bi i este stocat

în alte 2 registre concatenate; numerele sunt întregi cu semn

operanzii sunt în 2 registre generale i rezultatul, pe 64 bi i este stocat

în alte 2 registre concatenate; numerele sunt întregi f r semn

operanzii sunt în 2 registre generale, la rezultat se adun con inutul

a 2 registre concatenate i rezultatul este stocat în aceste al treilea i al patrulea registru;

numerele sunt întregi cu semn

operanzii sunt în 2 registre generale, la rezultat se adun con inutul

a 2 registre concatenate i rezultatul este stocat în aceste al treilea i al patrulea registru;

numerele sunt întregi f r semn

ş

Înmul ire „lung ”:

• SMULL

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

18

- 19. Exemple:

MUL

R4, R2, R1

; (R4) ← (R2)*(R1)

MLA

R7, R8, R9, R3

; (R7) ← (R8)*(R9) + (R3)

SMULL R4, R8, R2, R3

; (R4)↑(R8) ← (R2)*(R3)

↑

UMULL R6, R8, R0, R1

; (R6)↑(R8) ← (R0)*(R1)

↑

UMLAL R5, R8, R0, R1

; (R5)↑(R8) ← (R0)*(R1) + (R5)↑(R8)

↑

↑

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

19

- 20. 7.5.5. Instruc iuni aritmetice speciale

CLZ

înscrie într-un registru num rul de cifre binare 0 ale unui operand din alt registru,

începând cu msb i pân la primul 1

ă

ă

ş

Determin câte deplas ri stânga sunt necesare pentru normalizarea unui operand

ă

ă

ă

Determin bitul cu prioritatea maxim într-o masc binar

ă

ă

ă

Exemple:

CLZ

R4, R2

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

20

- 21. 7.5.6. Accesul în memorie

Tipuri de instruc iuni LOAD / STORE:

• 8 sau 32 bi i, întregi f r semn

• 16 bi i întregi f r semn, 16 sau 8 bi i, întregi cu semn

ă ă

ă ă

Se folosesc modurile de adresare amintite

LDR

LDRB

LDRH

LDRSB

LDRSH

STR

STRB

SRH

Încarc 32 bi i într-un registru general

Încarc 8 bi i într-un registru general

Încarc 16 bi i (întreg f r semn) într-un registru general

Încarc 8 bi i (întreg cu semn) într-un registru general

Încarc 16 bi i (întreg cu semn) într-un registru general

Memoreaz 32 bi i dintr-un registru de uz general

Memoreaz 8 bi i dintr-un registru de uz general

Memoreaz 16 bi i dintr-un registru de uz general

LDM

STRM

Încarc un subset sau toate registrele generale

Memoreaz un subset sau toate registrele generale

SWP

SWPB

Inter-schimb 32 bi i între registre i memorie

Inter-schimb 8 bi i între registre i memorie

ă

ă

ă ă

ă

ă

ă

ă

ă

ă

ă

ă

ş

ă

ş

ă

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

21

- 22. Exemple:

LDR R1, [R0]

; (R1) ← ((R0))

LDR R8, [R3,#4]

; (R8) ← ((R3) + 4)

LDR R12, [R13,#-4]

; (R12) ← ((R13) - 4)

STR

; ((R1) +100H) ← (R2)

R2, [R1,#0x100]

LDRB R5,[R9]

; (R5) ← 000000 ↑((R9))

LDR R11, [R3,R5,LSL #2]

; (R11) ← ((R3) + (R5)*4)

LDR R1, [R0,#4]!

; (R1) ← ((R0) + 4)

; (R0) ← (R0) + 4

STRB R7, [R6,#-1]!

; ((R6) -1) ← (R7)

; (R6) ← (R6) – 1

LDR R3, [R9], #4

; (R3) ← ((R9))

; (R9) ← (R9)+4

STR R2, [R5],#8

; ((R5)) ← (R2)

; (R5) ← (R5) + 8

LDR R0, [PC,#40]

; (R0) ← ((PC) + 40 + 8)

LDR R0, [R1], R2

; (R0) ← ((R1))

; (R1) ← (R1) + (R2)

SWP R12, R10, [R9]

; (R12) ← ((R9))

; ((R9)) ← (R10)

SWP R1, R1, [R9]

; (R1) ↔ ((R9))

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

22

- 23. 7.5.7. Comunicarea cu coprocesorul

Suport pân la 16 coprocesoare logice

ă

ă

Fiecare coprocesor poate avea pân la 16 registre proprii de m rimi diverse

ă

ă

Coprocesoarele au arhitecturi RISC, cu instruc iuni care

• execut opera ii interne cu registrele

• acceseaz memoria cu LOAD i STORE

• schimb date cu registrele nucleului ARM

ă

ş

ă

ă

Coprocesoarele pot fi ad ugate pe cip sau pe plac .

Cel mai adesea se folosesc coprocesoare pentru gestionarea memoriei i accesul în memoriile cache.

ă

ă

ş

CDP p5, 2, c12, c10, c3, 4

;ini iaz opera ii cu date la coprocesorul 5

;primul byte de cod este 2 iar al doilea byte

;de cod este 4; c12 este registru destina ie

; i c10, c3 sunt registre surs

MRC p15, 5, R4, c0, c2, 3

;transfer date de la coprocesorul 15;

;primul byte de cod este 5 iar al doilea byte

; de cod este 3; R4 este registru destina ie,

; iar c0, c2 sunt registre surs

ă

ă

ş

ă

ă

Microcontrolere - Capitolul 7

Corneliu BURILEANU ©

23