⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 1, 2do Parcial (2020 PAO 1) C4 B

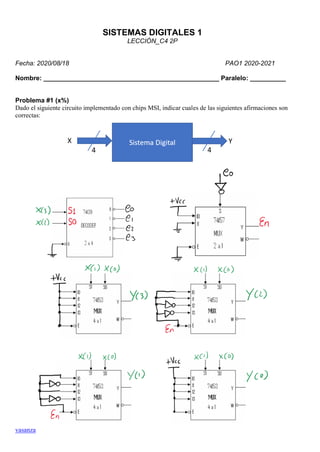

- 1. vasanza SISTEMAS DIGITALES 1 LECCIÓN_C4 2P Fecha: 2020/08/18 PAO1 2020-2021 Nombre: _________________________________________________ Paralelo: __________ Problema #1 (x%) Dado el siguiente circuito implementado con chips MSI, indicar cuales de las siguientes afirmaciones son correctas:

- 2. vasanza a) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 cuando la entrada X es menor que 4. b) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es menor que 4. c) En el sistema digital, la salida Y de 4 bits presenta el valor de X en exceso a 3 (XS3) cuando la entrada X es mayor e igual que 4 y menor que 8. d) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 4 y menor que 8. e) En el sistema digital, la salida Y de 4 bits presenta el valor de X en código GRAY cuando la entrada X es mayor e igual que 8 y menor que 12. f) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 8 y menor que 12. g) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 cuando la entrada X es mayor e igual que 12. h) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 12. i) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 para cualquier valor de X. j) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 para cualquier valor de X. k) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar para cualquier valor presente en la entrada X. Problema #2 (x%) Dado el siguiente circuito implementado con chips MSI, indicar cuales de las siguientes afirmaciones son correctas:

- 3. vasanza a) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 cuando la entrada X es menor que 4. b) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es menor que 4. c) En el sistema digital, la salida Y de 4 bits presenta el valor de X en exceso a 3 (XS3) cuando la entrada X es mayor e igual que 4 y menor que 8. d) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 4 y menor que 8. e) En el sistema digital, la salida Y de 4 bits presenta el valor de X en código GRAY cuando la entrada X es mayor e igual que 8 y menor que 12. f) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 8 y menor que 12. g) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 cuando la entrada X es mayor e igual que 12. h) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 12. i) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 para cualquier valor de X. j) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 para cualquier valor de X. k) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar para cualquier valor presente en la entrada X.

- 4. vasanza Problema #3 (x%) Dado el siguiente circuito implementado con chips MSI, indicar cuales de las siguientes afirmaciones son correctas:

- 5. vasanza a) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 cuando la entrada X es menor que 4. b) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es menor que 4. c) En el sistema digital, la salida Y de 4 bits presenta el valor de X en exceso a 3 (XS3) cuando la entrada X es mayor e igual que 4 y menor que 8. d) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 4 y menor que 8. e) En el sistema digital, la salida Y de 4 bits presenta el valor de X en código GRAY cuando la entrada X es mayor e igual que 8 y menor que 12. f) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 8 y menor que 12. g) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 cuando la entrada X es mayor e igual que 12. h) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 12. i) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 para cualquier valor de X. j) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 para cualquier valor de X. k) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar para cualquier valor presente en la entrada X. Problema #4 (x%) Dado el siguiente circuito implementado con chips MSI, indicar cuales de las siguientes afirmaciones son correctas:

- 6. vasanza a) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 cuando la entrada X es menor que 4. b) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es menor que 4. c) En el sistema digital, la salida Y de 4 bits presenta el valor de X en exceso a 3 (XS3) cuando la entrada X es mayor e igual que 4 y menor que 8. d) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 4 y menor que 8. e) En el sistema digital, la salida Y de 4 bits presenta el valor de X en código GRAY cuando la entrada X es mayor e igual que 8 y menor que 12. f) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 8 y menor que 12. g) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 cuando la entrada X es mayor e igual que 12. h) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 12. i) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 para cualquier valor de X. j) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 para cualquier valor de X. k) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar para cualquier valor presente en la entrada X.

- 7. vasanza Problema #5 (x%) Dado el siguiente circuito implementado con chips MSI, indicar cuales de las siguientes afirmaciones son correctas:

- 8. vasanza a) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 cuando la entrada X es menor que 4. b) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es menor que 4. c) En el sistema digital, la salida Y de 4 bits presenta el valor de X en exceso a 3 (XS3) cuando la entrada X es mayor e igual que 4 y menor que 8. d) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 4 y menor que 8. e) En el sistema digital, la salida Y de 4 bits presenta el valor de X en código GRAY cuando la entrada X es mayor e igual que 8 y menor que 12. f) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 8 y menor que 12. g) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 cuando la entrada X es mayor e igual que 12. h) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 12. i) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 para cualquier valor de X. j) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 para cualquier valor de X. k) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar para cualquier valor presente en la entrada X. Problema #6 (x%) Dado el siguiente circuito implementado con chips MSI, indicar cuales de las siguientes afirmaciones son correctas:

- 9. vasanza a) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 cuando la entrada X es menor que 4. b) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es menor que 4. c) En el sistema digital, la salida Y de 4 bits presenta el valor de X en exceso a 3 (XS3) cuando la entrada X es mayor e igual que 4 y menor que 8. d) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 4 y menor que 8. e) En el sistema digital, la salida Y de 4 bits presenta el valor de X en código GRAY cuando la entrada X es mayor e igual que 8 y menor que 12. f) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 8 y menor que 12. g) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 cuando la entrada X es mayor e igual que 12. h) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar solo cuando la entrada X es mayor e igual que 12. i) En el sistema digital, la salida Y de 4 bits presenta el valor de X dividido para 2 para cualquier valor de X. j) En el sistema digital, la salida Y de 4 bits presenta el valor de X multiplicado por 2 para cualquier valor de X. k) En el sistema digital, los multiplexores conectados a la señal En se logran habilitar para cualquier valor presente en la entrada X.