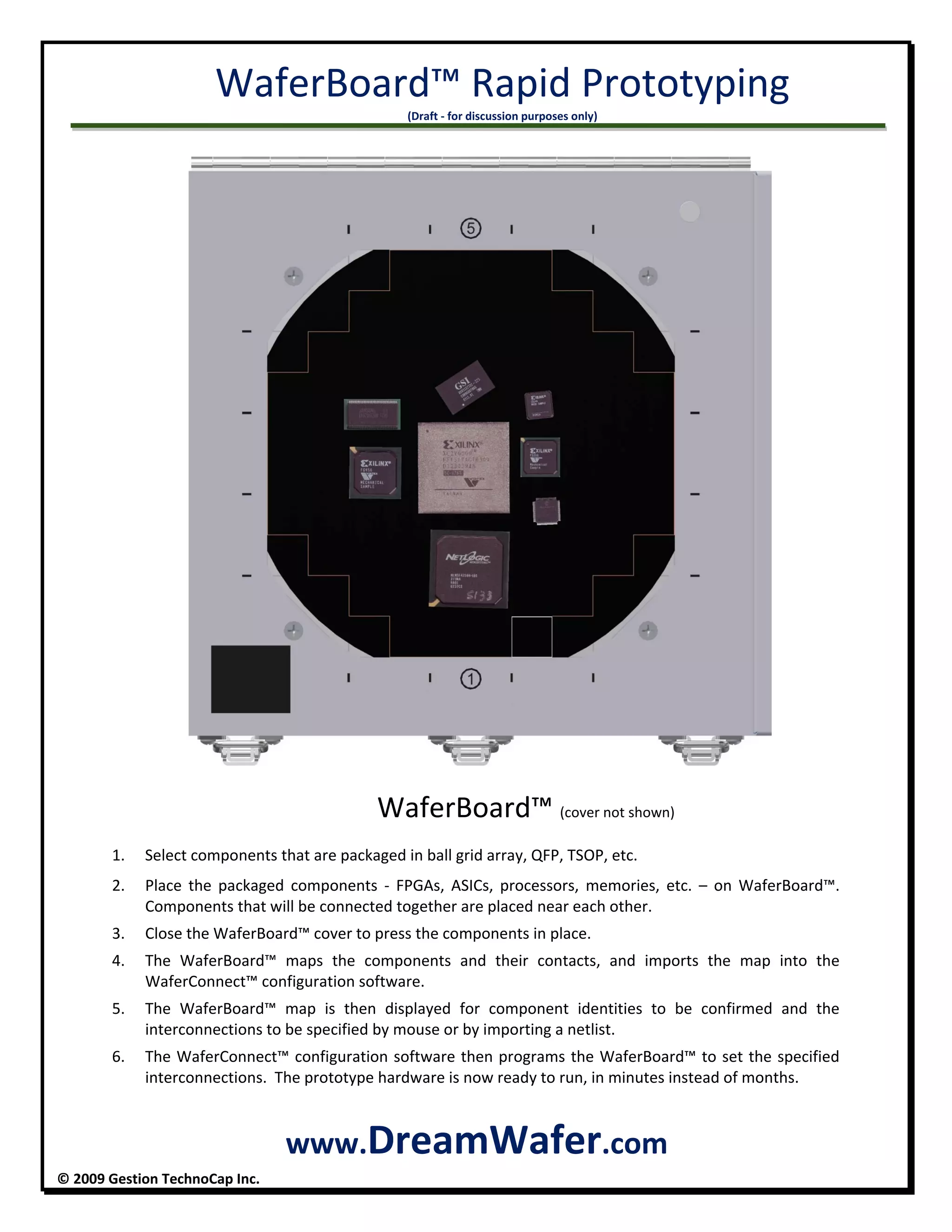

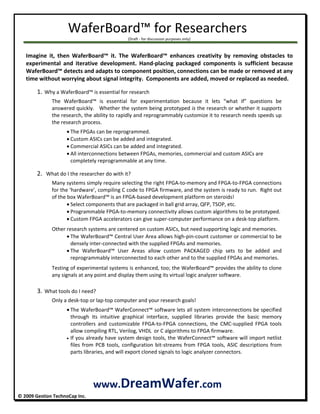

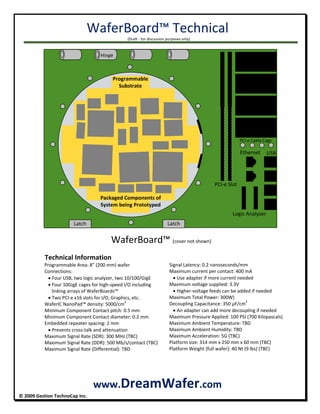

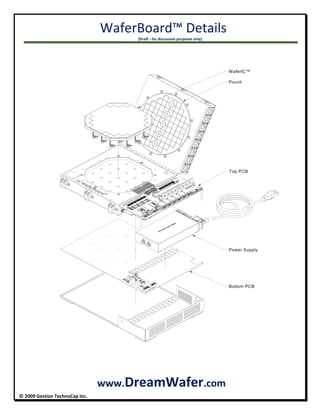

The document describes WaferBoard, a tool for rapidly prototyping electronic systems. It allows components like FPGAs, ASICs, processors and memory to be placed on the WaferBoard and interconnected programmatically through configuration software. This allows prototypes to be created and running in minutes, significantly faster than traditional methods. The WaferBoard maps components, confirms identities, and sets interconnects through software. This enables fast, flexible prototyping of complex electronic systems.