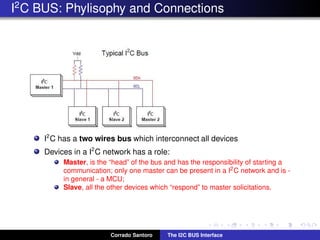

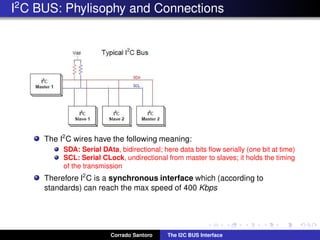

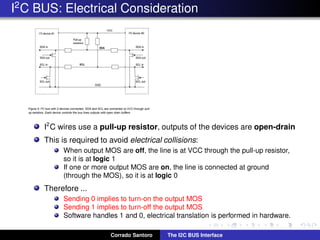

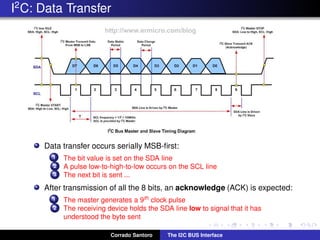

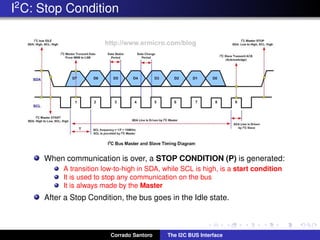

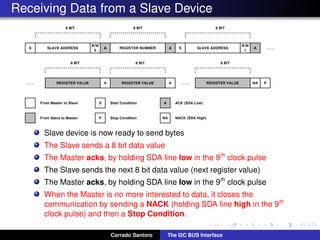

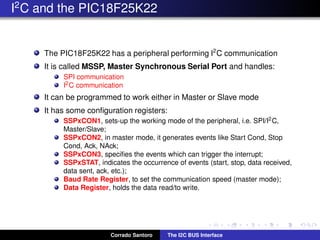

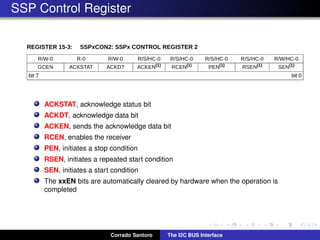

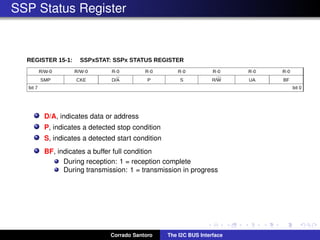

The document describes the I2C (Inter-Integrated Circuit) bus interface. I2C is a digital communication protocol used to connect integrated circuits on the same circuit board. It uses just two bidirectional open-drain lines - serial data (SDA) and serial clock (SCL). Devices on the I2C bus can operate as either a master or slave. The master device initiates and controls data transfers. Slave devices respond to the master's commands. The document outlines the electrical considerations, addressing schemes, data transfer protocols, and how to implement I2C on a PIC18F25K22 microcontroller.